A Fault-Tolerant Routing Method for On-Chip Internetwork Based on Channel Dependency Graph

An on-chip interconnection network and dependency graph technology, applied in data exchange networks, transmission systems, digital transmission systems, etc., can solve problems such as inability to fully play the role of faulty router components and waste of system resources, and achieve good scalability. performance and flexibility, low latency, and improved resource utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention is described in detail below in conjunction with accompanying drawing.

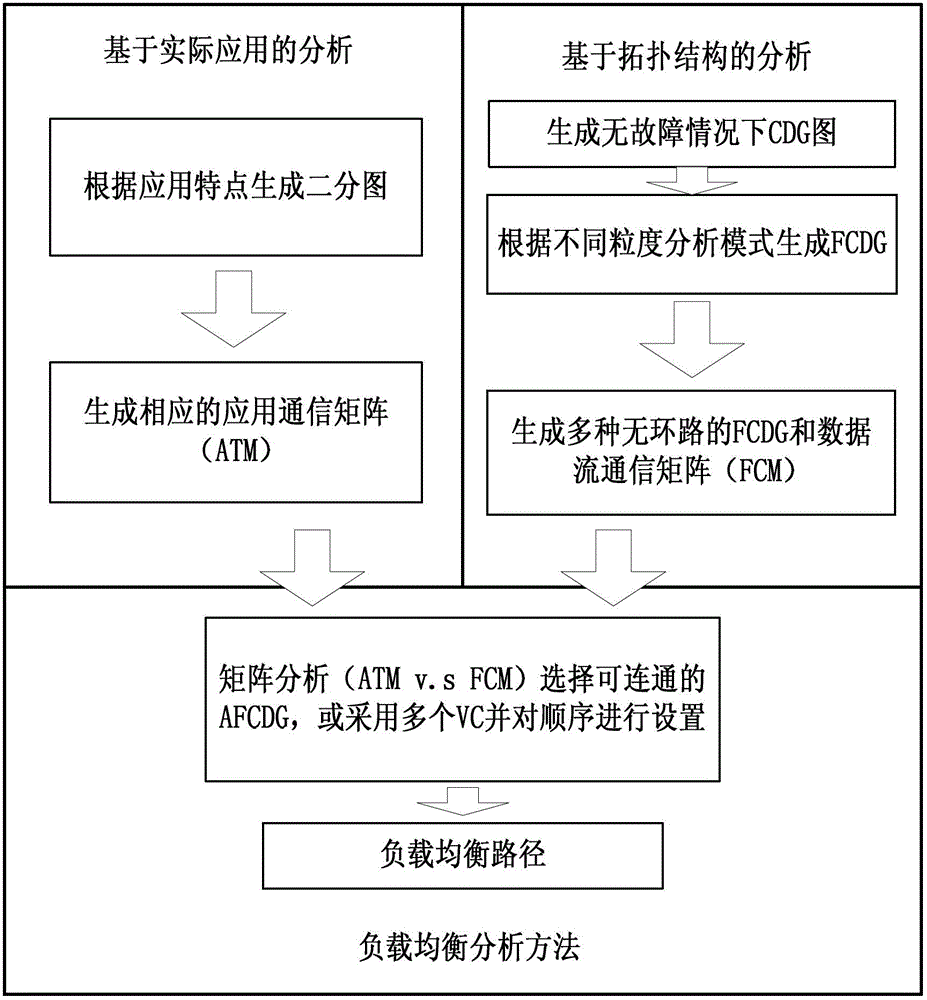

[0032] A fault-tolerant routing method for on-chip Internet based on channel dependency graph, refer to figure 1 , including the following steps:

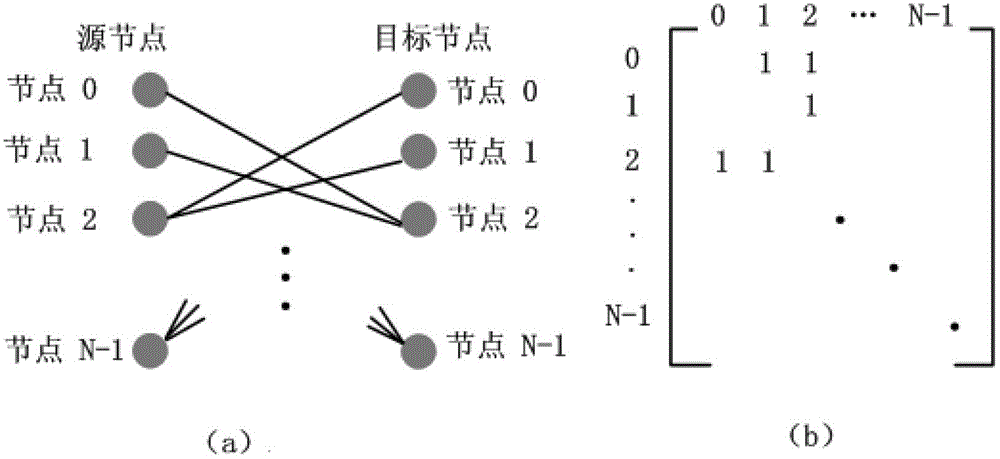

[0033] Step 1. First analyze the communication characteristics of the application modules, analyze whether there are communication requirements between the application modules, and generate a bipartite graph according to whether there are communication requirements between the application modules. Refer to image 3 The application modules in the bipartite graph are listed on both sides of the source node and the target node, and the solid line indicates that there is a communication requirement between the corresponding application modules; and the corresponding application module communication relationship matrix application traffic matrix, referred to as ATM, is generated by the ATM The corresponding bipartite graph of the comm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More