Three-dimensional packaging device for photonic integrated chip matching circuit

A technology of photon integration and matching circuits, applied in circuits, optical multiplexing systems, optics, etc., can solve the problems of increasing circuit design dimensions and matching circuit size limitations, and achieve impedance matching, enhanced heat dissipation, and heat dissipation The effect of area enlargement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

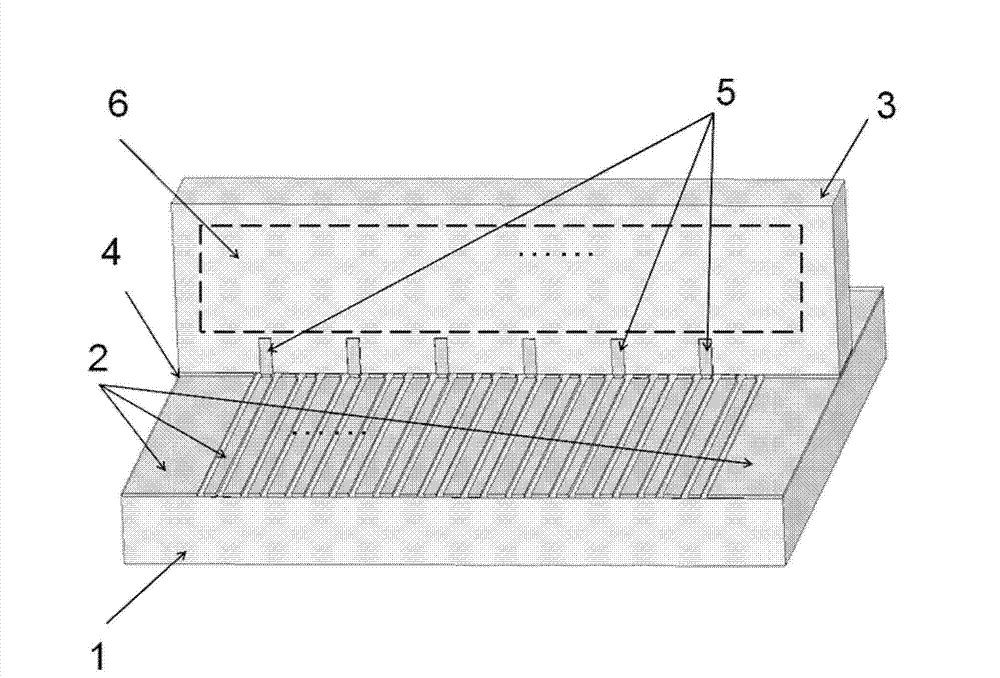

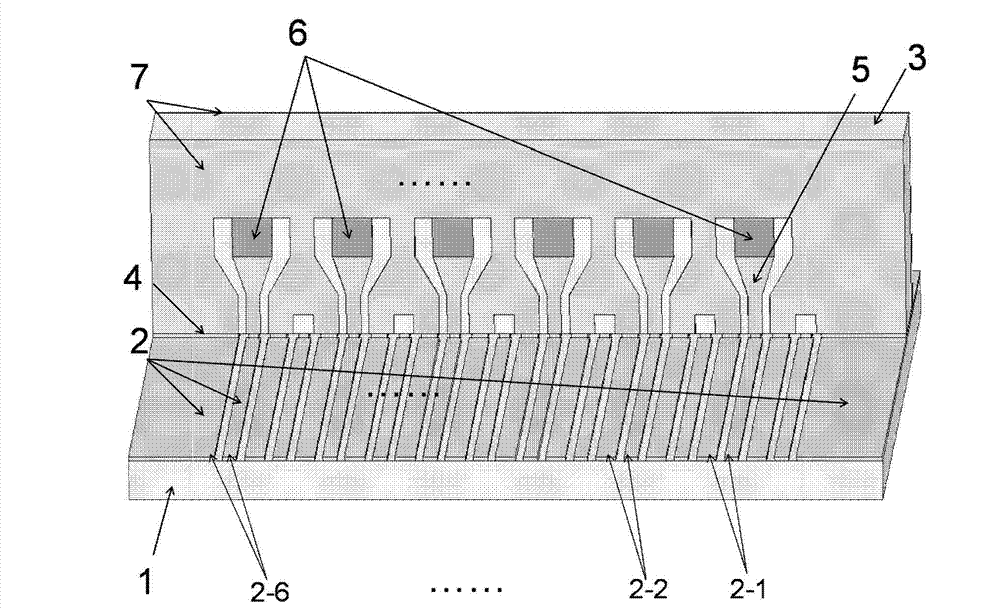

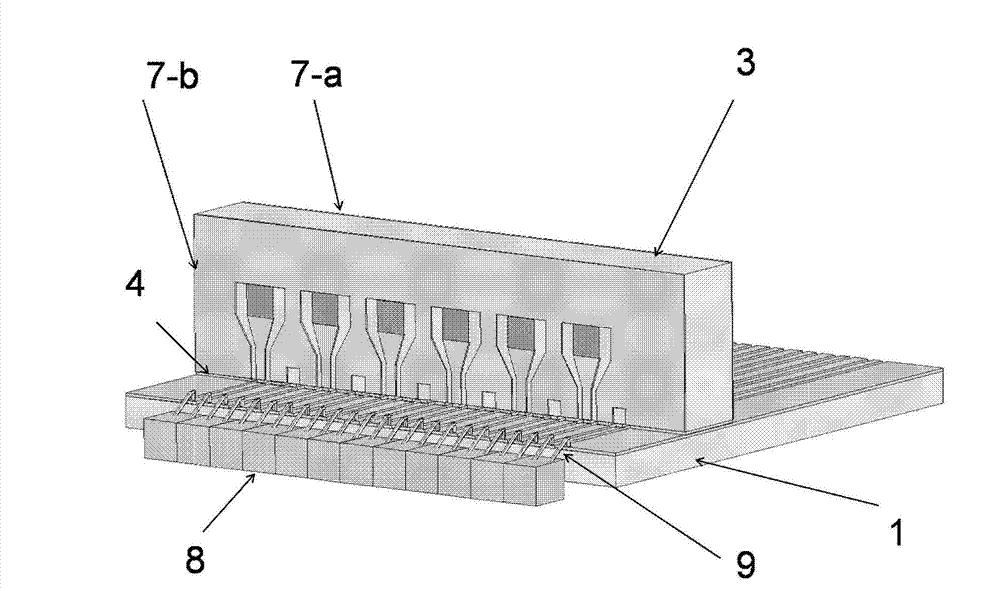

[0033] Such as figure 1 as shown, figure 1 It is a structural schematic diagram of a three-dimensional packaging device for a photonic integrated chip matching circuit provided by the present invention. The device includes: a first carrier substrate 1; a first microwave transmission line array 2 evaporated on the first carrier substrate 1 The surface is used to provide bias voltage and high-frequency modulation signal to the photonic integrated chip; a second carrier substrate 3 is perpendicular to or at a certain angle with the first carrier substrate 1 to form a three-dimensional structure; a second microwave transmission line An array 4 is vapor-deposited on the lower surface of the second carrier substrate 3, and is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More