Low-power-consumption high-reliability electrification resetting circuit

A technology of electrical reset and reliability, applied in the direction of electrical components, electronic switches, pulse technology, etc., can solve the problems of increasing chip cost, unfavorable CMOS integration, etc., to achieve enhanced ability to resist power supply noise, reduce chip area, and ensure reliability sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] specific implementation plan

[0027] The present invention is further described in detail through the embodiments in conjunction with the accompanying drawings

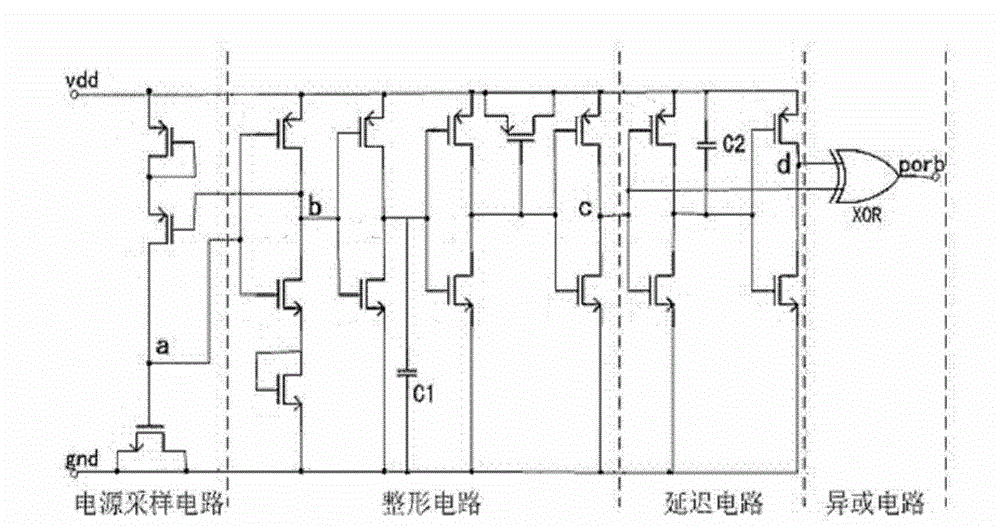

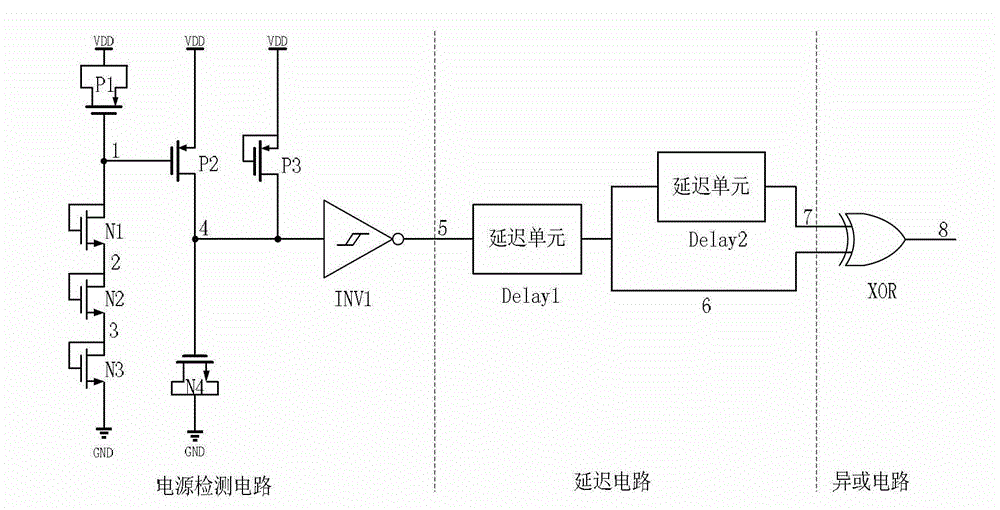

[0028] A low-power and high-reliability power-on reset circuit of the present invention is composed of a power detection circuit, a delay circuit and an XOR circuit, as shown in the attached figure 2 shown. Its specific circuit structure is as follows:

[0029] It is explained here that PMOS transistors and NMOS transistors are indicated by pipe P and pipe N respectively in the following documents and drawings, and the arrangement numbers of pipe P and pipe N are represented by numbers, such as the first PMOS transistor P1, the second PMOS transistor P2, the second PMOS transistor P2, An NMOS transistor N1, a second NMOS transistor N2, etc. are arranged in sequence.

[0030] The power detection circuit includes a PMOS transistor P1, a transistor P2, a transistor P3, an NMOS transistor N1, a transistor N2, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More