MOS device provided with vertical GaAs base structure and fabrication method of MOS device

A MOS device and vertical structure technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as difficult to obtain breakthroughs, achieve the effects of simplifying the manufacturing process, increasing switching speed, and realizing selective corrosion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

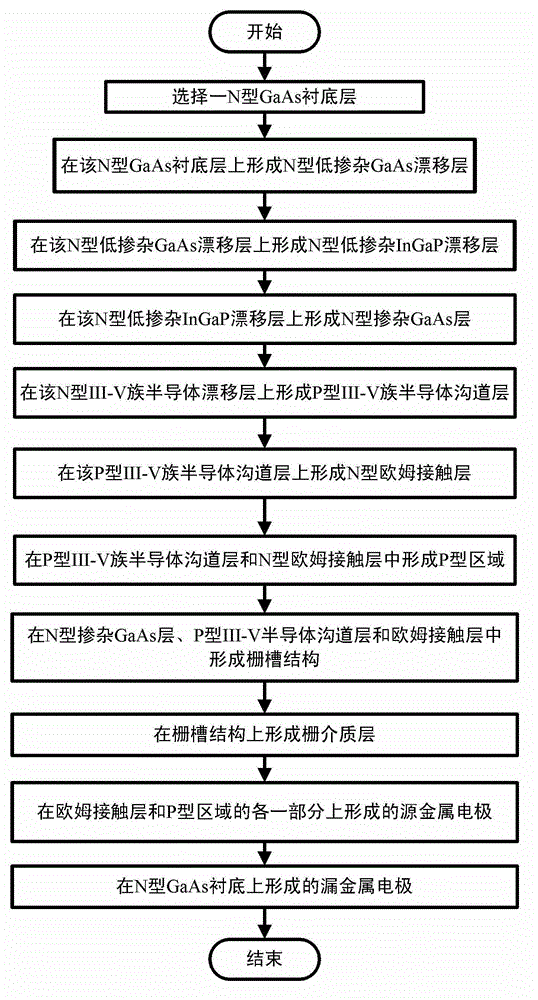

[0026] The GaAs-based vertical structure MOS device and its manufacturing method provided by the present invention reduce the on-resistance of the device by utilizing the high electron mobility characteristics of III-V semiconductor materials; through the design of the InGaP layer, the gate groove is realized. Selective etching in etching, thereby improving the consistency and process stability in the device manufacturing process.

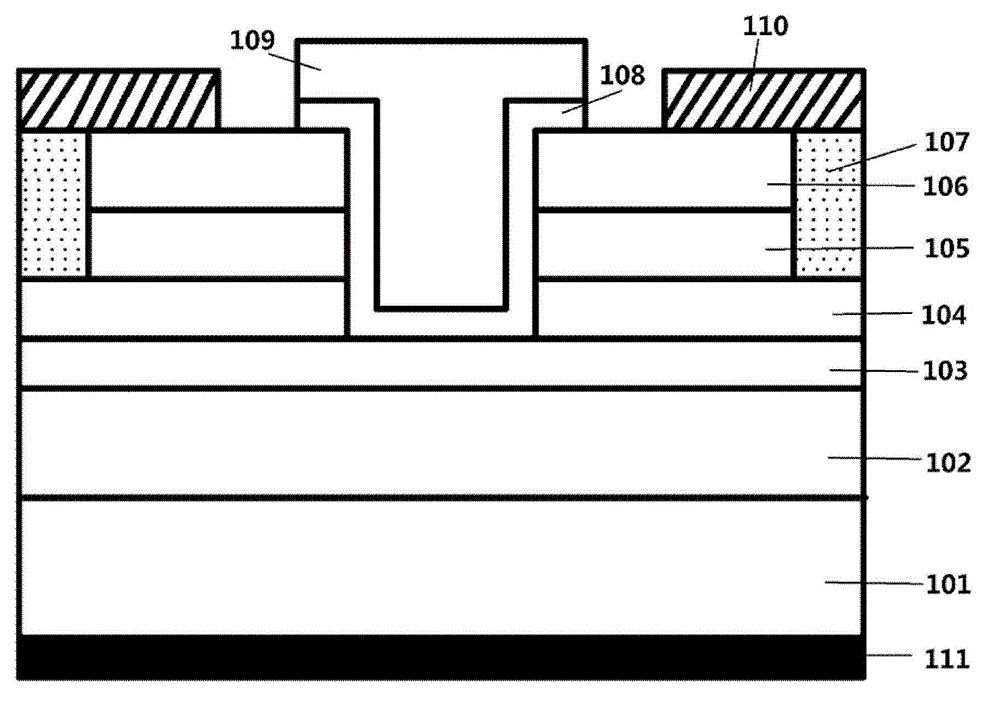

[0027] Such as figure 1 as shown, figure 1 A schematic diagram showing a GaAs-based vertical structure MOS device according to an embodiment of the present invention, the GaAs-based vertical structure MOS device includes: an N-type GaAs substrate layer 101; an N-type low-doped N-type substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More