Duty ratio adjusting circuit

A technology for adjusting circuit and duty cycle, applied in electrical components, generating electrical pulses, pulse generation, etc., can solve the problems that the clock signal cannot reach the duty cycle, the adjustment circuit is complicated, the charging time and the discharging time are not equal, etc. Achieve the effect of low cost and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

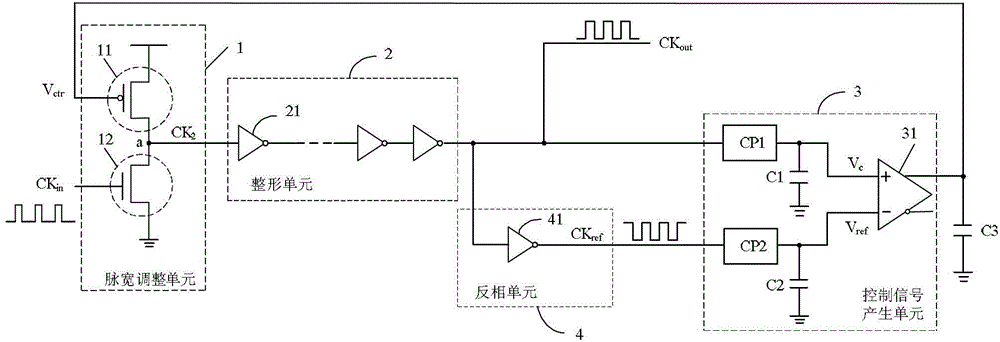

[0044] image 3 It is a circuit diagram of the duty cycle adjustment circuit of the first embodiment of the present invention.

[0045] Such as image 3 As shown, the duty cycle adjustment circuit includes: a pulse width adjustment unit 1, a shaping unit 2, a control signal generation unit 3, and an inversion unit 4.

[0046] Wherein, the pulse width adjustment unit 1 includes: a first transistor 11 and a second transistor 12;

[0047] The gate of the first transistor 11 inputs a control signal V ctr , The gate of the second transistor 12 inputs the first clock signal CK in ;

[0048] The drain of the first transistor 11 is connected to the drain of the second transistor 12 to output a second clock signal CK 2 ;

[0049] The source of the first transistor 11 is connected to a first voltage source, and the source of the second transistor 12 is connected to a second voltage source.

[0050] Wherein, the shaping unit 2 includes: an odd number of inverters 21 connected in series, and the s...

Embodiment 2

[0087] In this embodiment, the duty cycle adjustment circuit is similar to that in Embodiment 1. The difference is that the shaping unit in this embodiment includes an even number of inverters, and the connection mode of the amplifier in the control signal generating unit is the same as in Embodiment 1. Different.

[0088] Image 6 It is a circuit diagram of the duty cycle adjustment circuit of the second embodiment of the present invention.

[0089] Such as Image 6 As shown, the duty cycle adjustment circuit includes: a pulse width adjustment unit 1, a shaping unit 2', a control signal generation circuit 3', and an inversion unit 4.

[0090] The pulse width adjusting unit 1 and the inverting unit 4 are the same as or similar to those in the first embodiment, and will not be repeated here. The shaping unit 2'includes an even number of inverters 21, and the structures of the first charge pump CP1 and the second charge pump CP2 included in the control signal generating unit 3'are sim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More