Non-volatile highly-resistant-single-particle configuration memory unit

A memory cell and single-particle technology, applied in the field of integrated circuits, can solve the problems of non-mentioned, non-volatile memory, and weakened anti-radiation effect of DICE cells, so as to save the external configuration memory and simplify the system.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

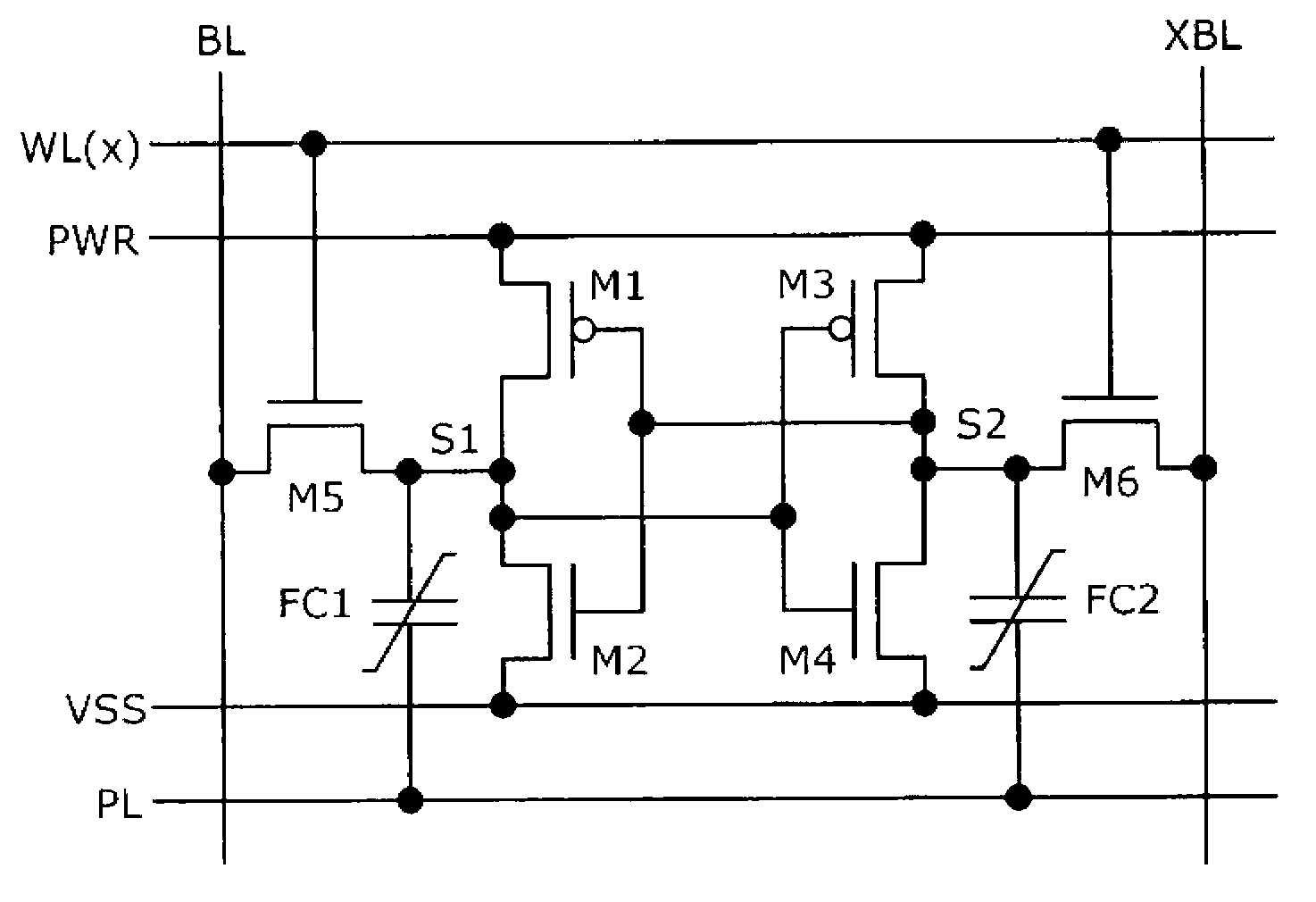

[0040] Embodiment 1: see Figure 5 .

[0041] This embodiment includes 8 MOS transistors, gate MOS transistors and PL board lines that form a 4-level DICE structure. Among the 4 nodes (P1~P4) of the DICE structure, the two nodes marked P1 and P4 are used as ferroelectric A connection node, the ferroelectric connection node refers to a node connected to the PL board line through a ferroelectric capacitor.

[0042] Specifically, this embodiment includes a first ferroelectric capacitor FeC1, a second ferroelectric capacitor FeC2, and 10 MOSFETs (M1~M10), wherein the MOS transistors marked as M1, M3, M5, and M7 are PMOS transistors, marked as The MOS tubes of M2, M4, M5, and M8 are NMOS tubes, which together form an 8-tube DICE SRAM structure. The MOS transistors marked M9 and M10 are the read and write gates controlled by the word line WL signal, VCC and VSS are the high and low power supplies of the chip, BL and ~BL are a pair of opposite bit line signals, and the PL signal is r...

Embodiment 2

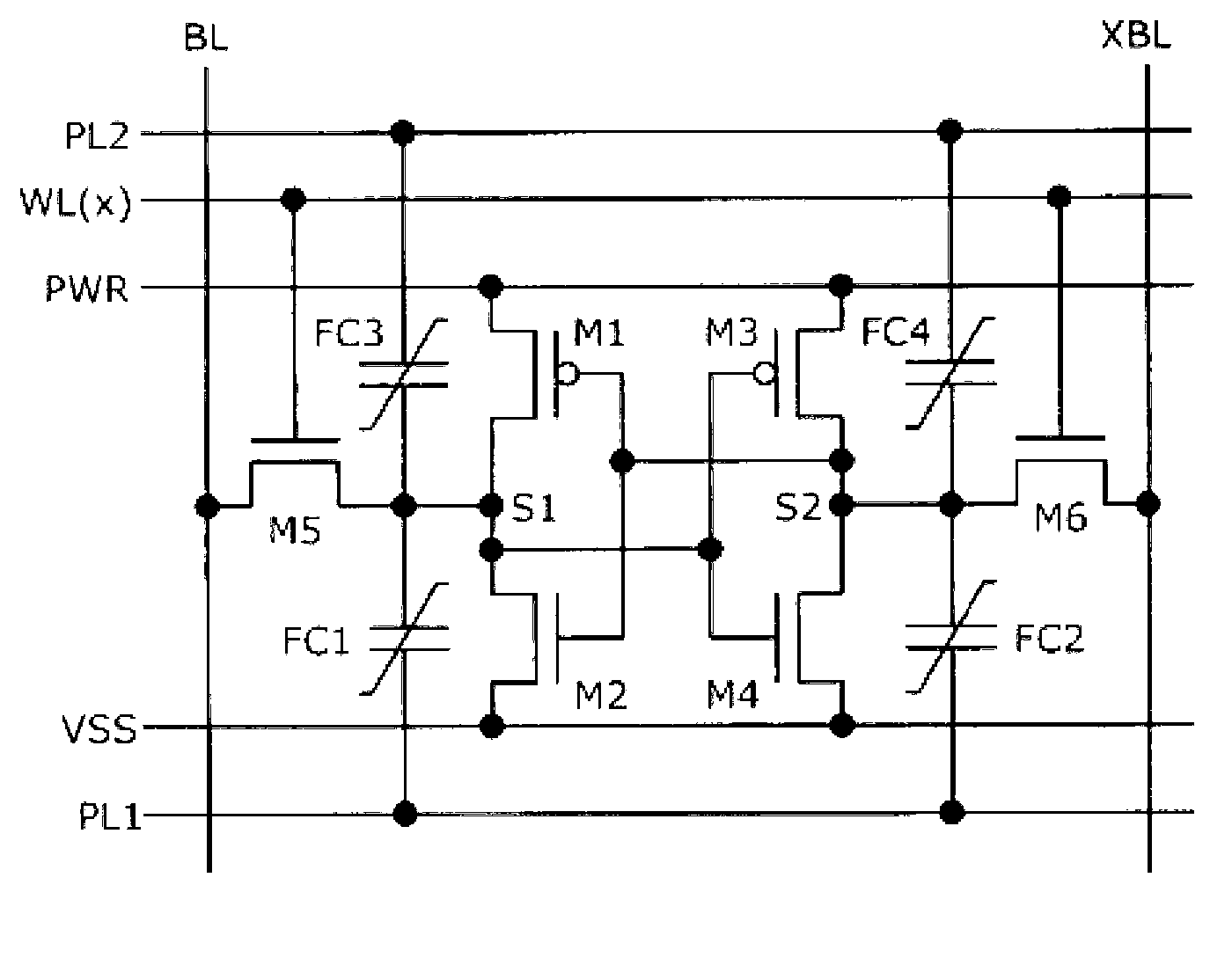

[0044] Example 2: see Figure 6 .

[0045] The difference between this embodiment and embodiment 1 is that the connection positions of FeC1 and FeC2 are changed. In Embodiment 1, the two nodes at the front and rear ends are used as ferroelectric connection nodes. In this embodiment, the two nodes in the middle are used as ferroelectric connection nodes, that is, the two nodes marked as P2 and P3 are used as ferroelectric connection nodes.

Embodiment 3

[0046] Embodiment 3: see Figure 7 .

[0047] The difference between this embodiment and Embodiment 1 is that in this embodiment, four ferroelectric capacitors FeC1-FeC4 are respectively connected to the four nodes of the DICE.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More