C-to-RTL comprehensive method based on visual fields intact (VFI) optimization

A comprehensive method, c-to-rtl technology, applied in the field of hardware design automation, can solve problems such as no VFI design support, design and optimization without considering C language, and inability to optimize settings, so as to improve hardware performance and reduce power consumption , enhance the practicality and the effect of the scope of application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The specific implementation manner of the invention will be further described below in conjunction with the accompanying drawings and embodiments. The following examples are only used to illustrate the present invention, but not to limit the scope of the present invention.

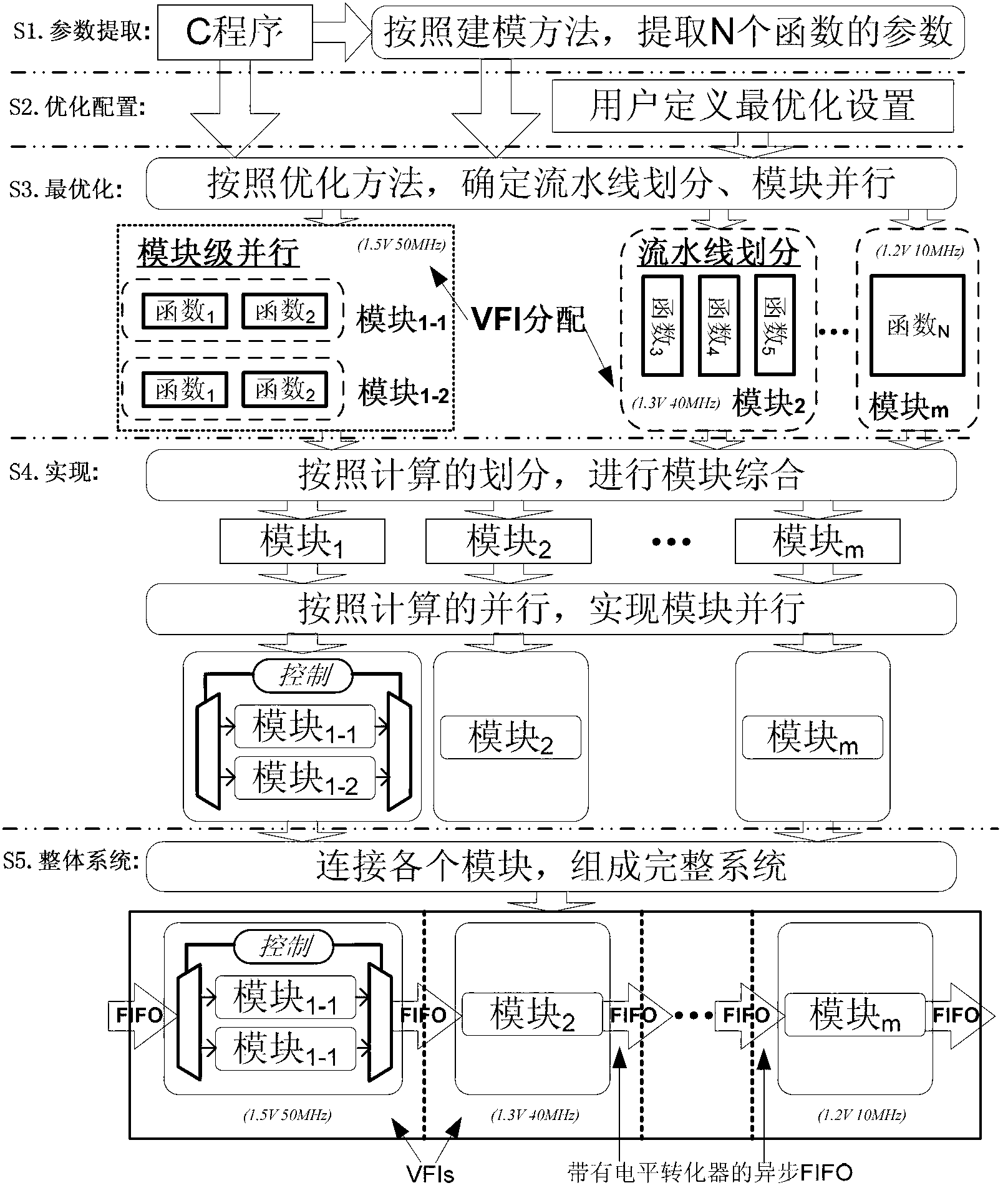

[0041] Flowchart such as figure 1 The shown C-to-RTL synthesis method for pipeline division and module parallel optimization mainly includes the following steps:

[0042] S1. Using the existing C-to-RTL tool, synthesize each function to be synthesized in the input C program in advance, and then extract or calculate the function parameters after synthesis; wherein, the C program is required to be composed of N functions, and these to-be-synthesized functions are required The connection topological relationship of the synthesis function is linear, and this requirement can be realized by modifying the programming style of the C program. Wherein, the function parameters include function operation cycl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More