Method for manufacturing non-volatile memory element, and non-volatile memory element

A technology of non-volatile storage and manufacturing method, applied in electrical components, semiconductor devices, electric solid devices, etc., can solve the problems of high initial breakdown voltage, uneven initial breakdown voltage, etc., and achieve the effect of reducing the effective area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

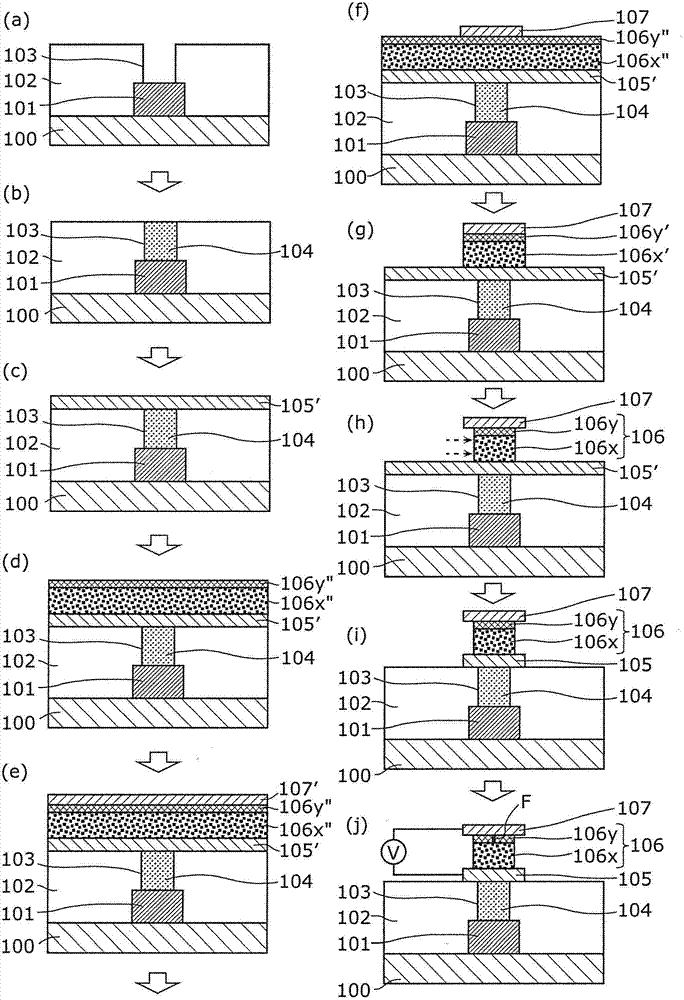

[0079] First, like figure 1 As shown in (a), a conductive layer made of aluminum or the like (with a film thickness of, for example, 400 nm or more and 600 nm or less) is formed on a substrate 100 on which transistors, lower wiring, etc. are formed, and patterned to form the lower wiring 101.

[0080] Then, after covering the lower layer wiring 101 and forming an insulating film on the substrate 100, the surface of the insulating film is planarized to form an interlayer insulating layer 102 (the film thickness is, for example, 500 nm or more and 1000 nm or less). Regarding the interlayer insulating layer 102, a plasma TEOS (Tetraethyl orthosilicate) film is used, or a fluorine-containing oxide (for example, FSG (Fluorinated Silicate Glass)) and other low-k materials are used to reduce the parasitic capacitance between wirings.

[0081] Then, the interlayer insulating layer 102 is patterned using a desired mask to form a contact hole 103 (a hole diameter of 50 nm or more and 300 nm o...

Embodiment approach 2

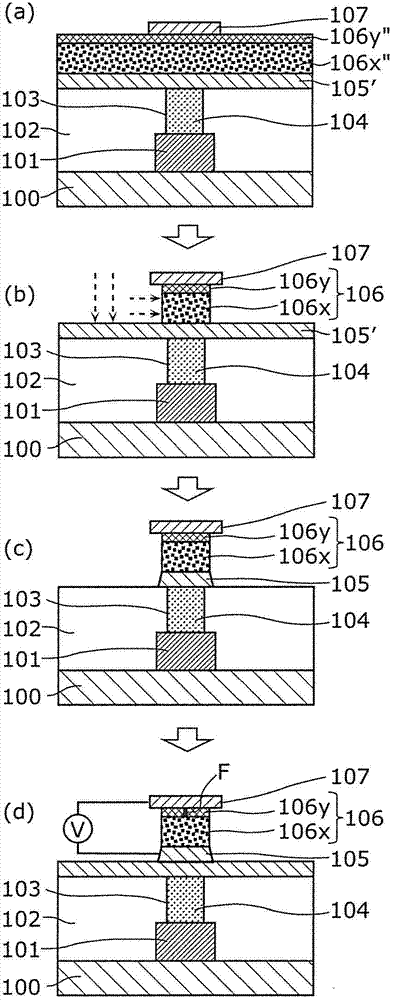

[0117] figure 2 (A) to (d) are cross-sectional views showing the method of manufacturing the main part of the nonvolatile memory element in the second embodiment of the present invention. in figure 2 (A) ~ (d), right and figure 1 (A) to (j) The same components are assigned the same symbols, and descriptions are omitted.

[0118] Such as figure 2 As shown in (a) to (d), the manufacturing method of the nonvolatile memory element of the first embodiment of the present invention is different from the manufacturing method of the nonvolatile memory element of the second embodiment of the present invention in that it differs from figure 1 The process of patterning the variable resistance film 106x" and the second variable resistance film 107y" shown in (g) and (h) simultaneously removes the side portion of the variable resistance element.

[0119] In the method of manufacturing the nonvolatile memory element of the first embodiment of the present invention, the variable resistance film ...

Embodiment approach 3

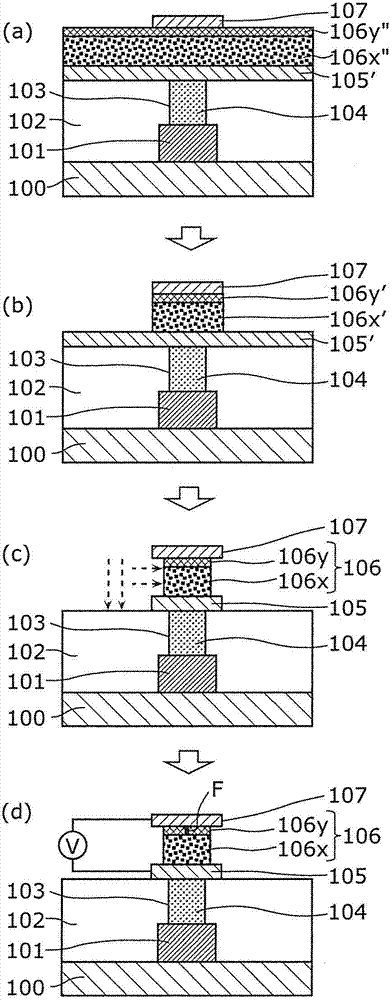

[0131] image 3 (A) to (d) are cross-sectional views showing the method of manufacturing the main part of the nonvolatile memory element in the third embodiment of the present invention. in image 3 (A) ~ (d), right and figure 1 (A) to (j) The same components are assigned the same reference numerals, and the description is omitted.

[0132] Such as image 3 As shown in (a) to (d), the difference between the manufacturing method of the non-volatile memory element of the first embodiment of the present invention and the method of manufacturing the non-volatile memory element of the third embodiment of the present invention is that they are performed simultaneously figure 1 Steps of removing the side portions of the variable resistance film 106x" and the second variable resistance film 107y" shown in (h) and (i) and patterning the first conductive film 105'.

[0133] In the manufacturing method of the nonvolatile memory element of the first embodiment of the present invention, after pa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Film thickness | aaaaa | aaaaa |

| Film thickness | aaaaa | aaaaa |

| Film thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More