Submission method of descriptor of network interface card (NIC) based on mixing of PIO (process input output) and DMA (direct memory access)

A network interface card and descriptor technology, applied in the field of high-speed interconnection network of high-performance computers, can solve the problems of transmission bottleneck, low startup overhead, limited capacity, etc., achieve capacity expansion, improve submission efficiency and data communication efficiency, and reduce startup delayed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

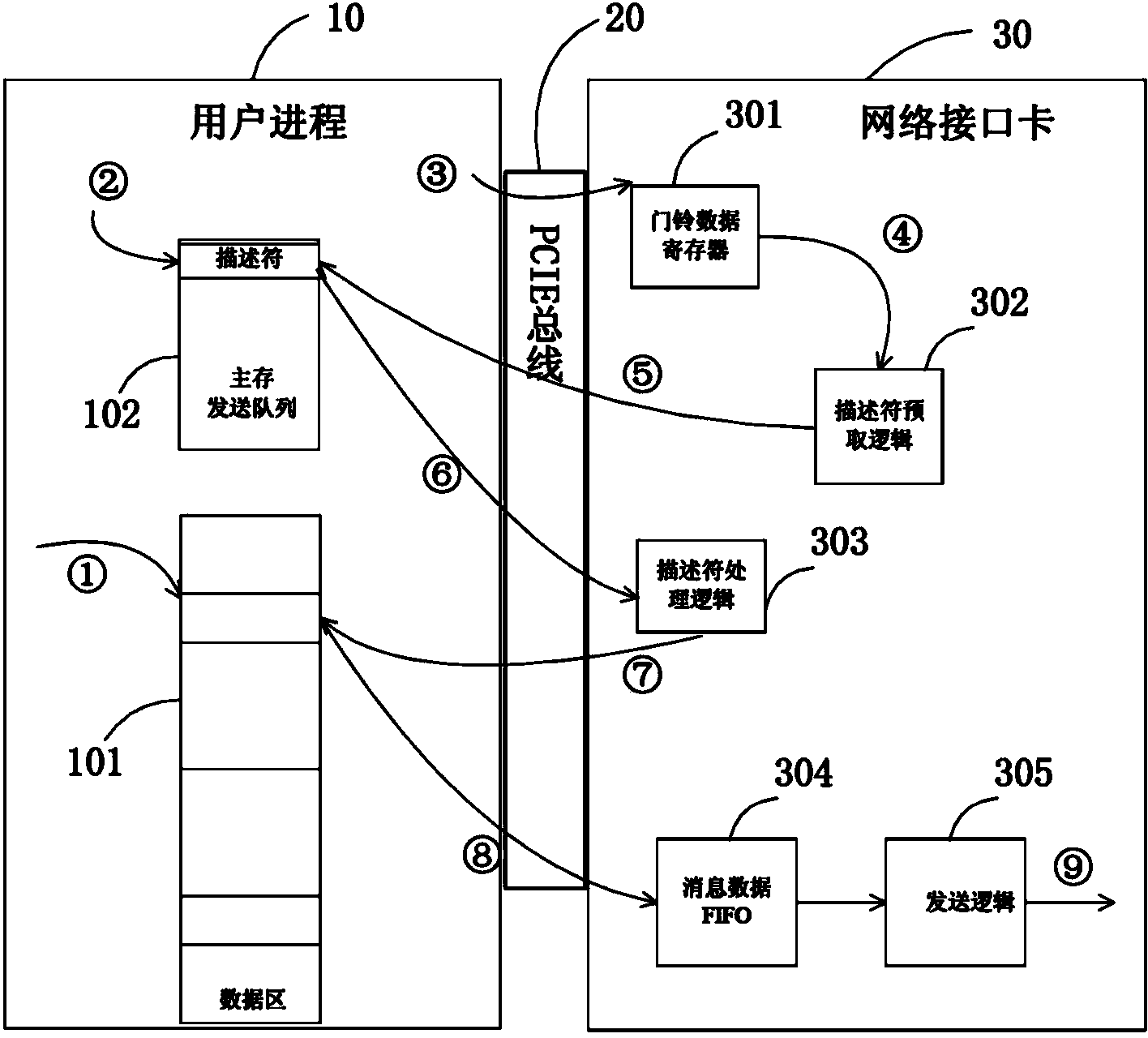

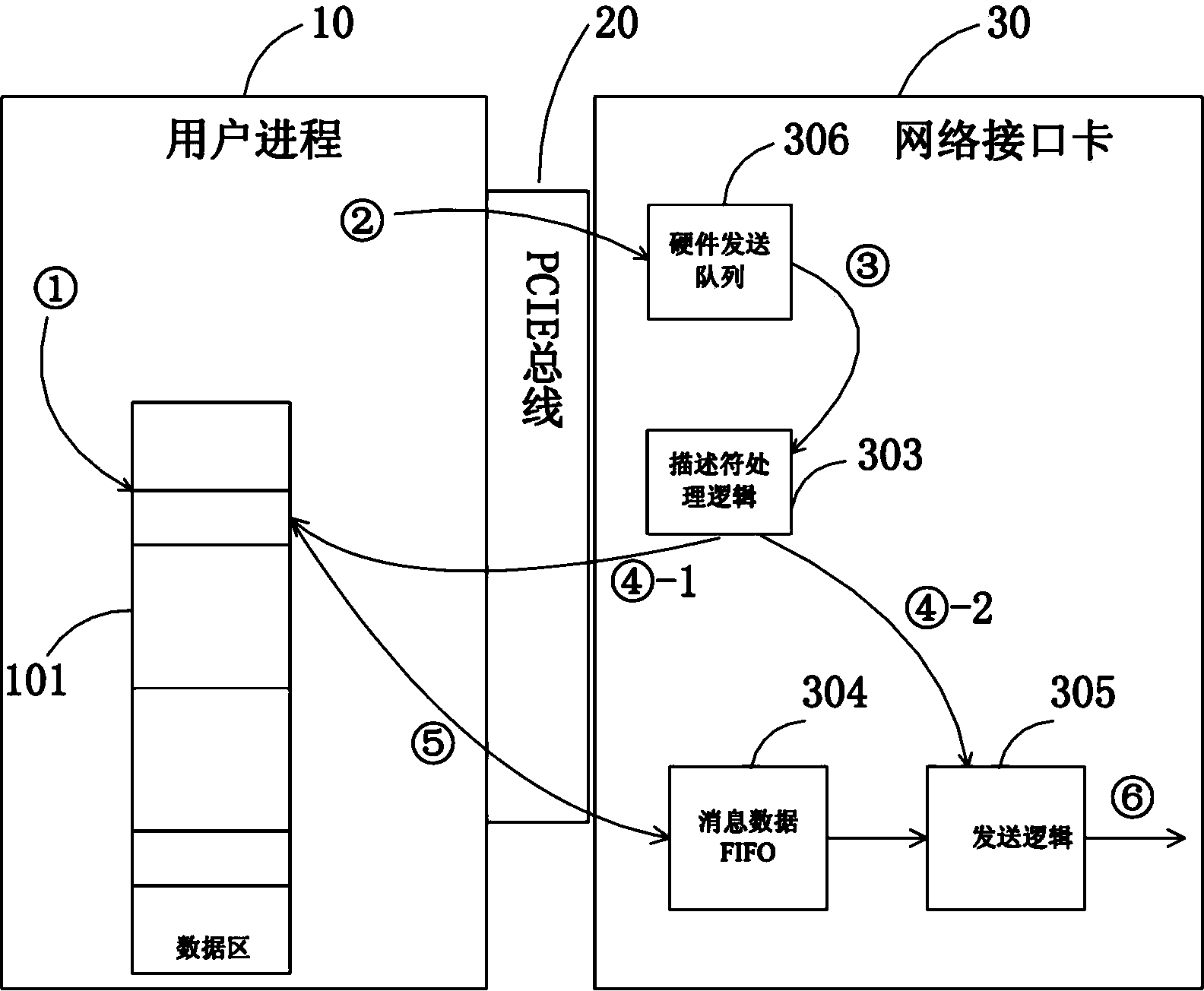

Embodiment Construction

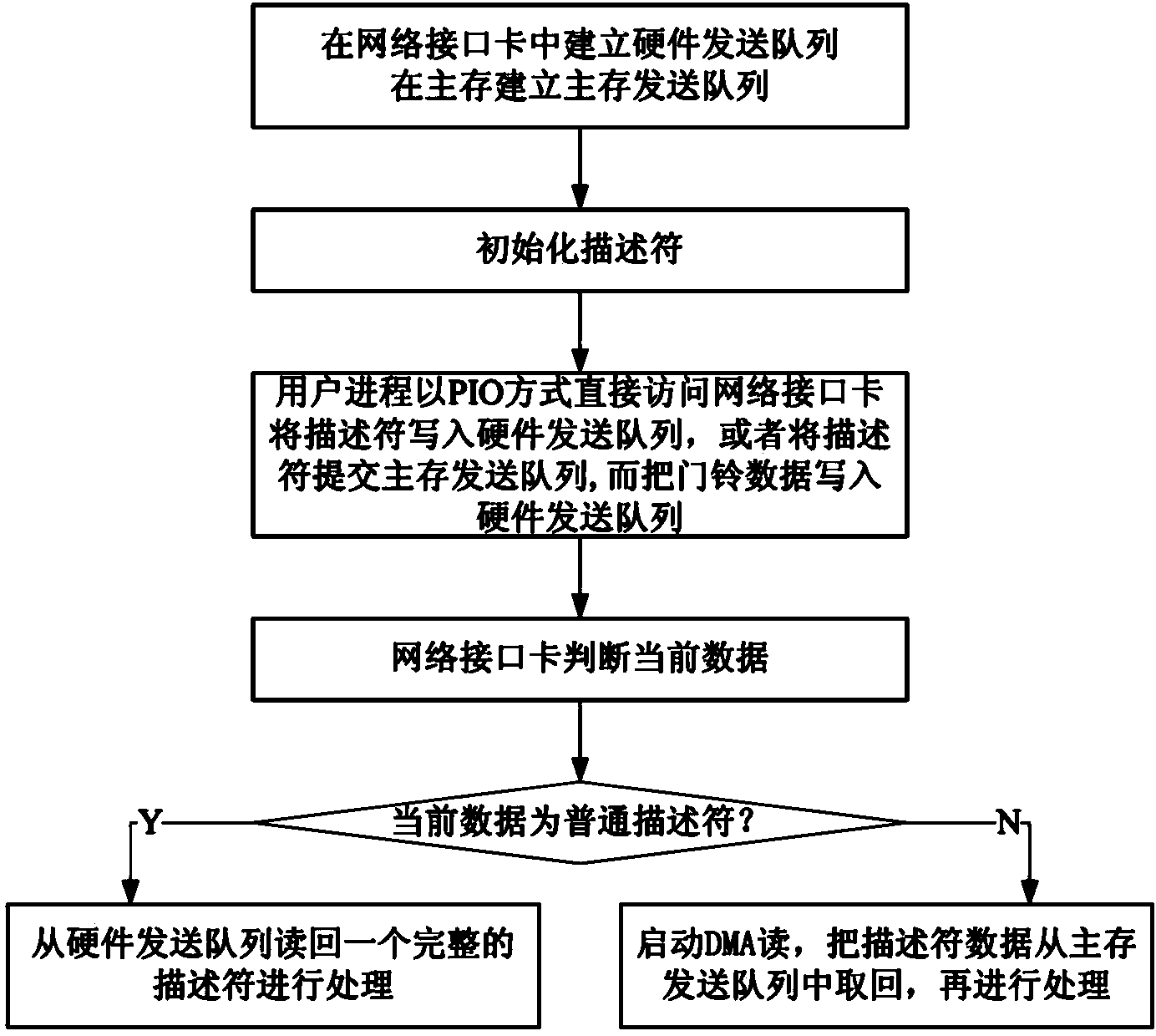

[0067] like image 3 As shown, the implementation steps of the method for submitting the network interface card descriptor in this embodiment are as follows:

[0068] 1) Establish a hardware send queue for storing descriptors and doorbell data written in PIO mode in the network interface card, and establish a main memory send queue for storing descriptors in the main memory; the hardware send queue and the main memory send The read pointer of the queue is maintained by the network interface card, and the write pointer of the hardware send queue and the main memory send queue is maintained by the user process;

[0069] 2) Initially generate the descriptor to be sent according to the user's communication request, and the type of the initialized generated descriptor is a normal descriptor without data or an immediate descriptor with data;

[0070] 3) Determine the type of the descriptor to be sent. If the descriptor to be sent is an immediate descriptor, write it into the hardwa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More