Metal grid electrode manufacturing method and CMOS manufacturing method

A manufacturing method and metal gate technology, which are applied in the field of metal gate manufacturing and CMOS manufacturing, can solve the problems of semiconductor device failure, open circuit, and reduced conductivity of Al metal electrodes, so as to prevent performance degradation and avoid voids. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0075] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0076] Such as Figure 5 As shown, it is a flow chart of an embodiment of the metal gate manufacturing method of the present invention, the method includes:

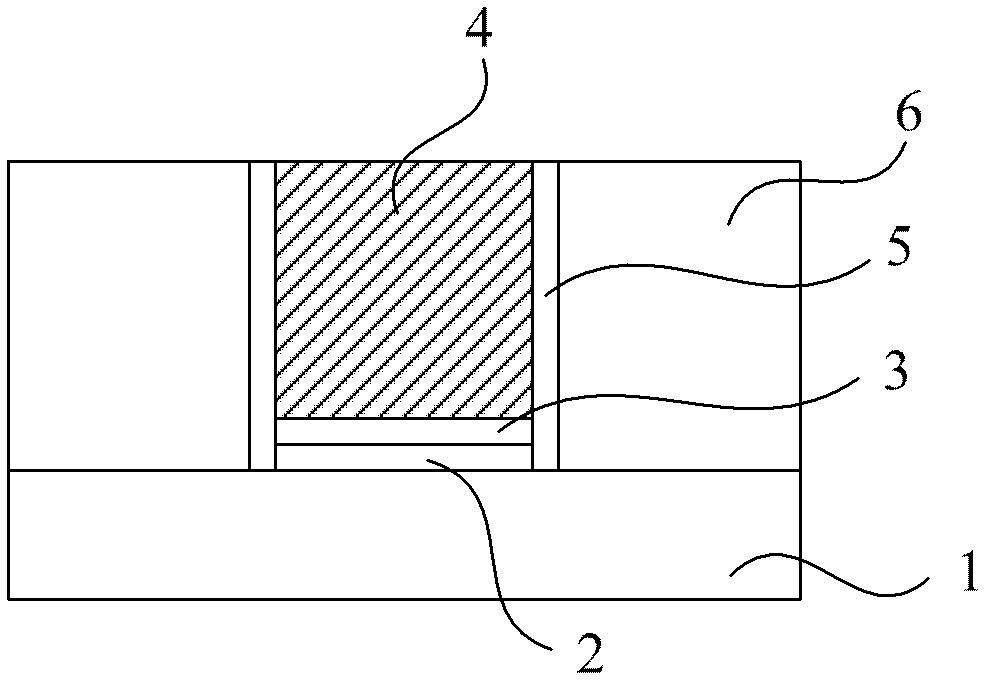

[0077] Step 1: Provide a substrate formed with a dummy gate structure, the dummy gate structure includes an interface layer, a high dielectric constant gate dielectric layer and a dummy polysilicon gate sequentially formed on the substrate, along the dummy gate structure Sidewalls are formed on both sides, and an interlayer dielectric layer is also formed on the substrate outside the sidewalls;

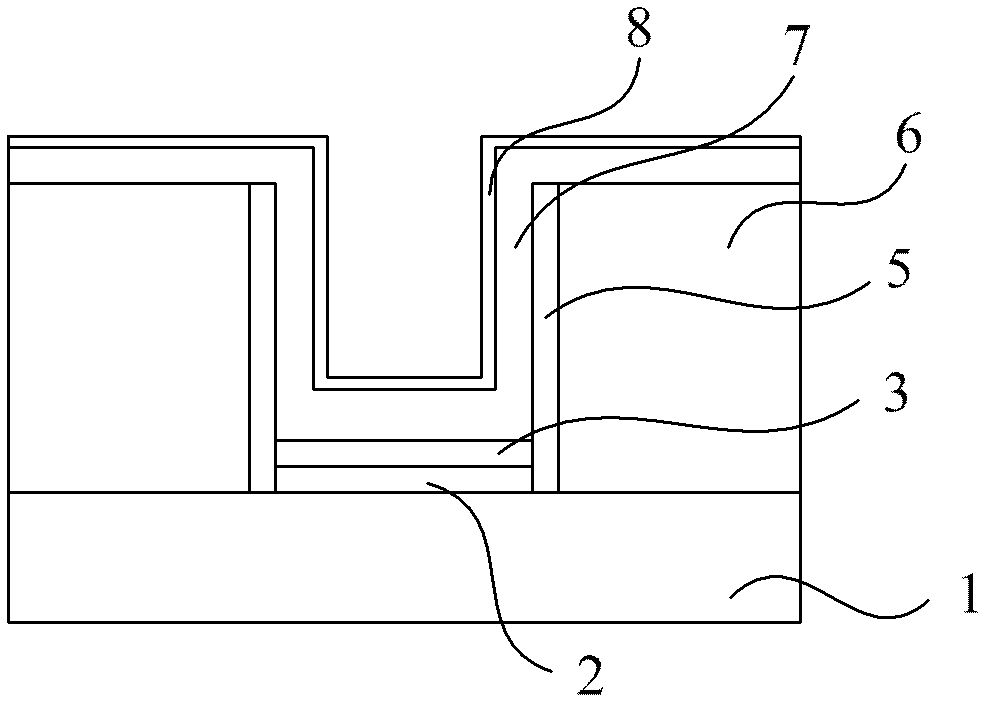

[0078] Step 2: removing the dummy polysilicon gate to form a trench, and sequentially depositing a metal work function layer and an isolation layer in the trench;

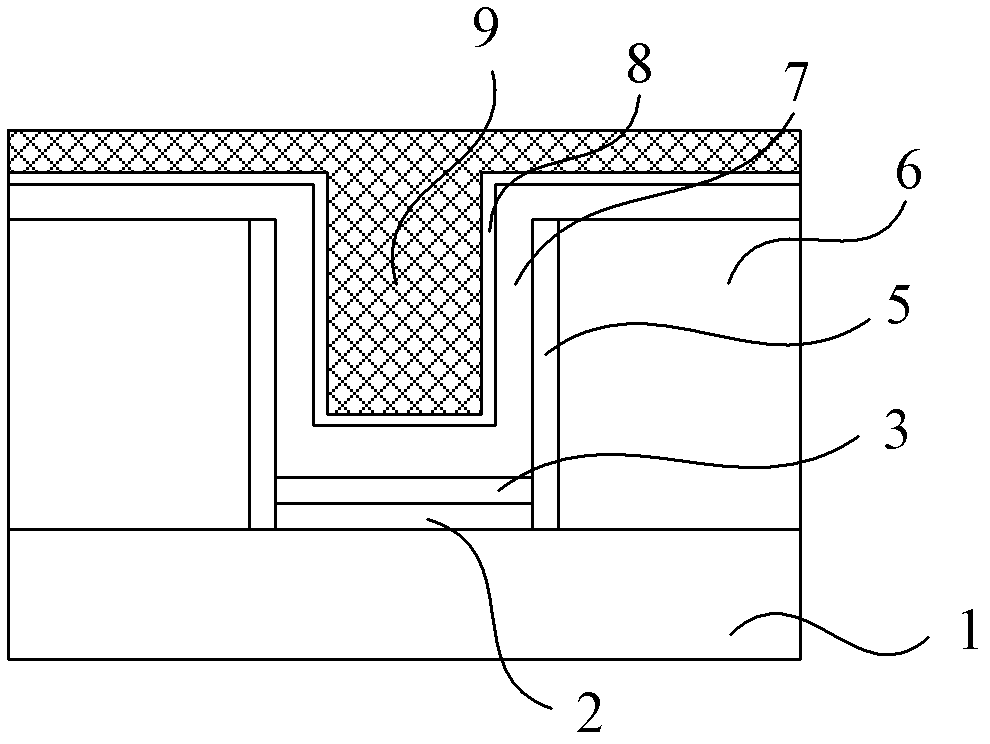

[0079] Step 3: depositing a polysilic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More