Behavioral modeling methods for clock and data recovery circuit and analog circuits

A technology for recovering circuits and modeling methods, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of not supporting modeling and simulation, low modeling efficiency, analog voltage, current modeling and simulation difficulties and other problems, to achieve the effect of easy implementation, improved efficiency, and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the technical problems, technical solutions and beneficial effects to be solved by the present invention clearer and clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

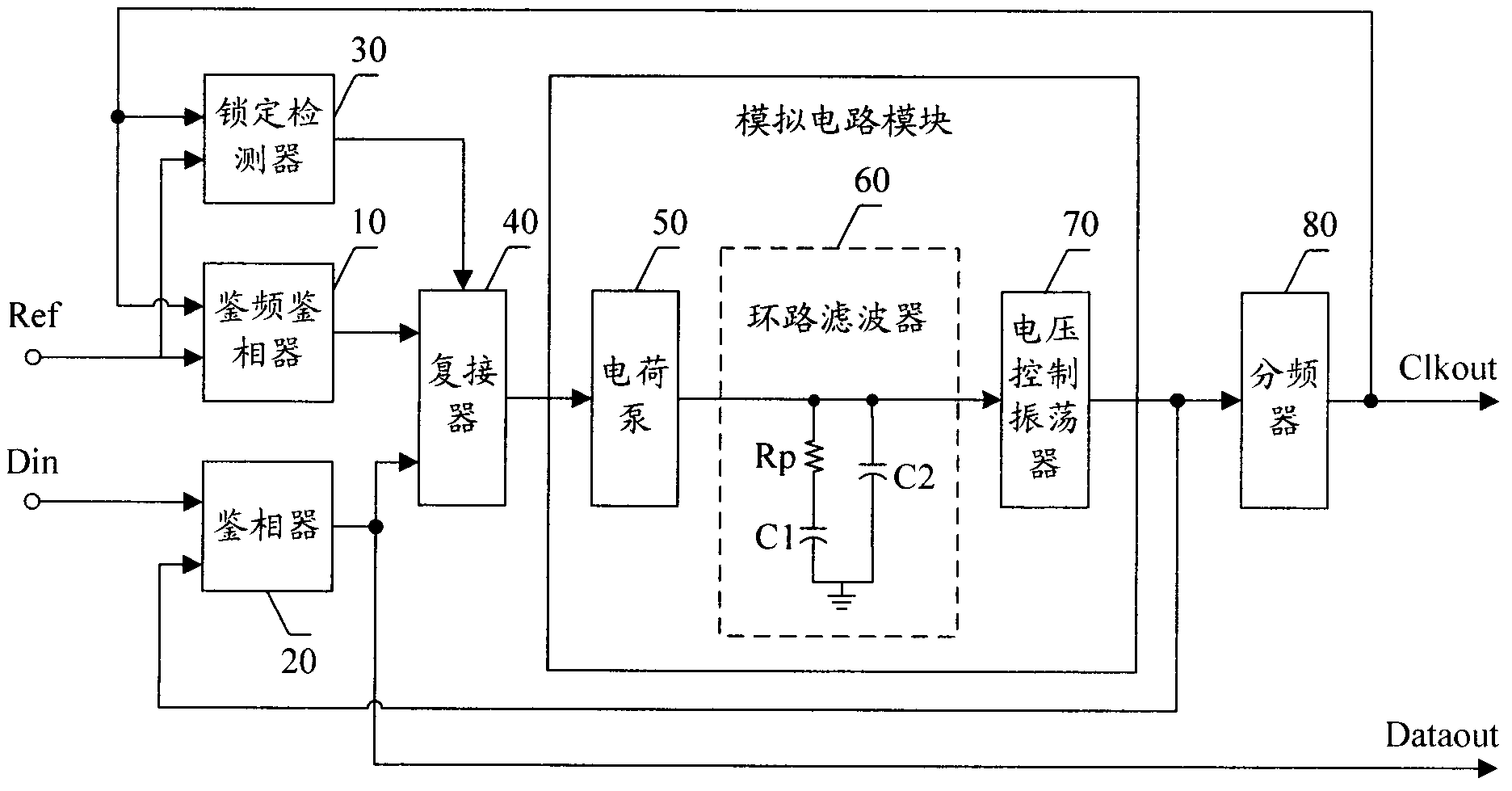

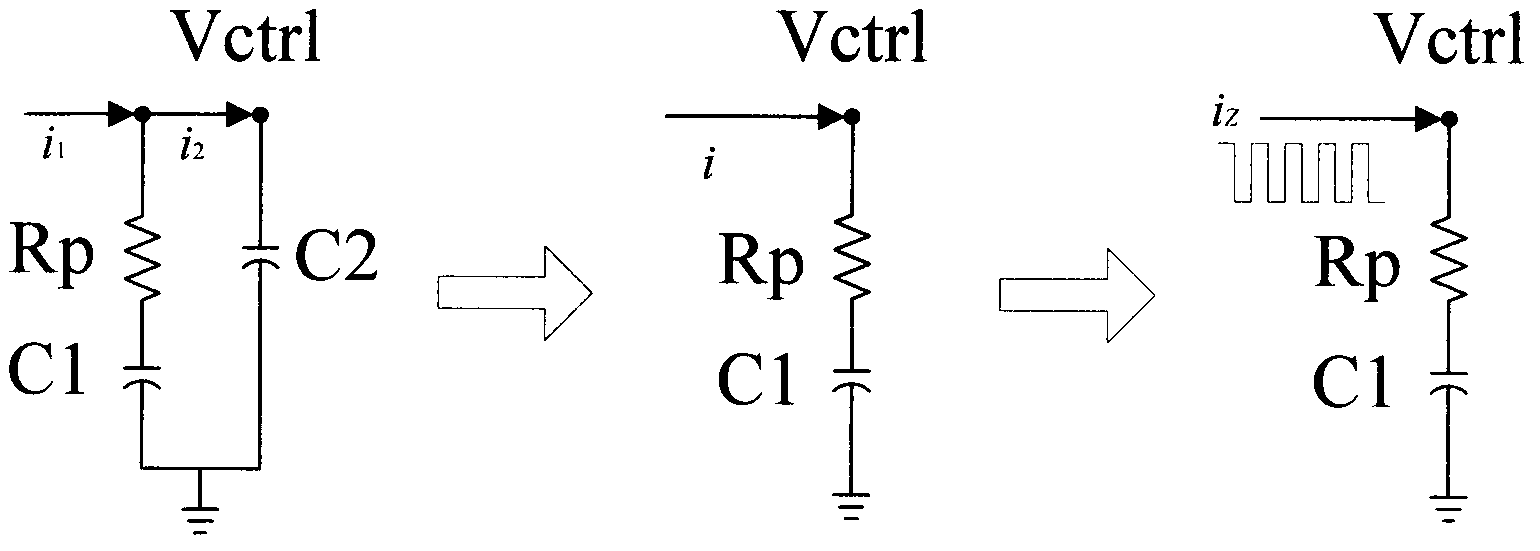

[0039] The present invention provides a behavior-level modeling method of a clock and data recovery circuit, adopts Verilog hardware description language, introduces a virtual high-speed sampling clock in the modeling process, and performs sampling and discretization operations on continuously changing voltages and currents; and then The current and voltage after the discretization operation are described in Verilog language; after the voltage on the loop filter is obtained, the present invention calculates the period of the output signal of the voltage ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More