Method for manufacturing high-evenness grid electrode lines

A gate line and uniformity technology, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve problems such as high cost, complicated process, and low production capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

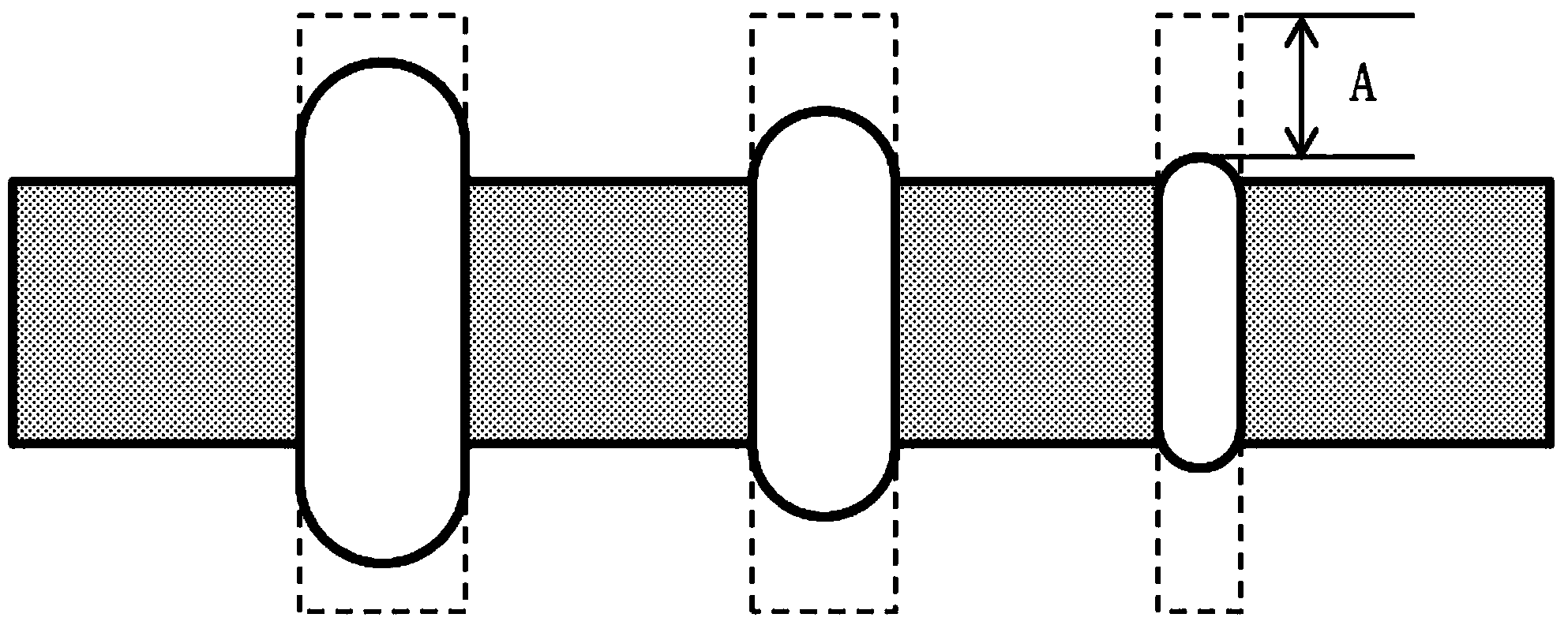

[0046] Figure 4A to Figure 4G A method for fabricating high-uniformity gate lines according to a preferred embodiment of the present invention is schematically shown.

[0047] Specifically, as Figure 4A to Figure 4G As shown, the method for making high-uniformity gate lines according to a preferred embodiment of the present invention includes:

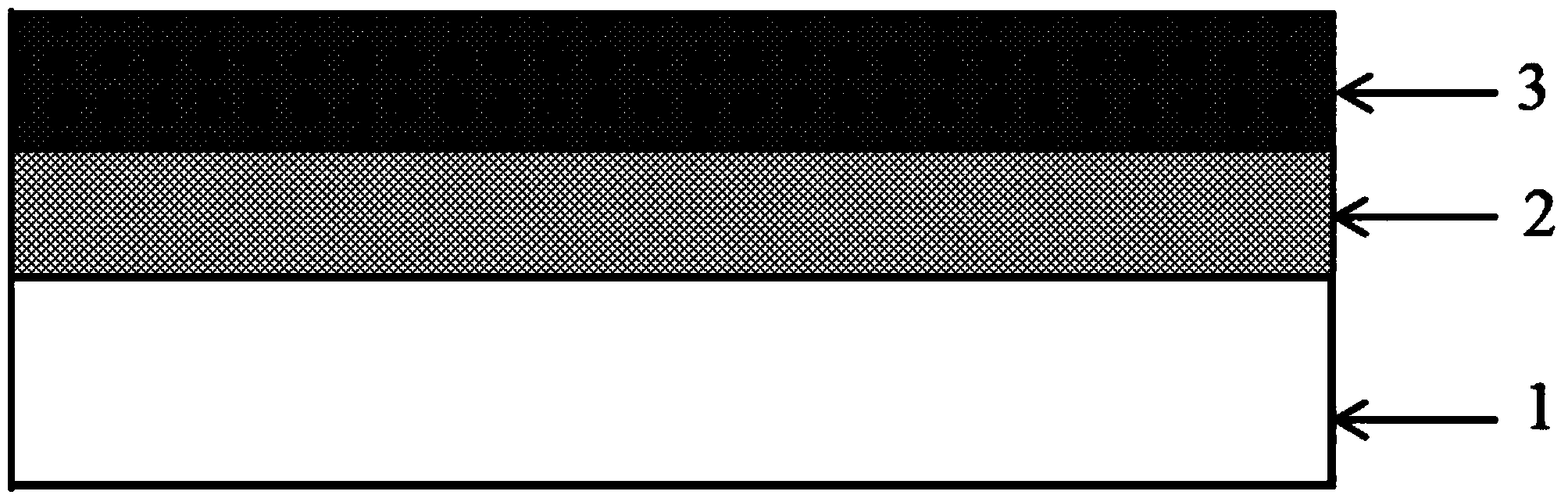

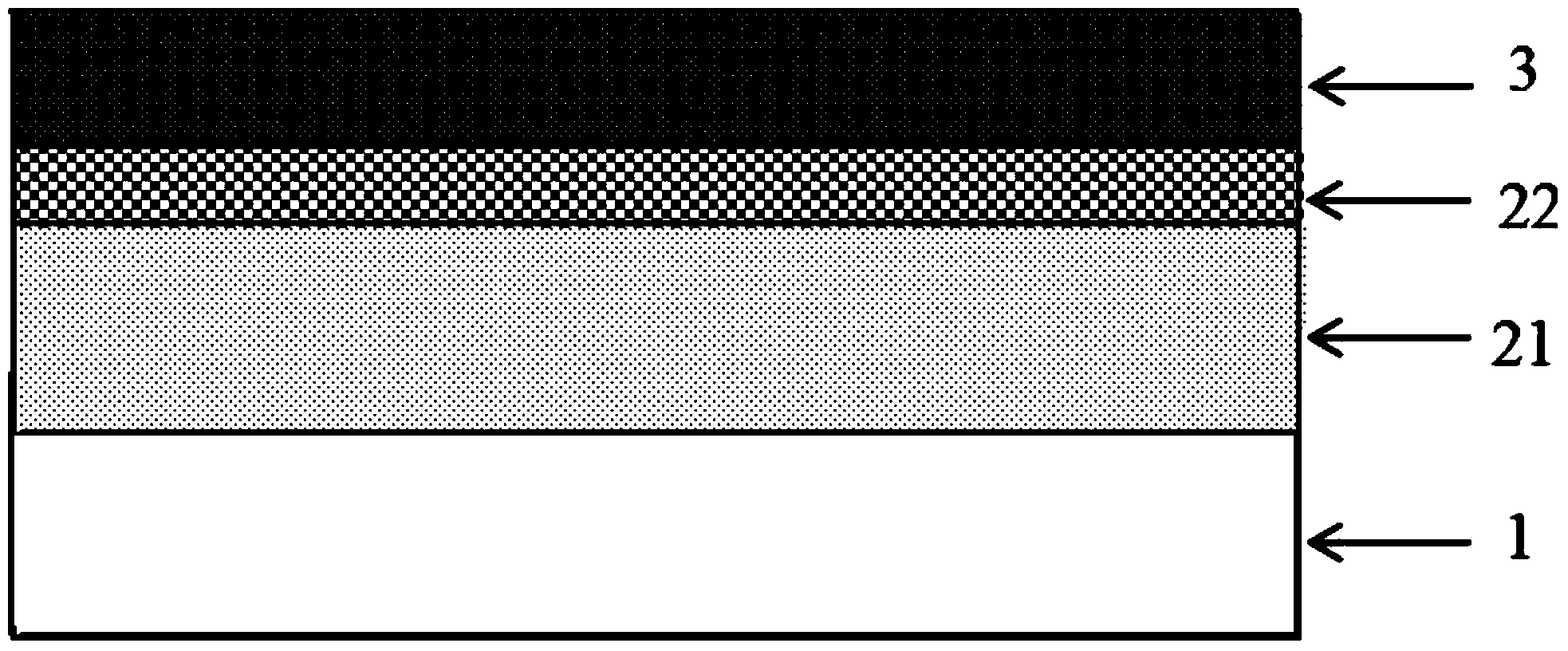

[0048] The first step: on the substrate silicon wafer 1, directly deposit the polysilicon film 4 in sequence, and then directly coat the spin-coated carbon film 21, the silicon-containing hard film 22, and the first photoresist 3 in sequence, such as Figure 4A shown; wherein, it should be noted that the silicon-containing hard film 22 and the first photoresist 3 are combined together as a mask for e...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com