FinFET manufacturing method

A manufacturing method and substrate technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of reducing FinFET device performance, high-k dielectric layer Fermi level pinning, and charge trap effects, etc. Improve the effect of Fermi level pinning, reduce bandgap states or oxygen vacancies, and improve threshold voltage drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

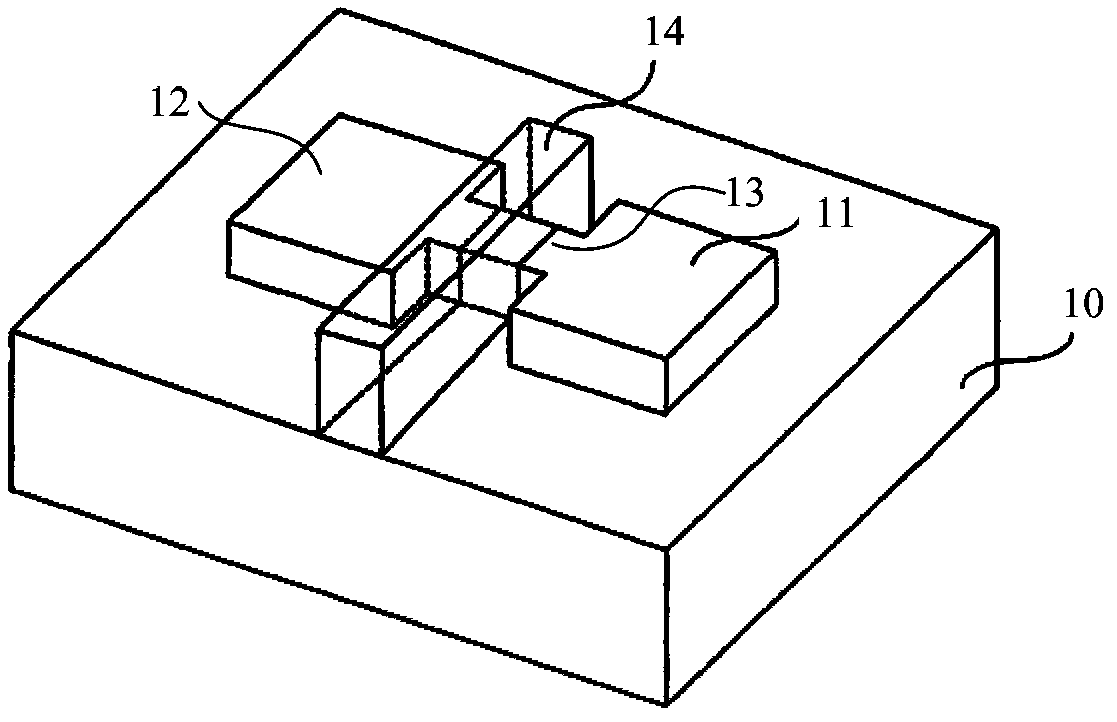

[0028] The FinFET manufacturing method proposed by the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

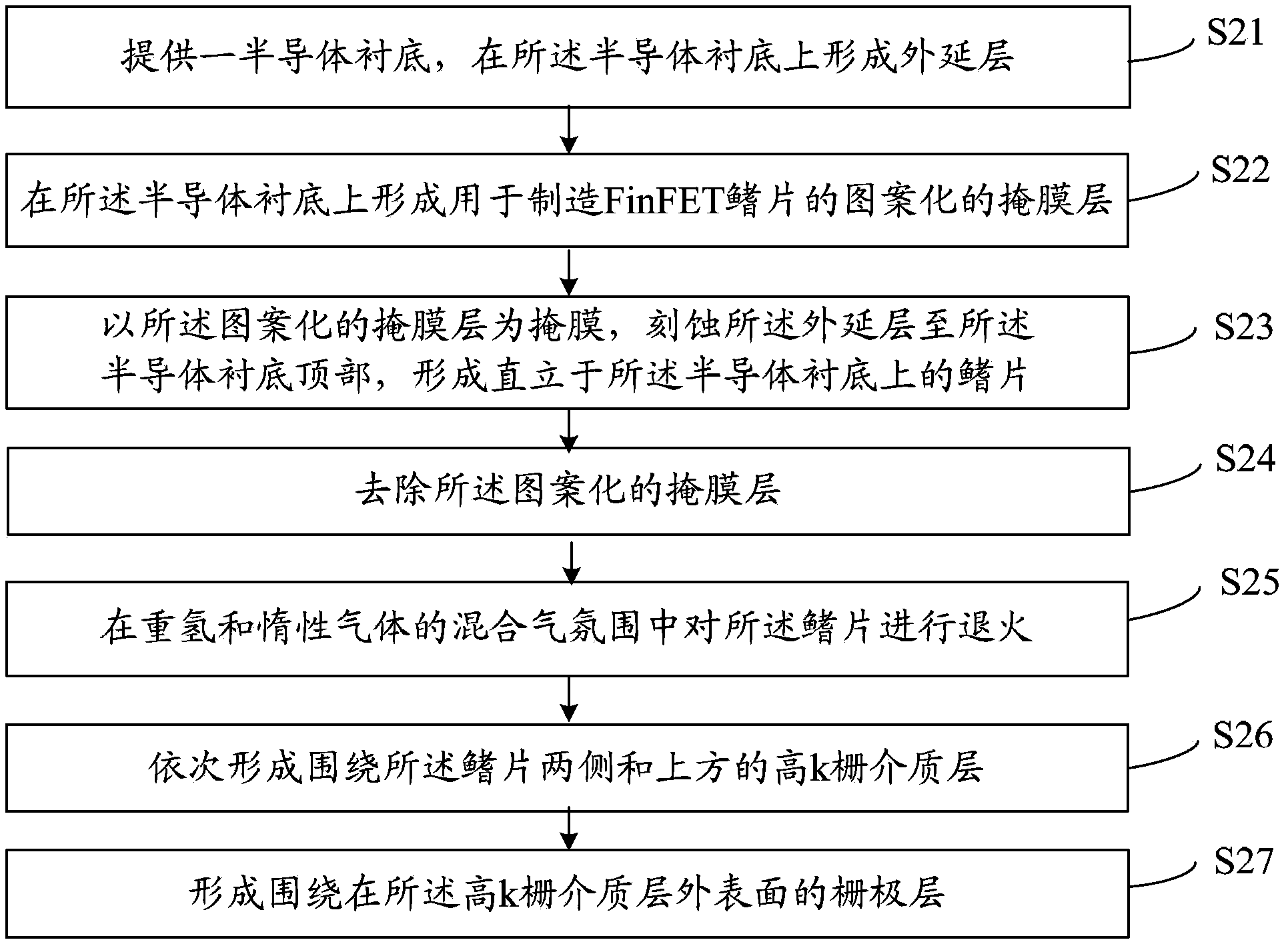

[0029] Such as figure 2 As shown, the present invention provides a kind of FinFET manufacturing method, comprises the following steps:

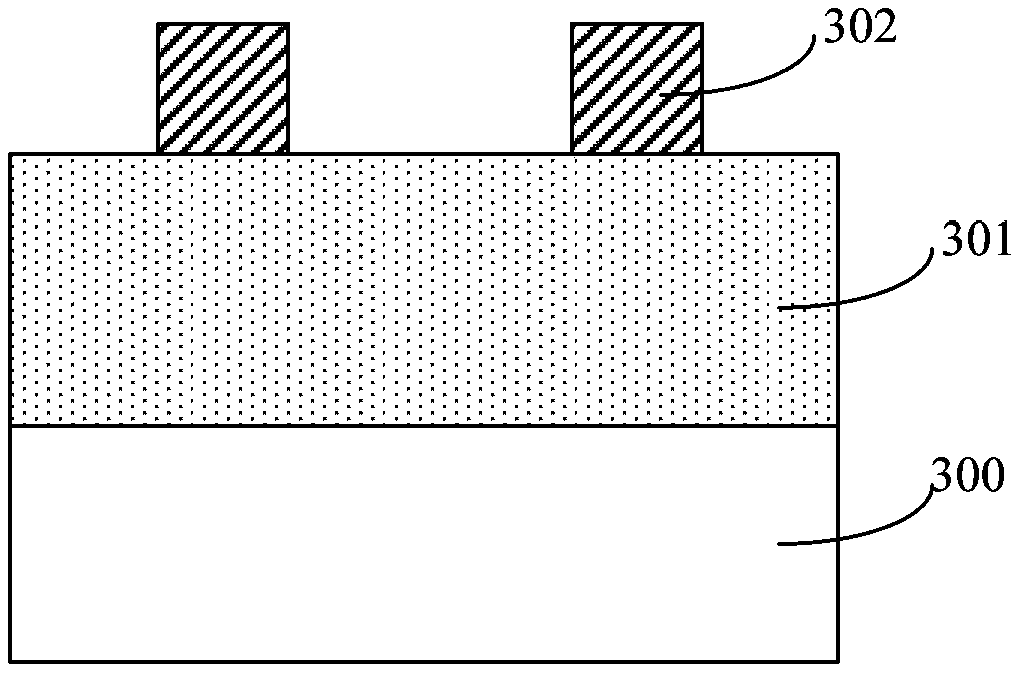

[0030] S21, providing a semiconductor substrate, forming an epitaxial layer on the semiconductor substrate;

[0031] S22, forming a patterned mask layer for manufacturing FinFET fins on the semiconductor substrate;

[0032] S23. Using the patterned mask layer as a mask, etch the epitaxial layer up to the top of the semiconductor substrate to form fins standing on the semiconductor substrate.

[0033] S24, removing the patterned mask layer;

[0034] S25, annealing the fins in a mixture gas atmosphere of deuterium and inert gas

[0035] S26, forming a high-k gate dielectric layer surrounding both sides and above the fin;

[0036] S27, forming a gate layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More