On-chip scratch-pad memory (SPM) management method facing multitasking embedded system

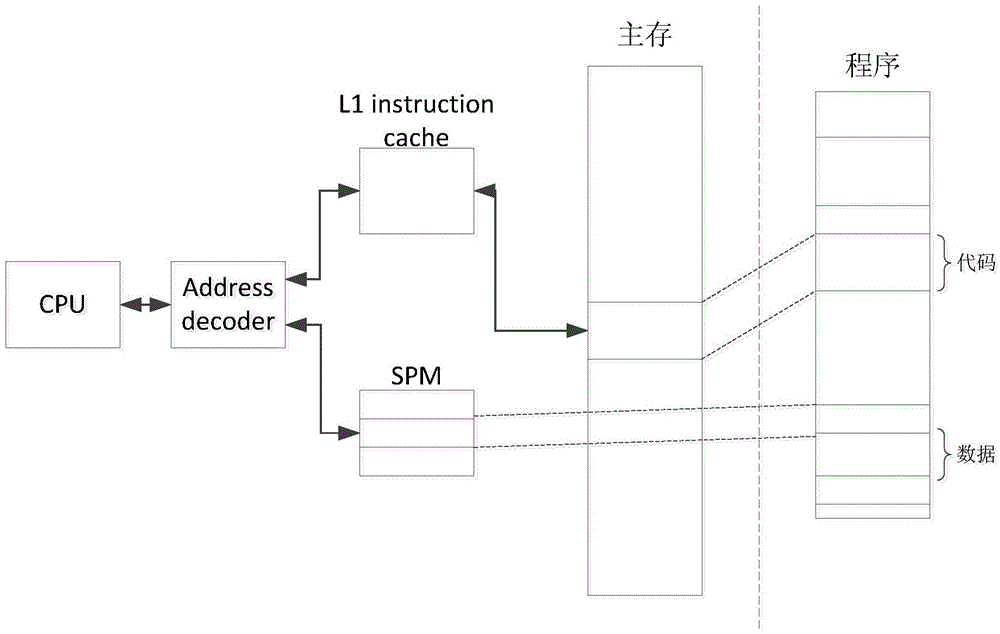

A technology of scratch pad memory and embedded system, which is applied in memory systems, instruments, multi-program devices, etc., and can solve problems such as multi-time, memory block allocation, and insufficient utilization of SPM.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] An example of the present invention is given below and the present invention will be further described in conjunction with the accompanying drawings.

[0041] (1) Pre-analyze the program code segment

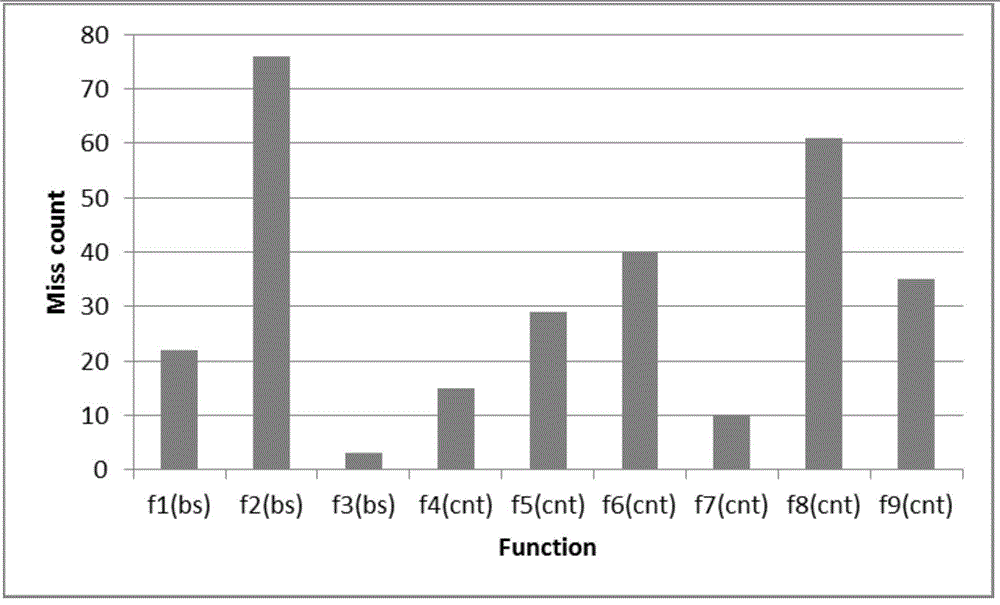

[0042] By analyzing the disassembly file, find out the code segment of the source program, and then analyze the program code segment; the analysis of the code segment is to count the first and last address and size of each function of each task in the multi-tasking system, and analyze the multi-tasking system All functions are numbered uniformly. For a task set (including task bs and task cnt) program (such as image 3 , the X-axis is the function number, and the Y-axis is the number of Cache misses) The obtained code segment information is as follows:

[0043] function number

first address

function size

1

4194624

176

2

4194800

88

3

4194888

488

……

……

……

62

4219232

36

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More