N-bit binary-system electro-optic odd-even checker

A parity check, binary technology, applied in the field of N-bit binary electro-optical parity checker, can solve the problem of small size, achieve the effect of small size, fast check speed and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

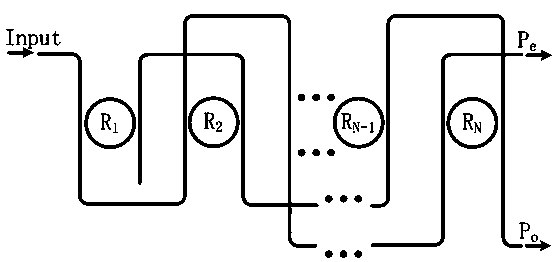

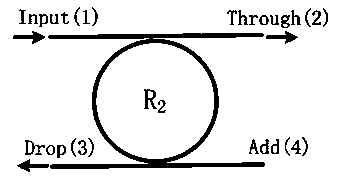

[0022] The N-bit binary electro-optical parity checker of the present invention is composed of N ring waveguides and two curved waveguides, referring to the attached figure 1 , whose basic structure is an MRR-based optical switch, consisting of only one structure of MRR, made of silicon-based nanowire waveguides, N microring resonator MRRs made of semiconductor materials on insulators and two curved Nanowire waveguide implementation, each microring resonator MRR is coupled with two nanowire waveguides, see attached figure 2 . There is a gap or insulation between two adjacent microring resonators MRR that can prevent thermal crosstalk between them.

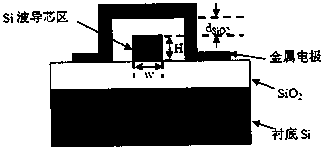

[0023] The MRR structure of the thermal modulation mechanism or electric modulation mechanism of the present invention is shown in image 3 .

[0024] The input of the device of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More