Formation method for semiconductor structure

A technology of semiconductors and conductive plugs, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficult control and unstable performance of semiconductor devices, achieve stable performance, avoid over-polishing or incomplete polishing, Controllable effect of chemical mechanical polishing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] As mentioned in the background art, in the process of forming through-silicon vias in the prior art, the end point of the planarization is difficult to control, resulting in unstable performance of the formed semiconductor device.

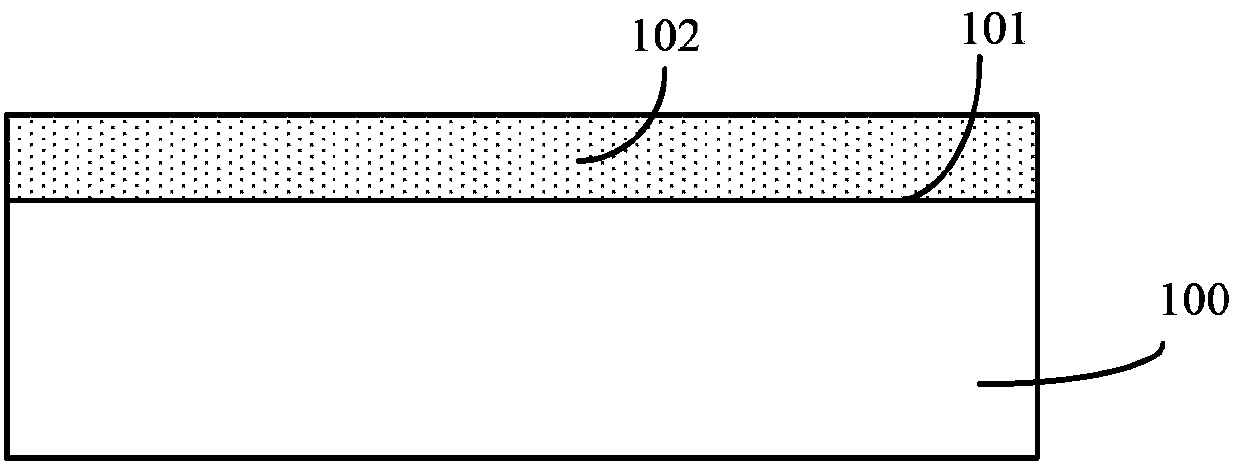

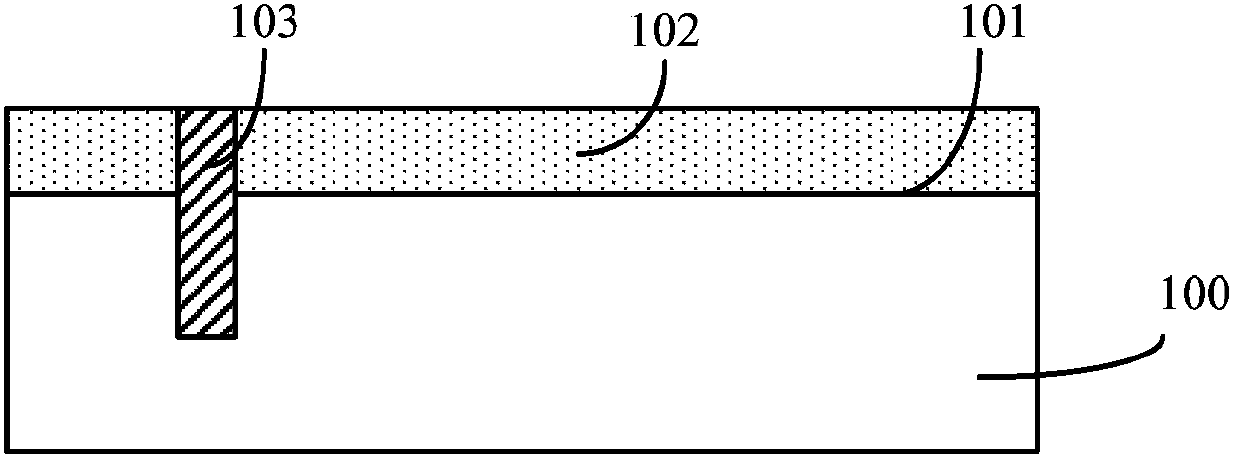

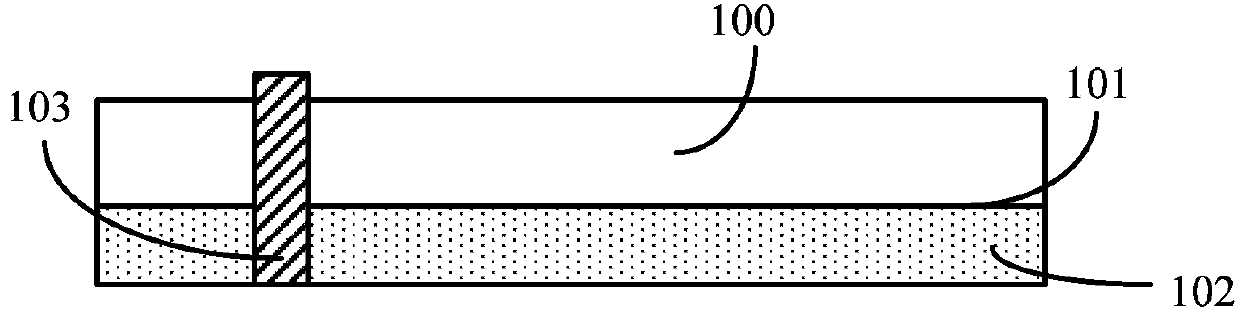

[0032] The inventor of the present invention has discovered through research that the prior art planarizes a silicon substrate 100 (such as image 3 The method of the second surface shown) includes: using a chemical mechanical polishing process to polish the second surface of the silicon substrate until it is close to the conductive plug 103 (such as image 3 As shown); after chemical mechanical polishing, an etching process is used to etch the second surface of the silicon substrate 100 until the conductive plug 103 protrudes from the second surface; however, the position where the chemical mechanical polishing stops It is difficult to control, which will result in over-grinding or incomplete grinding, making it difficult to control the thicknes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More