A packaging structure of a low-k chip and a manufacturing method thereof

A chip packaging structure, low-k technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as fragmentation and integrated circuit failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0043] Embodiment 1. The step of forming TSV holes is performed before the FEOL process. That is, the TSV holes are pre-formed on the substrate before the FEOL process, and the TSV holes are gradually connected to the topmost connection line in the metal layer during the subsequent process. The process includes:

[0044] Provide the substrate before the FEOL process;

[0045] forming TSV holes in the substrate;

[0046] forming a chip on the substrate by FEOL process;

[0047] The metal layer is formed by a BEOL process, and the TSV hole extends to the topmost connection line in the metal layer and is electrically connected to the topmost connection line.

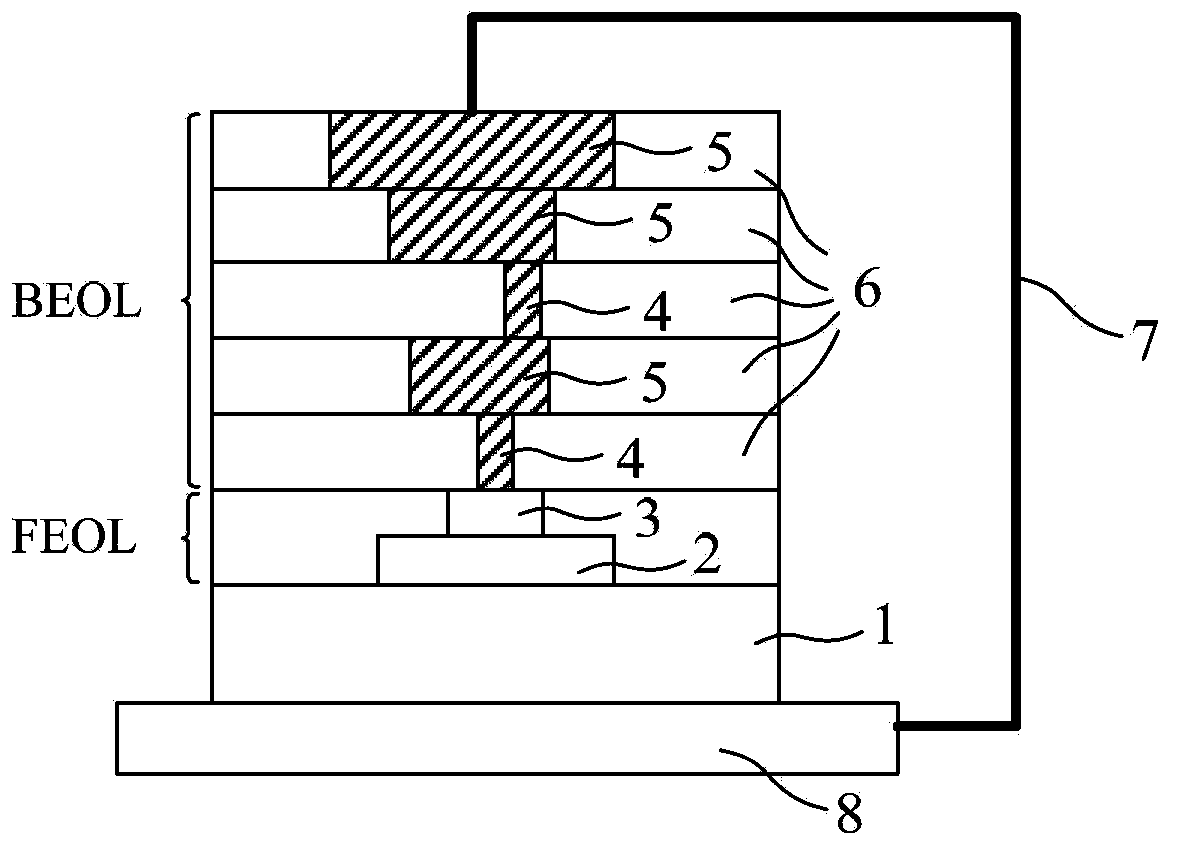

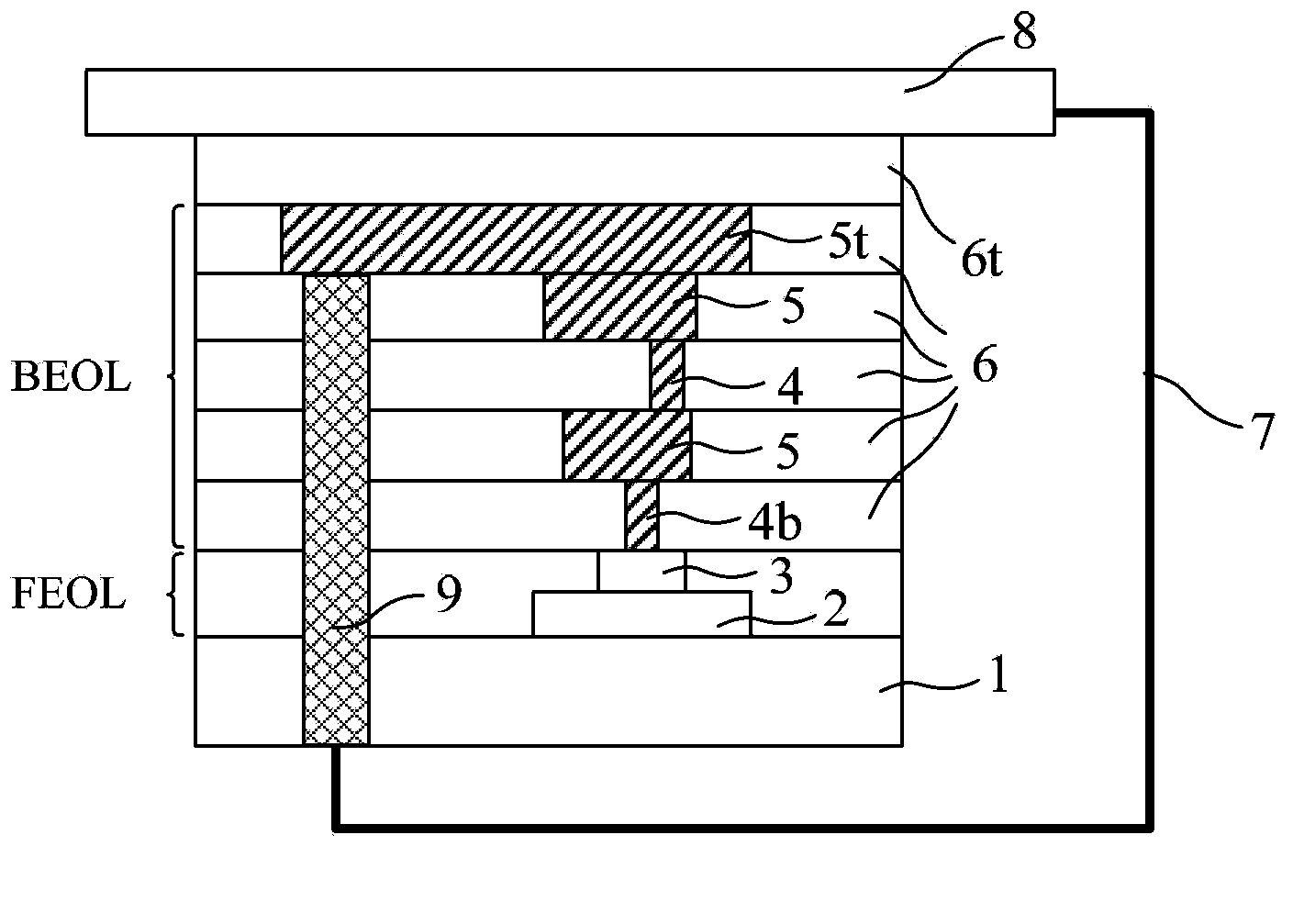

[0048] Please refer to figure 2 The packaging structure of the low-k chip of the present invention is shown. The specific formation process of the TSV holes mentioned above in the first embodiment is as follows.

[0049] First, a substrate 1 is provided.

[0050] Then, the existing TSV hole 9 forming method can be u...

Embodiment 2

[0054] Embodiment 2. The step of forming TSV holes is performed during the FEOL process. That is, TSV holes are formed on the substrate during the FEOL process, and the TSV holes are gradually connected to the topmost connection line in the metal layer in the subsequent process.

[0055] Because the FEOL process consists of multiple processes, such as the formation of STI (Shallow Trench Isolation, shallow trench isolation) in the substrate 1, the formation of wells, and the gate structure in CMOS (Complementary Metal Oxide Semiconductor, Complementary Metal Oxide Semiconductor) devices The formation of the source / drain region and so on. In the second embodiment, the step of forming the TSV hole 9 may be performed between these steps in the FEOL process as required. The formed TSV hole 9 penetrates the substrate 1 . In the subsequent process, it is necessary to pay attention to the treatment of the formed TSV hole 9. For example, when forming an interlayer dielectric layer, ...

Embodiment 3

[0056] Embodiment 3. The step of forming TSV holes is performed after the FEOL process and before the BEOL process. That is, after the FEOL process is completed and before the BEOL process is started, TSV holes are formed on the substrate and the chip layer formed by FEOL, and the TSV holes are gradually connected to the topmost connection line in the metal layer during the subsequent process.

[0057] Take the manufacture of CMOS devices as an example, and refer to figure 2 . First, a chip 2 is formed on the substrate 1. The chip 2 is composed of CMOS devices, which include NMOS (N-Metal-Oxide-Semiconductor, N-type metal oxide semiconductor) and PMOS (P-Metal-Oxide-Semiconductor, P-type Metal Oxide Semiconductor) devices, NMOS includes its gate structure and source / drain, similarly, PMOS includes its gate structure and source / drain. In the structure formed after the FEOL process is completed, there are generally structures such as an interlayer dielectric layer deposited o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More