Wideband sample-and-hold circuit for the front-end of a successive-approximation analog-to-digital converter

A technology of sample-and-hold circuits and analog-to-digital converters, applied in analog/digital conversion, code conversion, instruments, etc., can solve problems such as difficult to meet bandwidth requirements, achieve the goal of improving bandwidth, meeting signal linearity, and saving hardware overhead Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings.

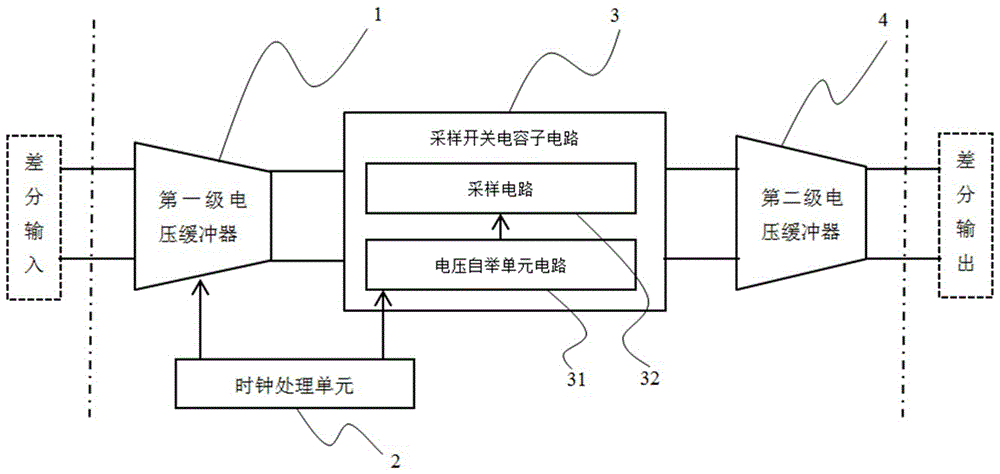

[0028] see figure 1 , a broadband sample-and-hold circuit for the front end of the successive approximation analog-to-digital converter, consisting of a first-stage voltage buffer 1, a clock processing unit 2, a sampling switched capacitor sub-circuit 3, and a second-stage voltage buffer 4; The signal output end of the primary voltage buffer 1 is connected to the signal input end of the sampling switched capacitor sub-circuit 3; the signal output end of the sampling switched capacitor sub-circuit 3 is connected to the signal input end of the second-stage voltage buffer 4; the clock processing unit 2 Provide clock signals to the first-stage voltage buffer 1 and the sampling switched capacitor sub-circuit 3 respectively; the first-stage voltage buffer 1 is responsible for isolating the sampling switched capacitor sub-circuit 3 from the previous stage circuit, r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com