Transistor forming method

A technology of transistors and semiconductors, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems such as poor performance of transistors, achieve better isolation effects, improved and stable performance, and good device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background, the performance of the transistor with the high-K dielectric layer and the metal gate structure in the prior art is not good.

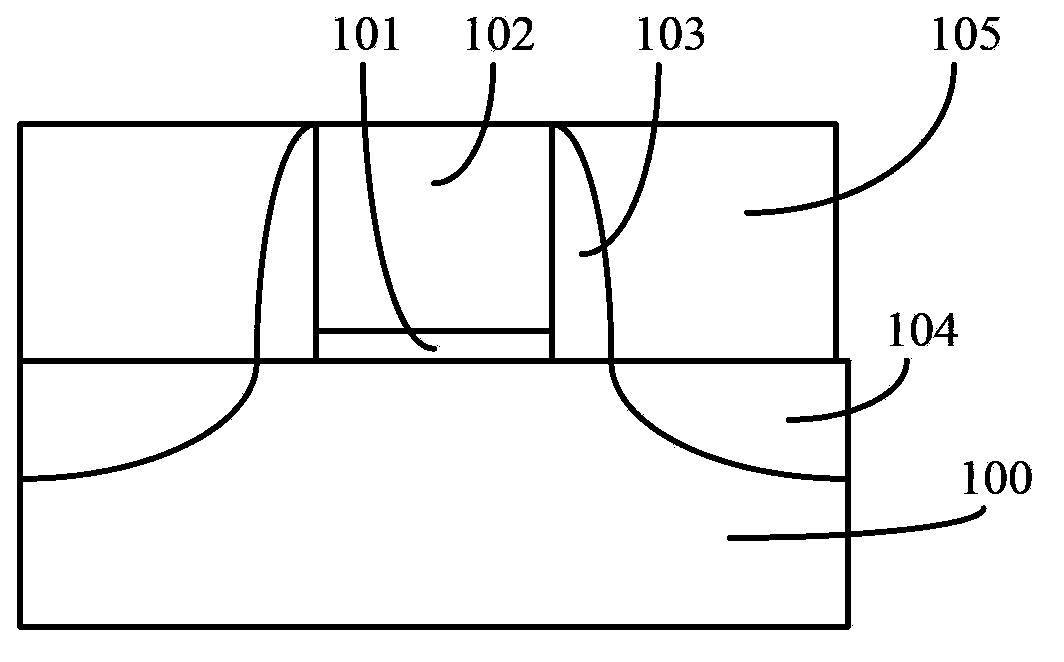

[0033] After research by the inventor of the present invention, please continue to refer to figure 1 , since the material of the metal gate layer 102 is metal, when the transistor is working, the prior art will directly apply an operating voltage to the top surface of the metal gate layer 102; however, directly to the metal gate layer When an operating voltage is applied to the top surface of the metal gate layer 102, the metal on the surface of the metal gate layer 102 will undergo metal electromigration under the action of an operating electric field, resulting in problems such as short circuit, short circuit or unstable performance of the device. In order to prevent the electromigration of metal on the top surface of the metal gate layer 102, the inventors of the present invention have found through research t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More