Technique method for patterning back surface of silicon wafer

A process method and graphic technology, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of restricted processing technology, opacity of metal and silicon wafers, and inability to do backside processes, etc., to achieve reduction The effect of production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

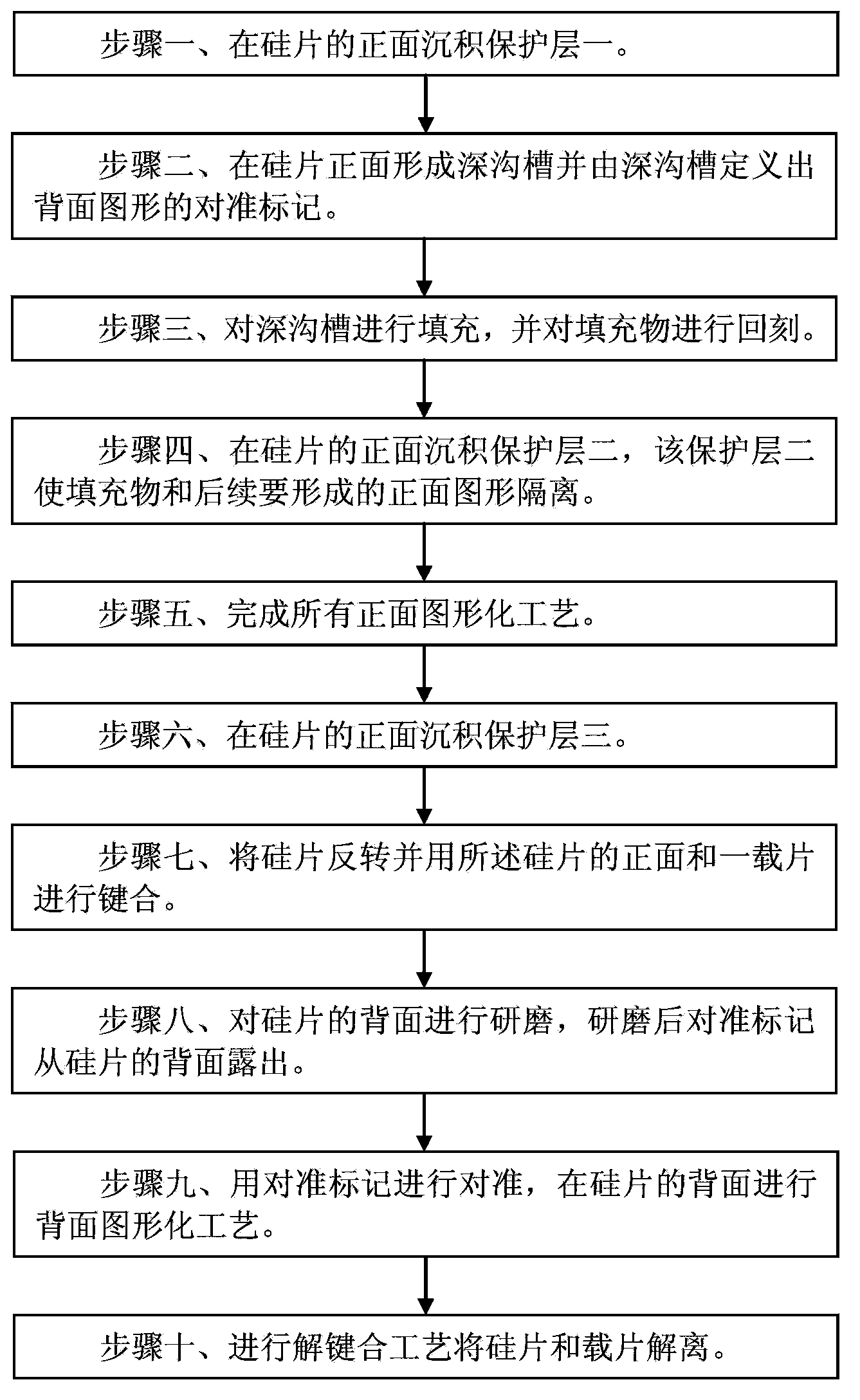

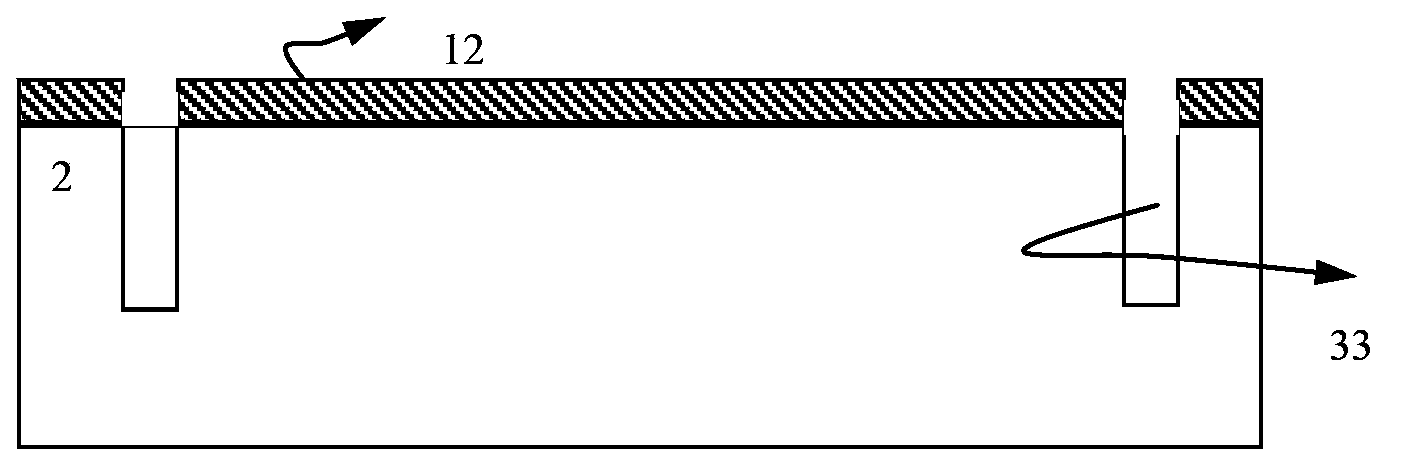

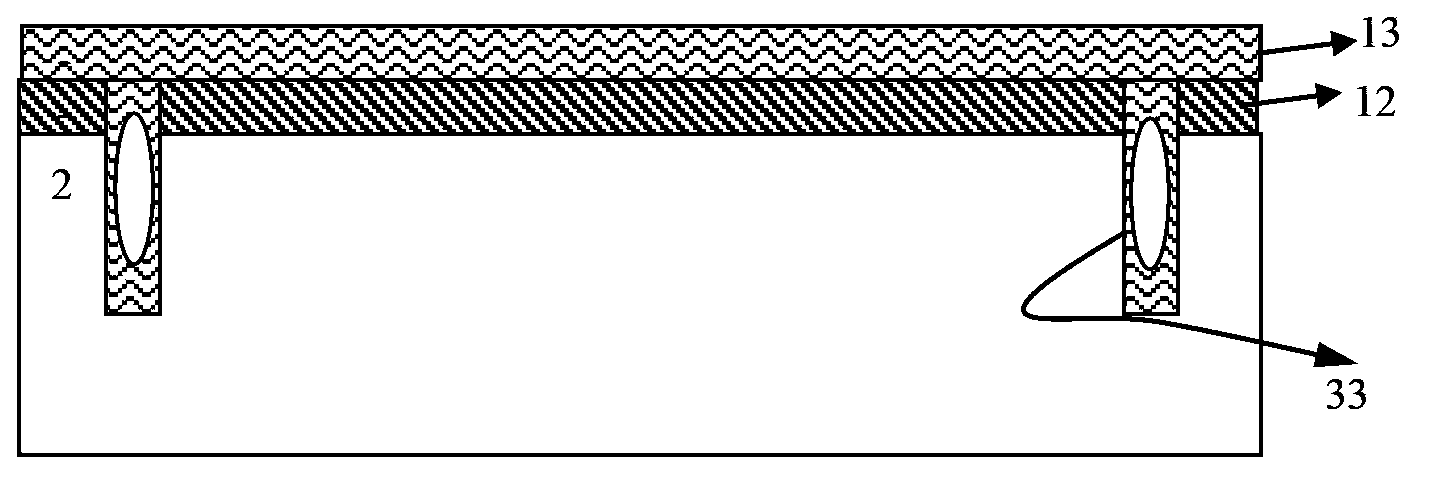

[0040] Such as figure 1 Shown is the flowchart of a method of the embodiment of the present invention; Figure 2A to Figure 2N Shown is a structural diagram of devices in each step of the method of Embodiment 1 of the present invention. In the first method of the embodiment of the present invention, an RC-IGBT with a rated breakdown voltage of about 1200V is taken as an example. The thickness of the silicon wafer 2 required by the device is 80 μm to 100 μm, and the front side of the silicon wafer 2 needs to form an IGBT device. The back side of sheet 2 needs to form a P / N distribution under the IGBT device pattern. Embodiment 1 of the present invention The process method for patterning the back side of a silicon wafer comprises the following steps:

[0041] Step 1, such as Figure 2A As shown, a silicon wafer 2 is provided, and the initial thickness of the silicon wafer 2 is 725 μm. A protective layer 12 is deposited on the front surface of the silicon wafer 2 .

[0042] ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More