A multi-source regulated resistive memory with a multi-layer film structure and its preparation method

A technology of resistive variable memory and multi-layer film, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the lack of semiconductor layer divergence, control the coefficient of electric resistive change, and the influence of MFS structure storage performance. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

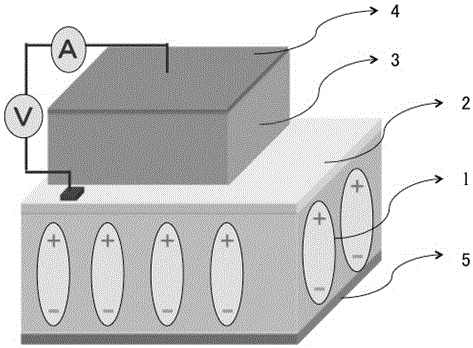

[0035] A multi-source regulated resistive memory with a multilayer film structure (see figure 1 ), including a ferroelectric single crystal substrate 1, a conductive lower electrode 2, a ferroelectric thin film layer or a heterojunction layer 3, an upper electrode thin film layer 4, and a gate electrode layer 5; it is characterized in that: the conductive lower electrode is set on the ferroelectric single crystal Between the substrate and the ferroelectric thin film layer or the heterojunction layer, the upper electrode thin film layer is arranged on the top layer, and the gate electrode layer is on the lowermost layer; the ferroelectric single crystal substrate is PMN-PT; the conductive lower electrode is La x Sr 1-x MnO 3 Manganese oxide, wherein the value of x is 0.1-0.2; the ferroelectric thin film layer or heterojunction layer is BaTiO 3 ; The upper electrode film layer or the gate electrode layer is Pt. The thickness of the ferroelectric single crystal substrate is 0....

Embodiment 2

[0037] A multi-source regulated resistive memory with a multilayer film structure (see figure 1 ), including a ferroelectric single crystal substrate, a conductive lower electrode, a ferroelectric thin film layer or a heterojunction layer, an upper electrode thin film layer, and a gate electrode layer; it is characterized in that: the conductive lower electrode is set on the ferroelectric single crystal substrate and the ferroelectric thin film Between layers or heterojunction layers, the upper electrode thin film layer is placed on the top layer, and the gate electrode layer is placed on the lowermost layer.

[0038] Ferroelectric single crystal substrate of the present invention is PMN-PT; Described conductive lower electrode is La x Ca 1-x MnO 3 Manganese oxide, wherein the value of x is 0.1-0.2; the ferroelectric thin film layer or heterojunction layer is BiFeO 3 Ferroelectric film; said upper electrode film layer or gate electrode layer is Au or Al. The thickness of t...

Embodiment 3

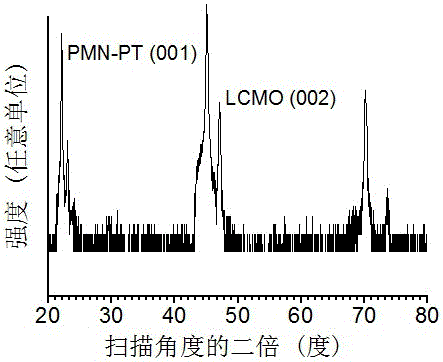

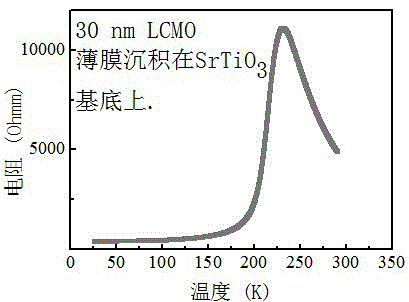

[0040] The structure of the transparent conductive oxide thin film with multi-layer film structure is: the substrate PMN-PT, the thickness is 0.5mm; the lower electrode layer is La 0.8 Ca 0.2 MnO 3 , with a thickness of 30nm; the thickness of the ferroelectric BTO film layer is 300nm; the thickness of the upper electrode layer Pt is 500nm; the thickness of the Ag gate electrode layer is 500nm. The deposition temperatures of the three-layer films are 750°C, 800°C and room temperature respectively, and the gases used in the deposition are O 2 (60Pa), O 2 (10Pa) and Ar gas (0.02Pa). figure 2 Shows BTO / La 0.8 Ca 0.2 MnO 3 / PMN-PT structure X-ray diffraction (XRD) patterns. The prepared samples were heated at 500 °C and high-purity O 2 Annealed under flow protection for 2 hours. The Ag gate electrode layer is prepared by thermal evaporation in a high vacuum chamber at room temperature.

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More