Transistors and methods of forming them

A technology of transistors and semiconductors, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems that transistors cannot meet, limit the application range of transistors, complex technical requirements, etc., and achieve the effect of size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

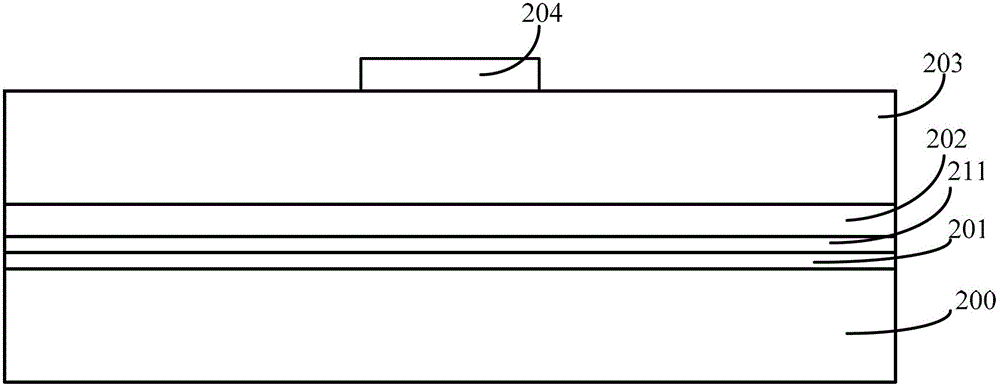

[0043] Figure 2 to Figure 9 is a schematic cross-sectional structure diagram of the formation process of the transistor described in the first embodiment of the present invention.

[0044] Please refer to figure 2 , providing a semiconductor substrate 200, forming a gate dielectric film 201 on the surface of the semiconductor substrate 200; forming a first work function film 202 on the surface of the gate dielectric layer film 201; forming a dummy film 202 on the surface of the first work function film 202 A gate film 203 ; a sacrificial layer 204 is formed on the surface of the dummy gate film 203 .

[0045] The semiconductor substrate 200 is used to provide a working platform for subsequent processes; the semiconductor substrate 200 is a silicon substrate, a silicon-germanium substrate, a silicon carbide substrate, a silicon-on-insulator (SOI) substrate, a germanium-on-insulator (GOI) ) substrate, glass substrate or III-V compound substrate (such as gallium arsenide, etc...

no. 2 example

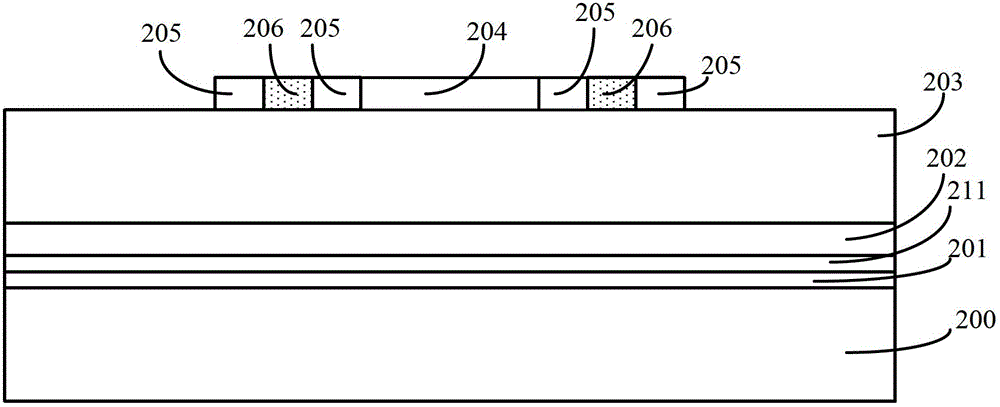

[0086] The difference between the second embodiment and the first embodiment is that in the first embodiment Figure 5 On the basis of removing the second mask layer, and retaining the first mask layer as a mask for etching the first work function layer, the details are as follows.

[0087] exist Figure 5 basis, please refer to Figure 10 , after forming the dielectric layer 207, remove the second mask layer 205 (such as Figure 5 shown); after removing the second mask layer 205, the dummy gate layer 203a and the first work function layer 202a are etched using the dielectric layer 207 and the remaining first mask layer 206 as masks.

[0088] In this embodiment, the second mask layer 205 is removed, and the first mask layer 206 is retained, and then the regions on both sides of the first work function layer 202a can be etched away, and the middle region of the first work function layer 202a is retained; Subsequent formation of the second work function layer can make the wor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More