A method for detecting the quality of through-silicon vias

A quality inspection method and through-silicon via technology, applied in semiconductor/solid-state device testing/measurement, electrical components, circuits, etc., can solve problems such as difficult to find defects, scan speed limits the detection scale, and fails to automatically record defect-related data. , to achieve the effect of improving the yield rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

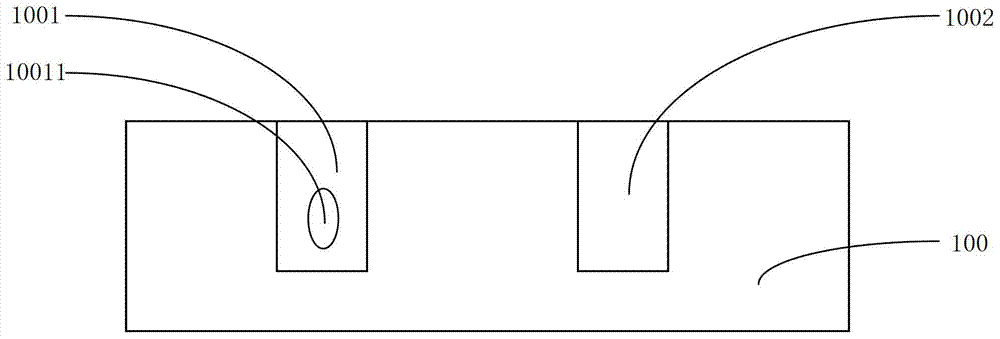

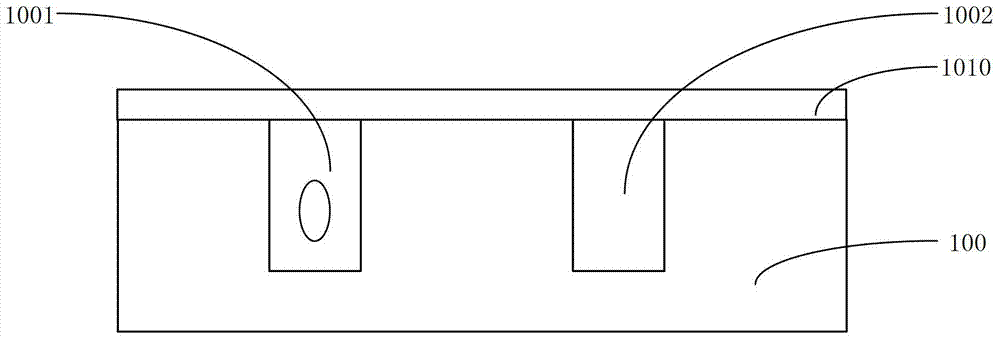

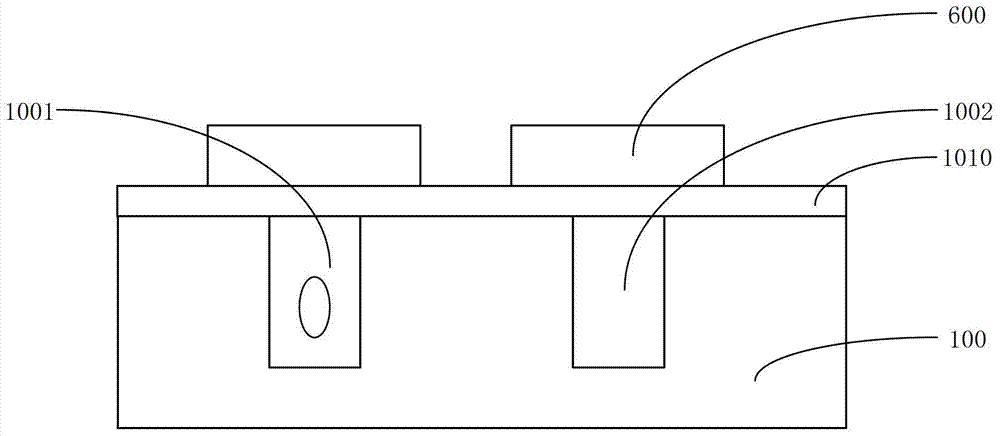

[0069] Below, refer to Figure 1A-Figure 1F and image 3 The detailed steps of the TSV quality detection method proposed in Embodiment 1 of the present invention will be described below. in, Figure 1A-Figure 1F It shows a schematic cross-sectional view of the graphics formed in the relevant steps of a TSV quality detection method proposed in Embodiment 1 of the present invention; image 3 It is a flowchart of a TSV quality detection method proposed by the present invention.

[0070] The TSV quality detection method proposed in the embodiment of the present invention specifically includes the following steps:

[0071] Step a1: providing a semiconductor device 100 formed with a through-silicon via (TSV), the upper surface of the through-silicon via (TSV) is in the same plane as the upper surface of the semiconductor device, such as Figure 1A shown.

[0072] Exemplarily, the semiconductor device 100 includes TSVs 1001 and 1002 , and the TSV 1001 includes a cavity 10011 . T...

Embodiment 2

[0099] Below, refer to Figure 2A-Figure 2G and image 3 The detailed steps of the TSV quality detection method proposed in the second embodiment of the present invention will be described. in, Figure 2A-Figure 2G It shows a schematic cross-sectional view of the graphics formed in the relevant steps of a TSV quality detection method proposed in Embodiment 2 of the present invention; image 3 It is a flowchart of a TSV quality detection method proposed by the present invention.

[0100] The TSV quality detection method proposed in the embodiment of the present invention specifically includes the following steps:

[0101] Step b1: providing a semiconductor device 200 formed with a through-silicon via (TSV), the upper surface of the through-silicon via (TSV) is in the same plane as the upper surface of the semiconductor device, such as Figure 2A shown.

[0102] Exemplarily, the semiconductor device 200 includes TSVs 2001 and 2002 , and the TSV 2001 includes a cavity 20011 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More