Multi-chip package structure

A packaging structure, multi-chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of difficulty in pulling out electroplating wires, easy crosstalk of signals, increased processing costs, etc., to achieve easy internal routing design, reduce The difficulty of packaging process and the effect of ensuring signal integrity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be described in detail below in conjunction with various embodiments shown in the drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

[0026] Please refer to Figure 2 to Figure 7 Shown is a preferred embodiment of the multi-chip package structure 100 of the present invention.

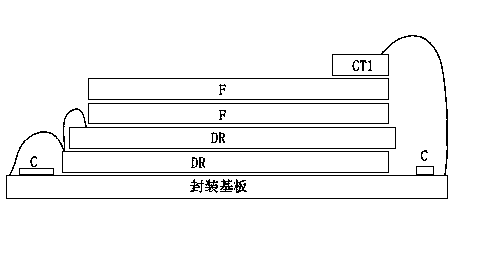

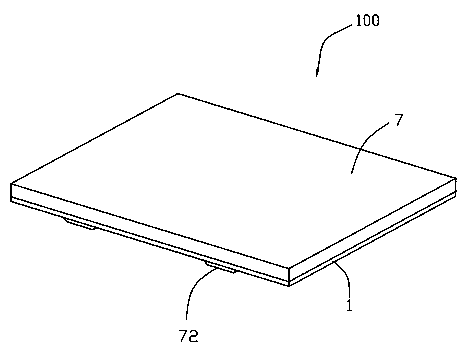

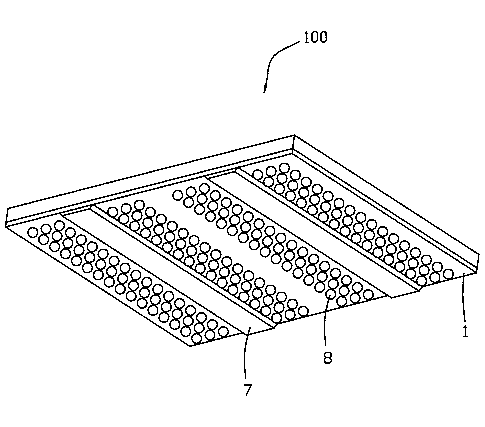

[0027] The multi-chip package structure 100 includes a substrate 1, two DRAM chips 2, a second chip 3, a circuit adapter board 4, a third chip 5, several capacitors and resistors 6, several bonding wires, a package body 7 and several tin Ball 8.

[0028] Please refer to Figure 6 and Figure 7 As shown, the substrate 1 is provided with a first surface 11 and a second surface 12 opposite to each other, a number of wires (not shown) arranged on the first surface 11 and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com