Epilepsy state closed-loop control experiment platform based on FPGA

An epileptic state and closed-loop control technology, applied in the field of biomedical engineering, can solve problems such as low precision, imperfect man-machine interface, and difficult analysis of FPGA hardware neuron network operation, so as to improve operability, flexibility, The effect of portable hardware experiment platform

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

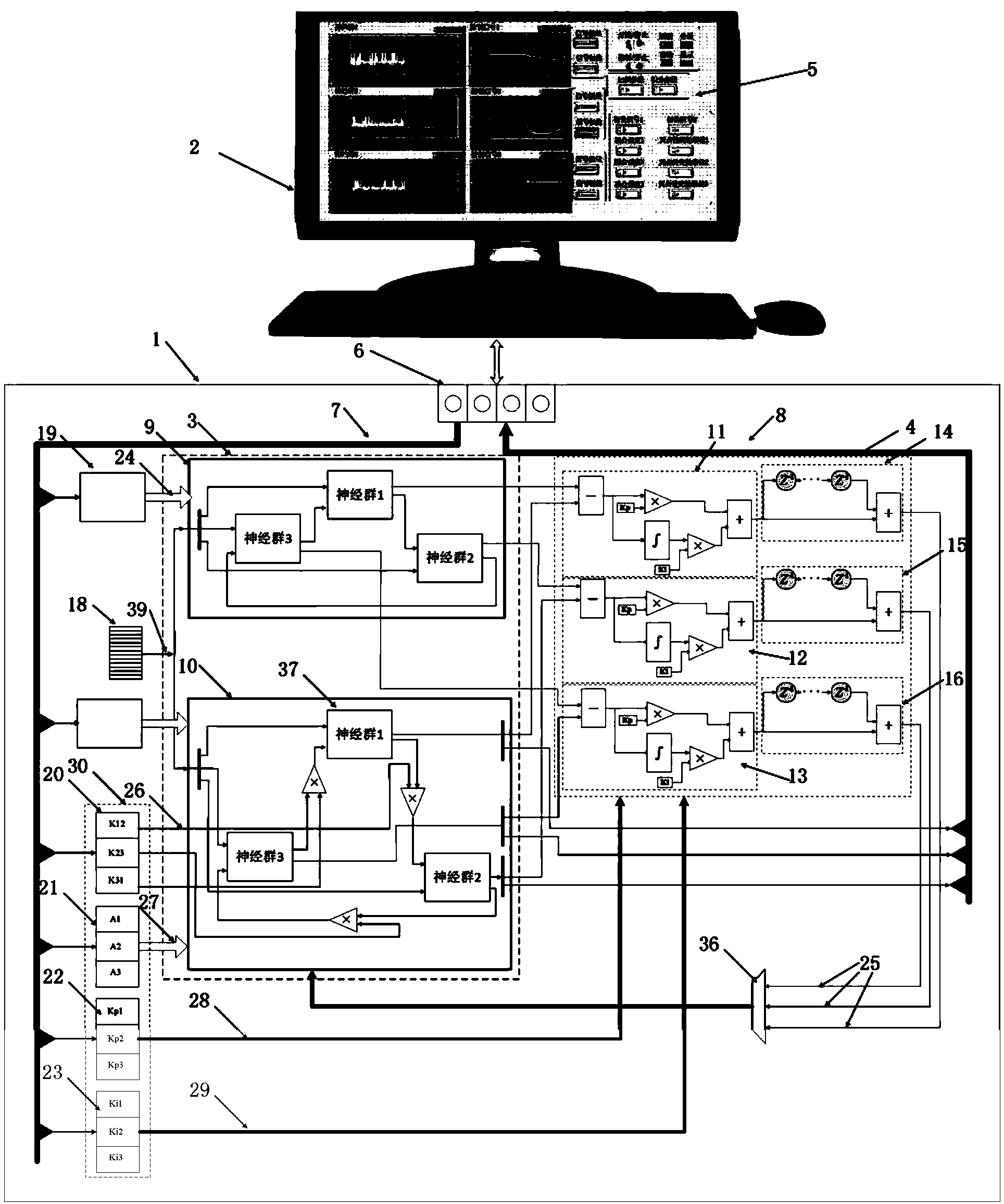

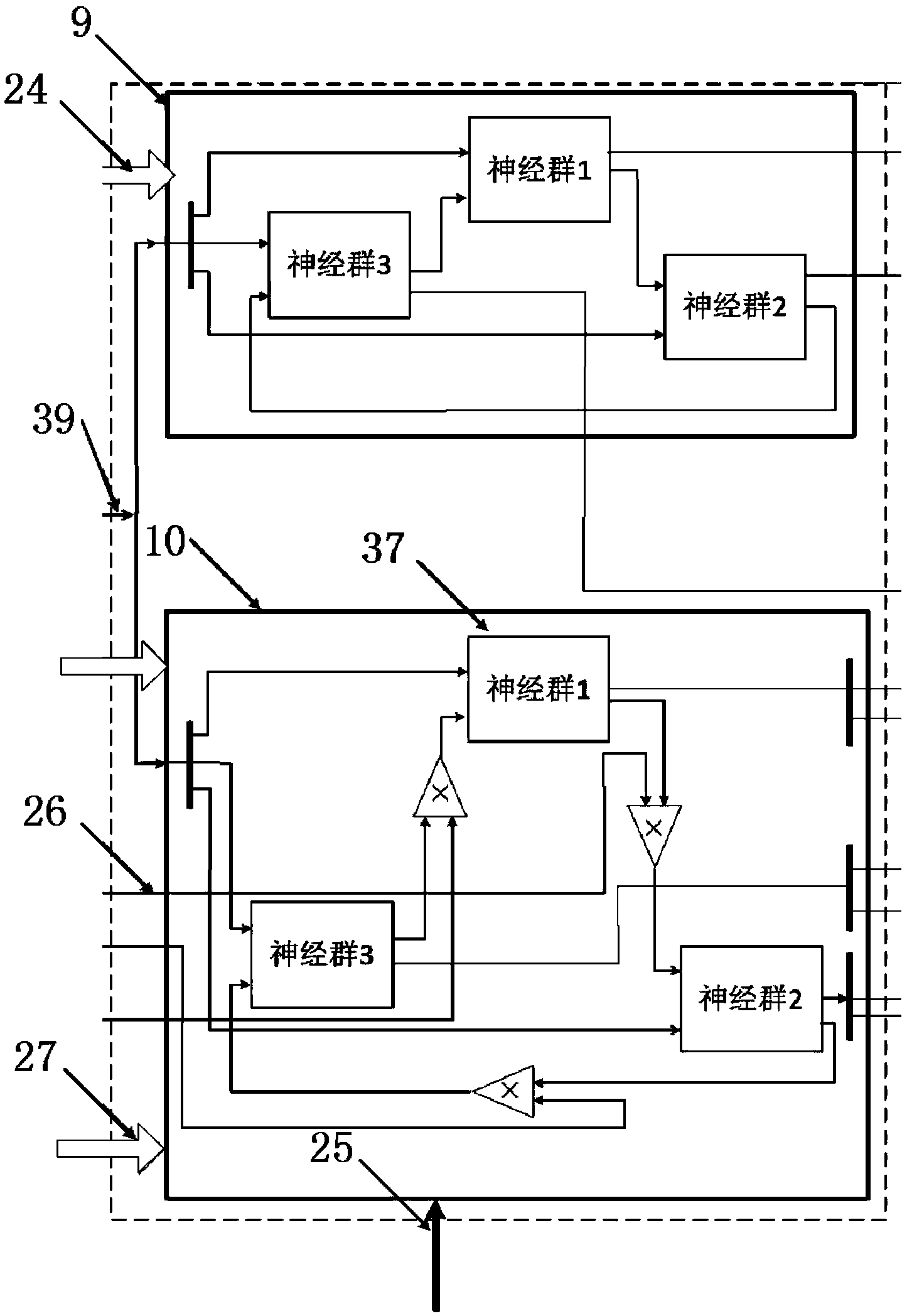

[0021] The closed-loop control FPGA experimental platform structure of the epilepsy neural cluster network of the present invention will be described below in conjunction with the accompanying drawings.

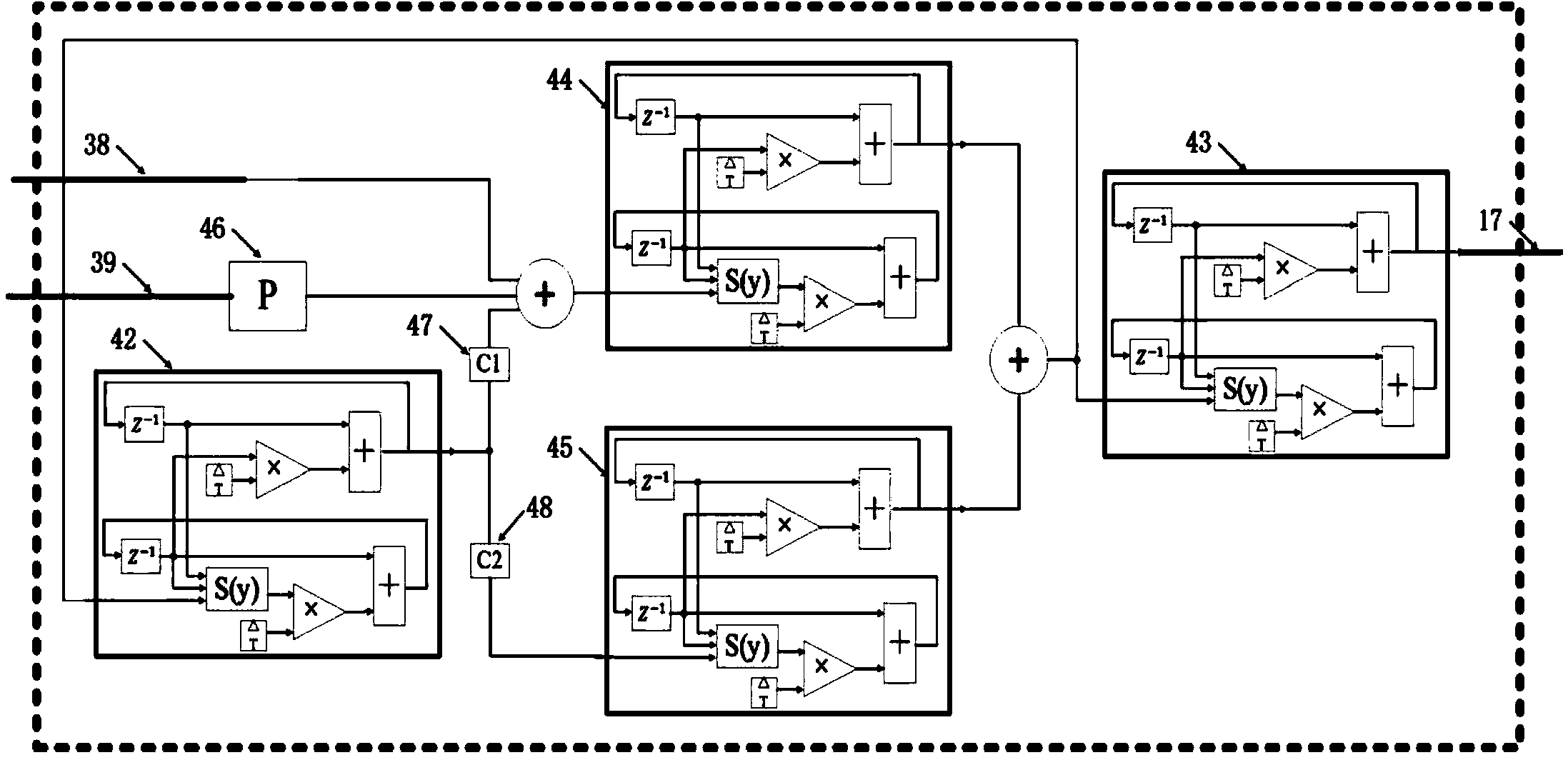

[0022] The design idea of the closed-loop control FPGA experimental platform of the epilepsy neural cluster network of the present invention is to first set up an epilepsy neural cluster network model with multiple neural clusters and complex coupling on the FPGA; then design PI type iterations independently of the neural cluster network model on the FPGA Learning controller, PI type iterative learning control signal is applied to the model as an external current stimulus, and the pathological discharge mode of the epileptic neural cluster network is changed through stimulation to make it produce normal discharge; finally, the software interface of the host computer is designed, and the software interface of the host computer is set by setting parameters And transmit it to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More