Method for preparing a plasma nitrided gate dielectric layer

A gate dielectric layer, plasma nitridation technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the equivalent thickness of oxide cannot be reduced, gate leakage cannot be effectively reduced, and device reliability cannot be reduced. problems, to achieve the effect of reducing leakage current density, increasing nitrogen content, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The specific implementation manner of the present invention will be described in more detail below with reference to schematic diagrams. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

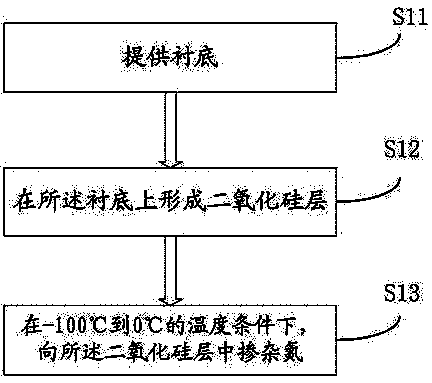

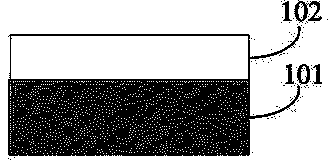

[0032] The invention provides a method for preparing a plasma nitride gate dielectric layer, such as figure 1 As shown, it is a schematic flow chart of a method for preparing a plasma nitrided gate dielectric layer according to an embodiment of the present invention, Figure 2 ~ Figure 4 It is a schematic diagram of the structure formed by preparing the plasma nitrided gate dielectric layer according to the above process in the embodiment of the present invention.

[0033] Specifically include the following ste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More