Crystal lattice dislocation detecting method

A dislocation and lattice technology, applied in the field of integrated circuit design, can solve problems such as electrical failure and find the location of dislocations, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

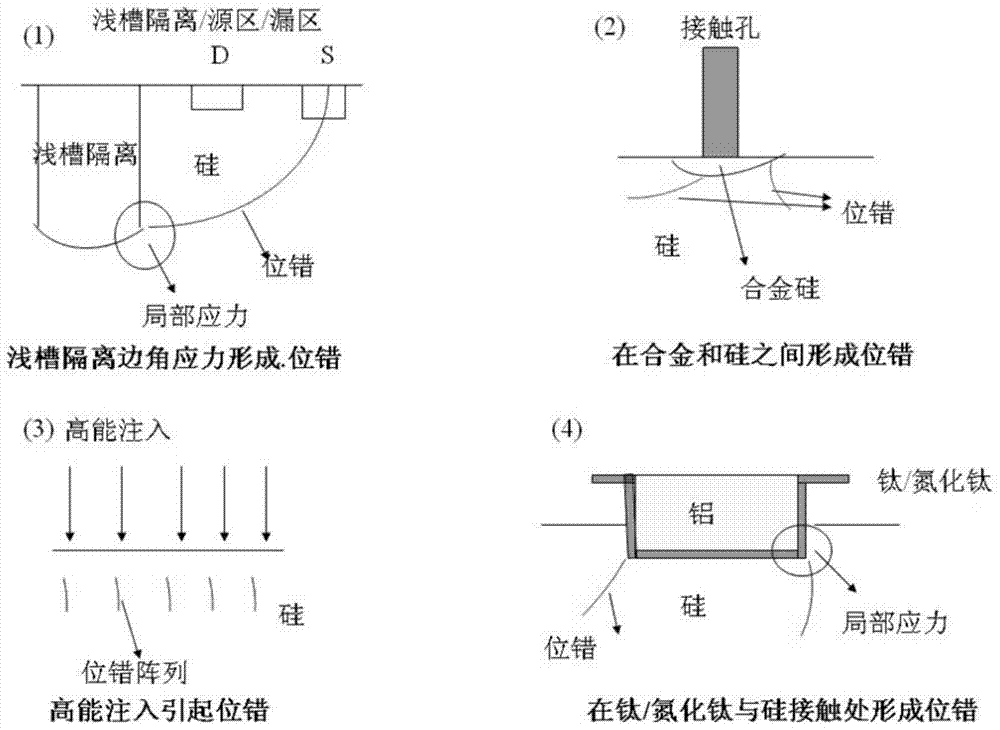

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The method for detecting lattice dislocations described in the present invention comprises the following steps:

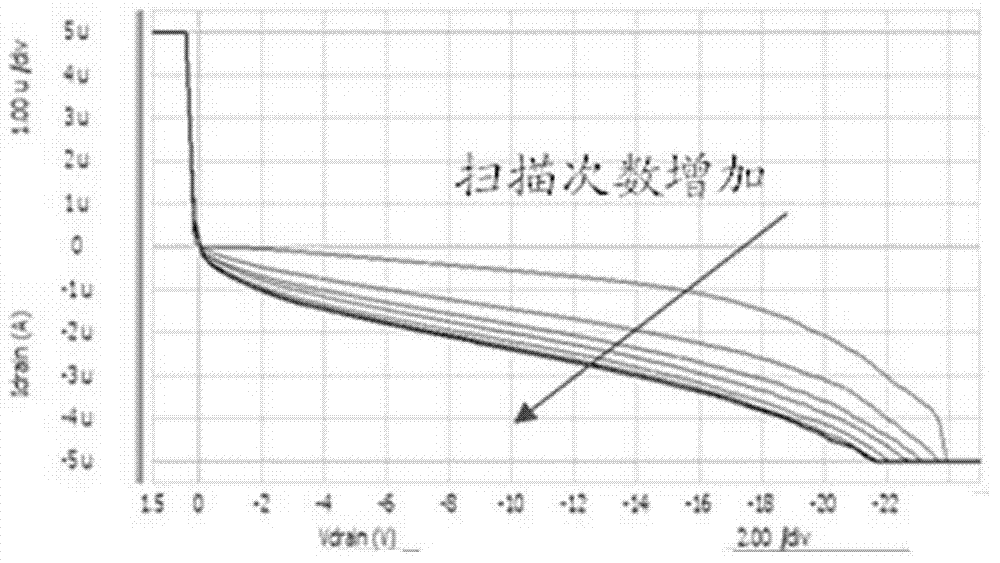

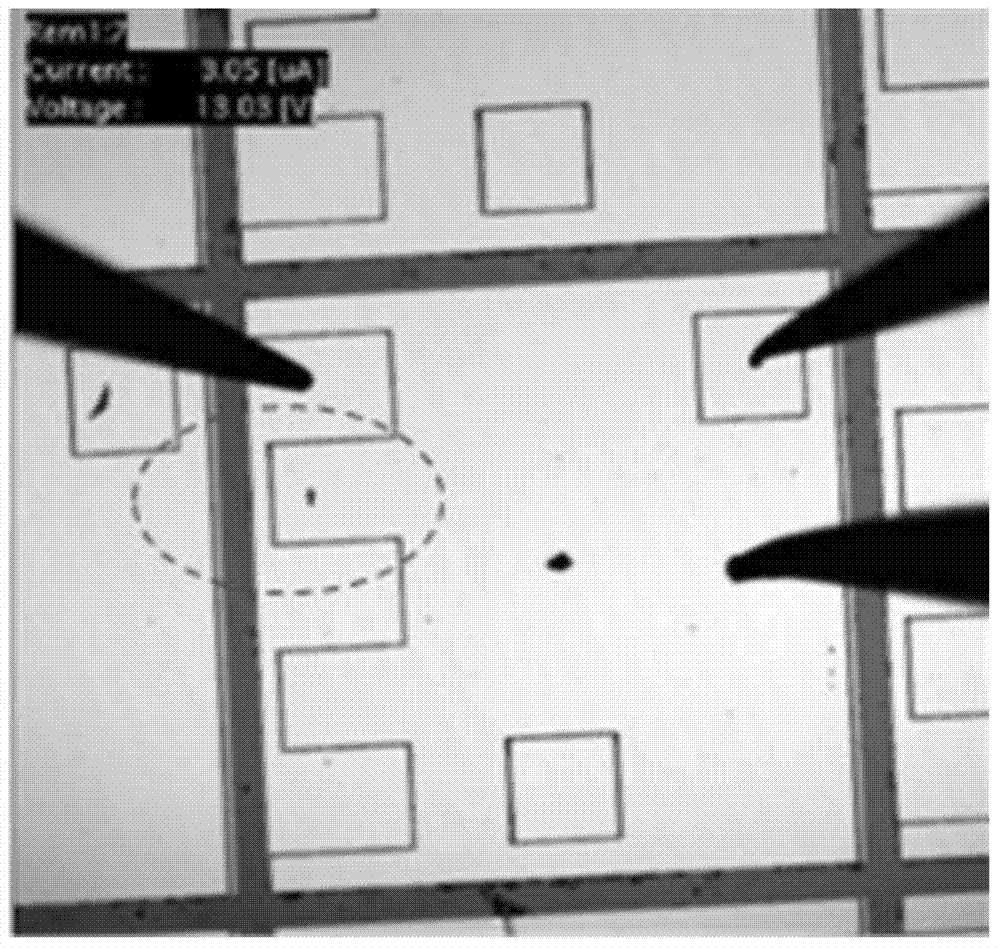

[0021] The first step is to select failed devices for electrical testing, such as MOS tubes, diodes, triodes, memory tubes, etc. The voltage-current curve was measured by multiple scans. If it is a storage tube that cannot measure the voltage-current curve, read the current of the storage tube multiple times to detect changes in the current. Observe whether the voltage-current curve (storage tube is the current curve, the same below) obtained by multiple scans gradually becomes larger or smaller, such as figure 2 The voltage-current curve shown is for a pLDMOS I dss Taking failure analysis as an example, the curves obtained by scanning multiple measurements are different and have changed.

[0022] The second step is to bake the failed device and re-measure its voltage-current curve several times to observe whether it gradually becomes larger or smaller. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com