Patents

Literature

54results about How to "Improve the efficiency of failure analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

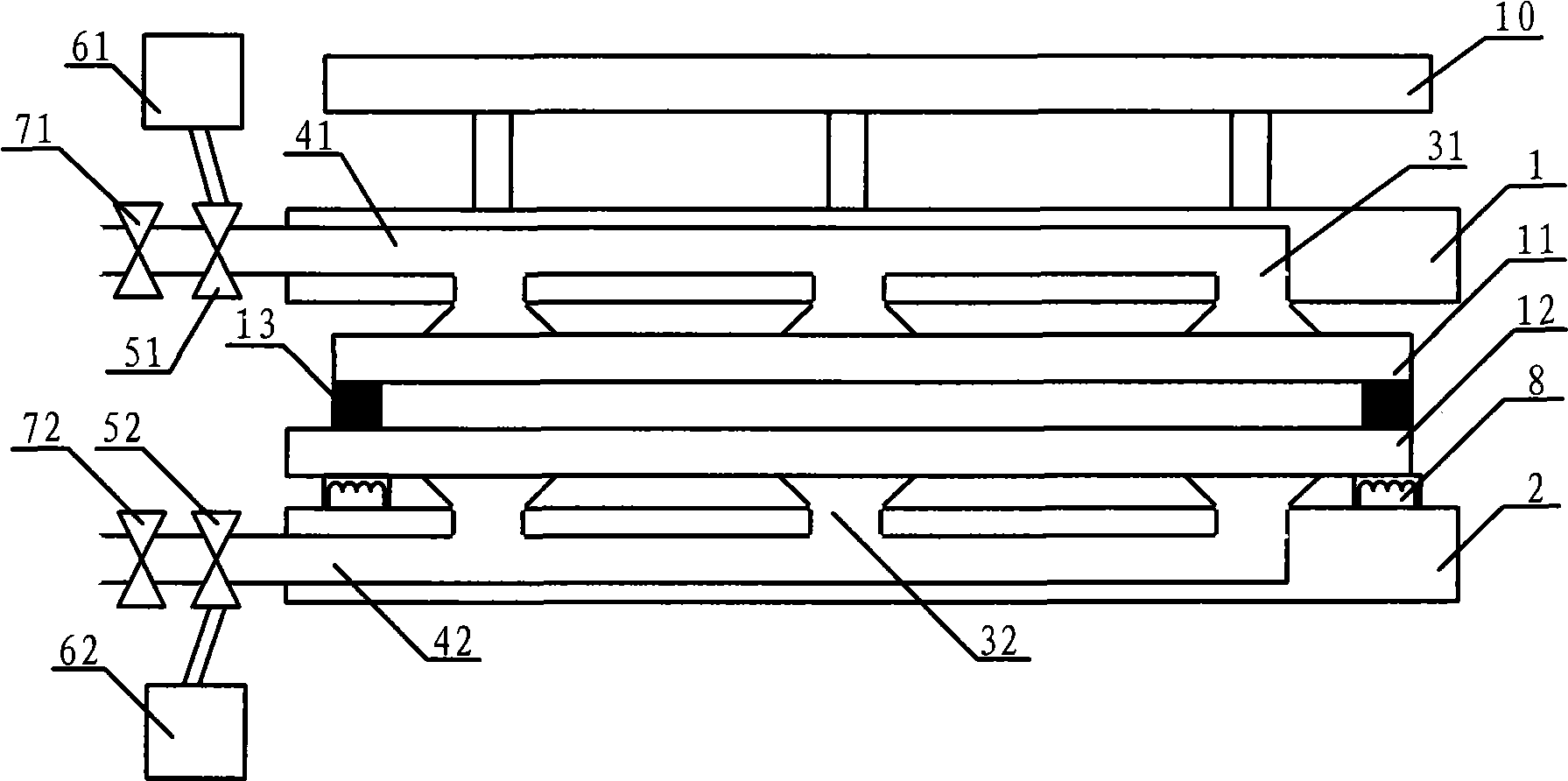

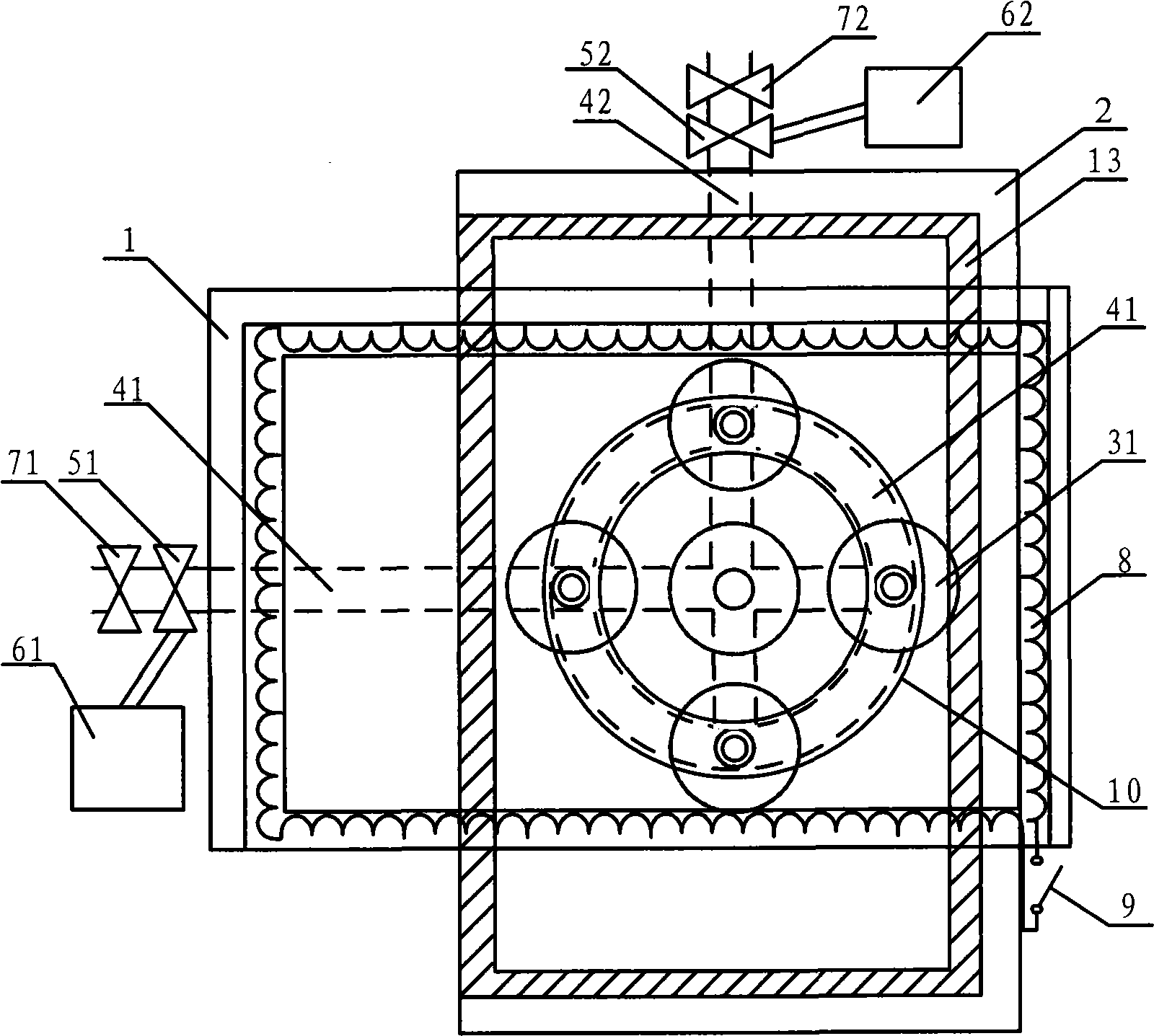

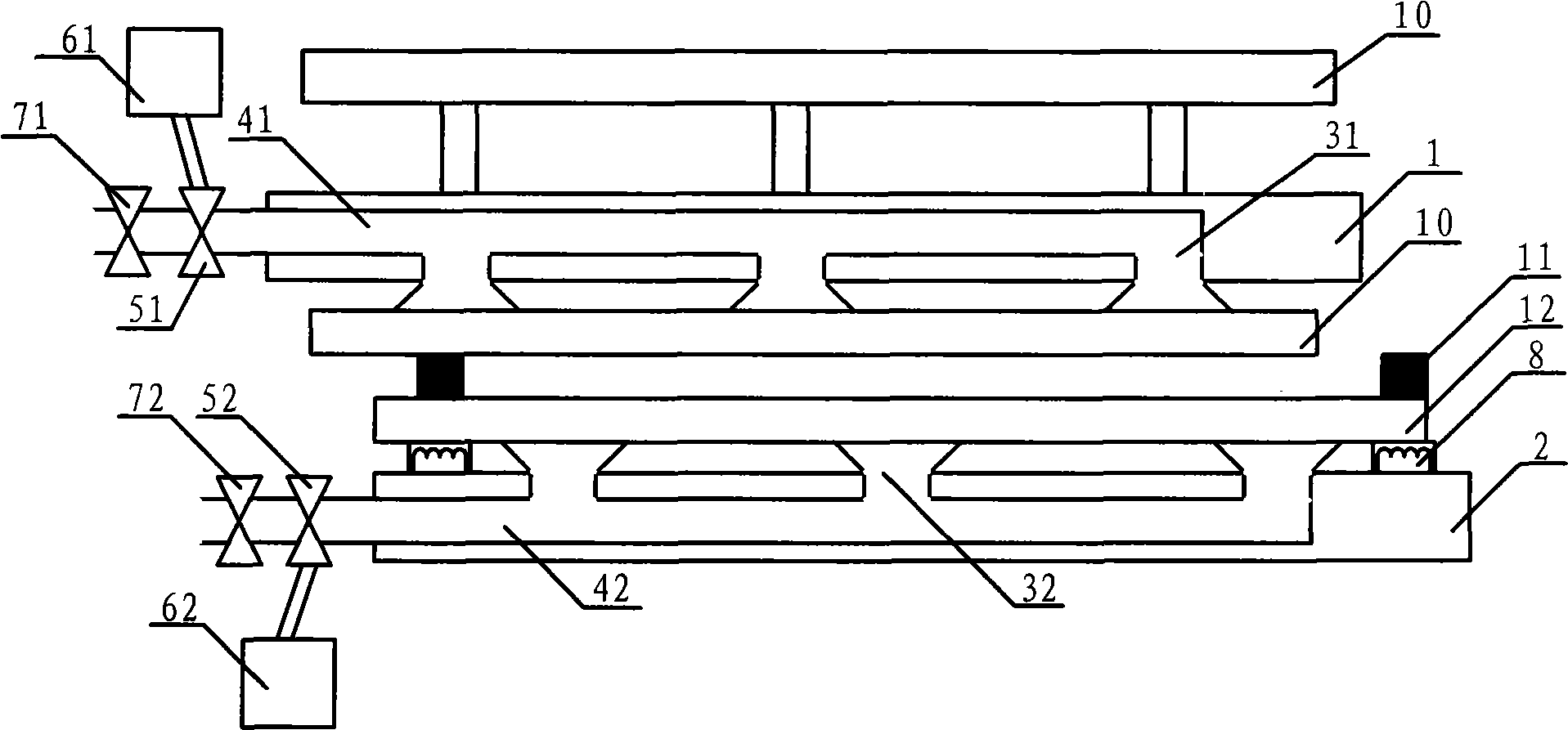

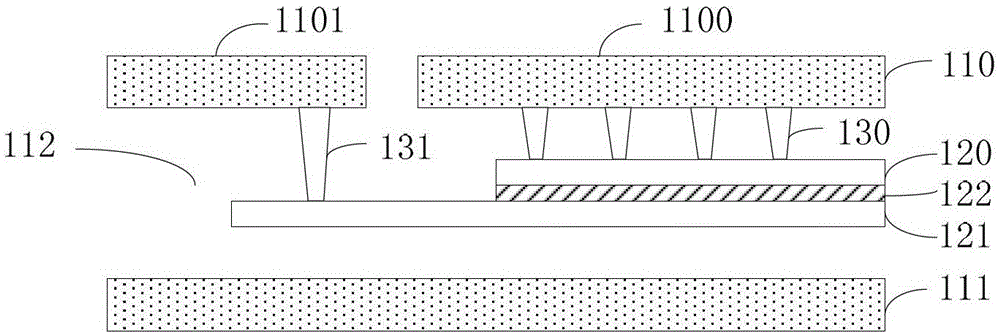

Screen detaching device for LCD

InactiveCN101487933AReduce labor intensityShorten the screen teardown timeNon-linear opticsElectrical componentsLiquid-crystal displayEngineering

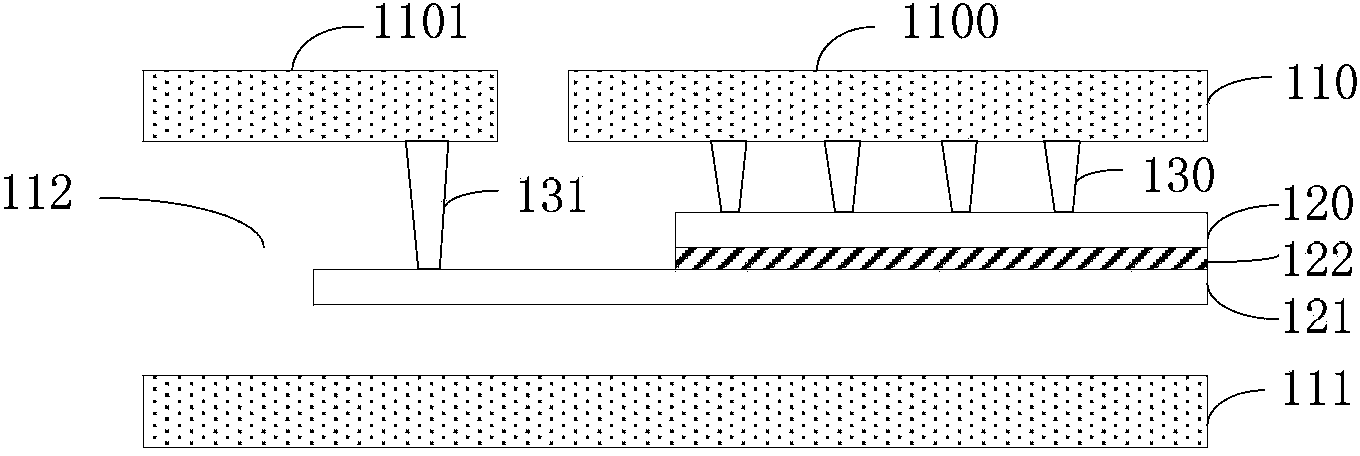

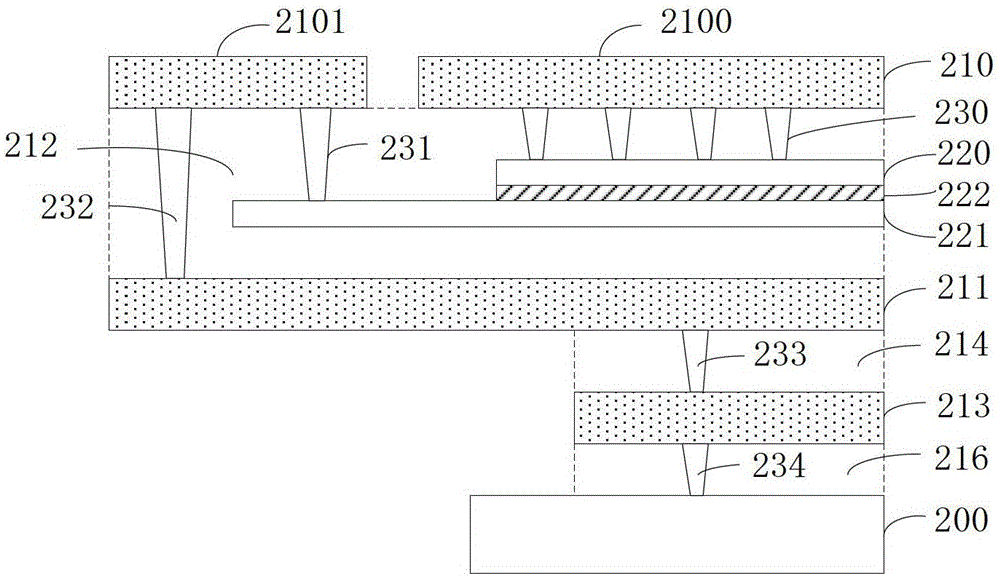

The invention relates to a liquid crystal display screen splitter, comprising an upper board, a lower board, at least two absorption devices, a vacuum pump and a heating element; wherein the upper board and the lower board are provided with breathing pipes, the absorption devices are respectively arranged on the breathing pipes of the upper board and the lower board and used for fixing the liquid crystal display screen, the vaccum pump is connected with the absorption devices by the breathing pipes and used for vaccum suction on the absorption devices, and the heating element is arranged on the lower board and / or the upper board and used for heating glue for sealing the frame of the liquid crystal display screen. The invention has simple structure and low cost, and can efficiently split the liquid crystal display screen with less labor.

Owner:BOE TECH GRP CO LTD +1

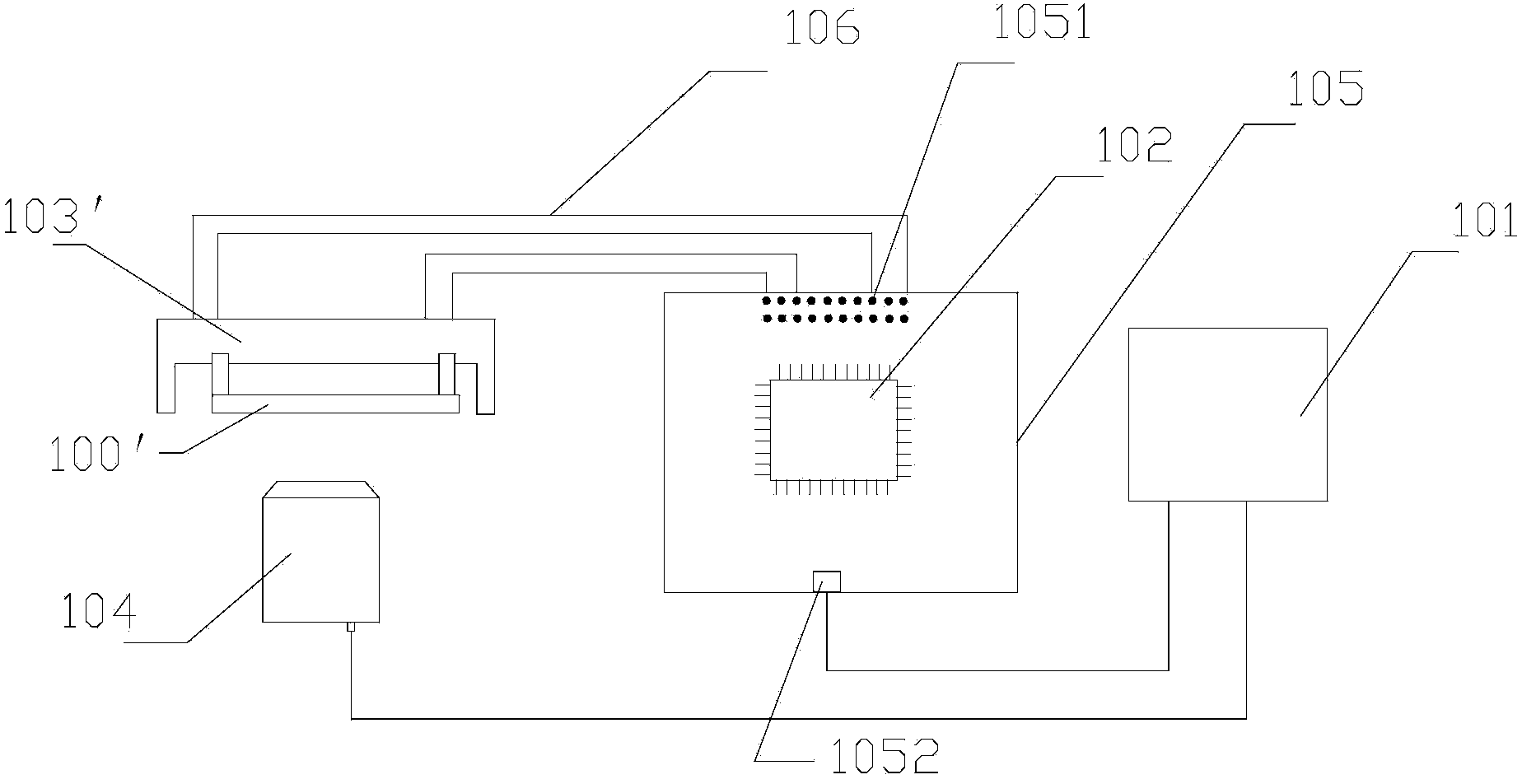

Failure analysis system

InactiveCN104049199APerformance is not affectedImprove the efficiency of failure analysisElectronic circuit testingMicrocomputerMicrocontroller

The invention discloses a failure analysis system, and relates to the technical field of integrated circuit failure analysis. According to the failure analysis system, a testing process and testing conditions are written in a single-chip microcomputer, and then the single-chip microcomputer is used for controlling and realizing dynamic hotspot analysis of a chip, wherein the dynamic hotspot analysis process comprises various loop tests including a power source short circuit test, various electric leakage tests, a functional test and the like. In this way, a testing machine does not need to be moved frequently, and the performance of the testing machine will not be affected.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

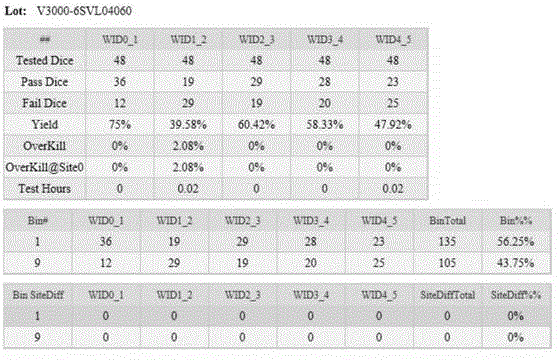

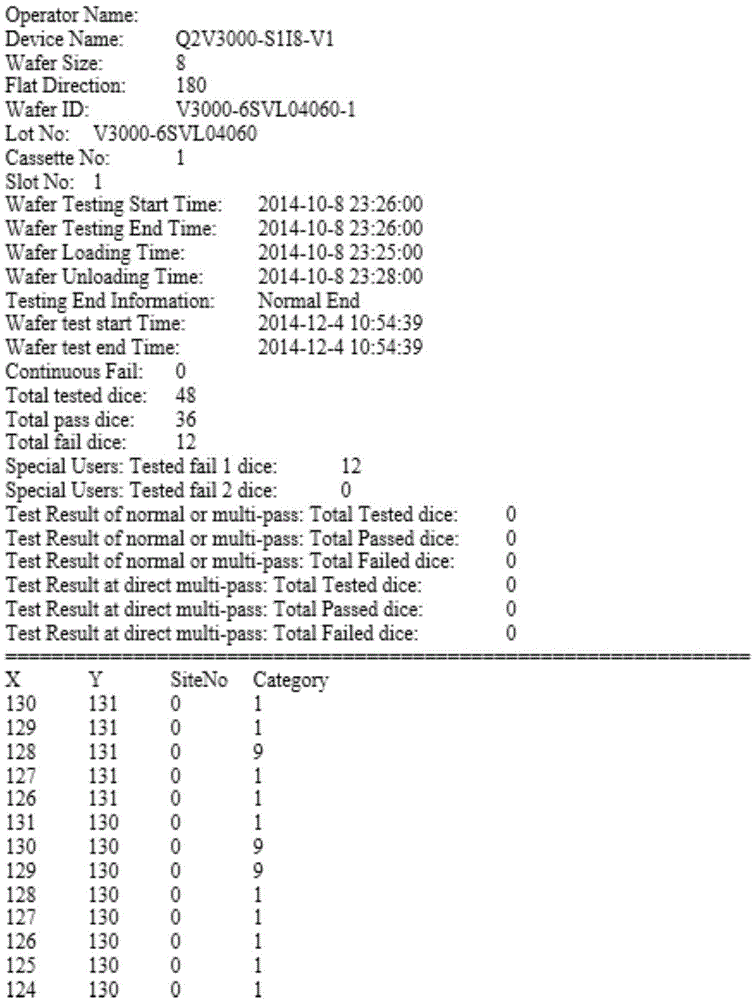

Data depth traceability test method

ActiveCN104597392AImprove the efficiency of failure analysisNormal Data Analysis EfficiencyElectronic circuit testingSpecific testRelevant information

The invention provides a data depth traceability test method. The method comprises the steps of: timely acquiring relevant information of a product to be tested from a server; reading the information acquired from the server by regular expression, performing stored storing on key information in the information, and drawing a yield rate drawing; and according to the yield rate drawing, acquiring the yield rate of the product to be tested, the failure distribution, specific failure information of a failure chip on the product to be tested, and specific information of the chip passing the test on the product to be tested. The key information related to the product to be tested is subject to stored storing by regular expression, the yield rate drawing is drawn, and an engineer can visually know the yield rate and the failure distribution of the product to be tested according to the yield rate drawing; the specific failure information of the failure chip on the product to be tested can be acquired, and the efficiency of failure analysis is improved; and the specific test information of the chip passing the test can be acquired, and the normal data analysis efficiency is improved.

Owner:SINO IC TECH

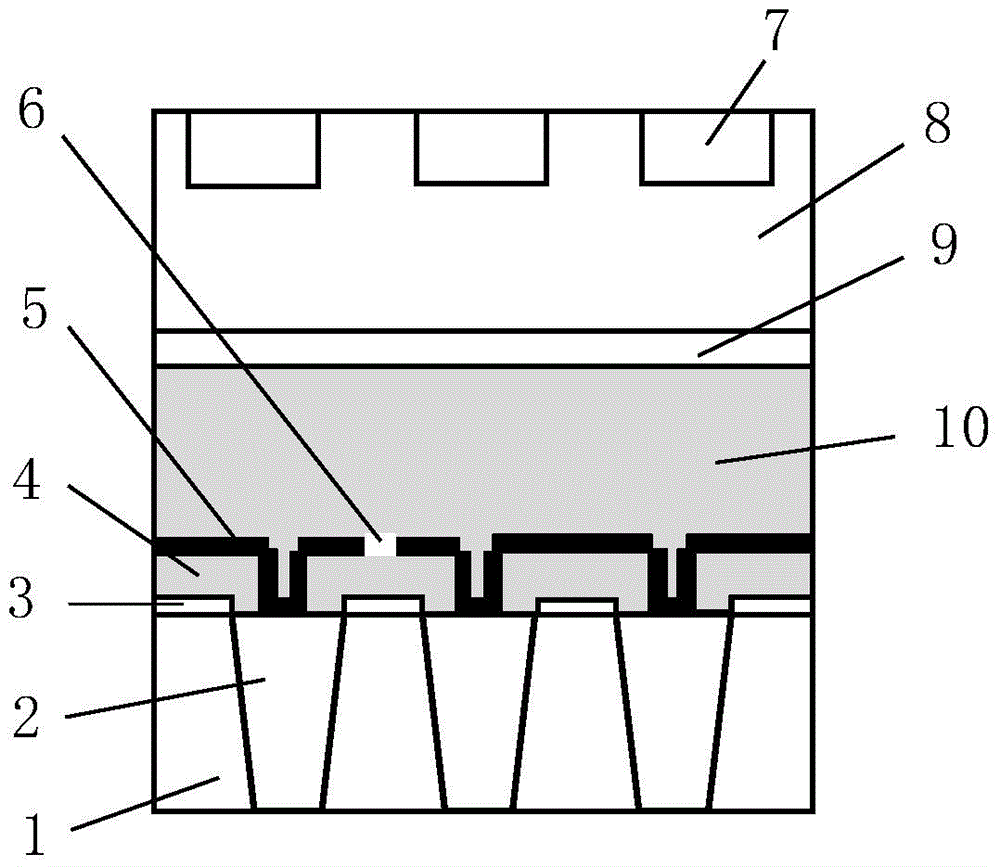

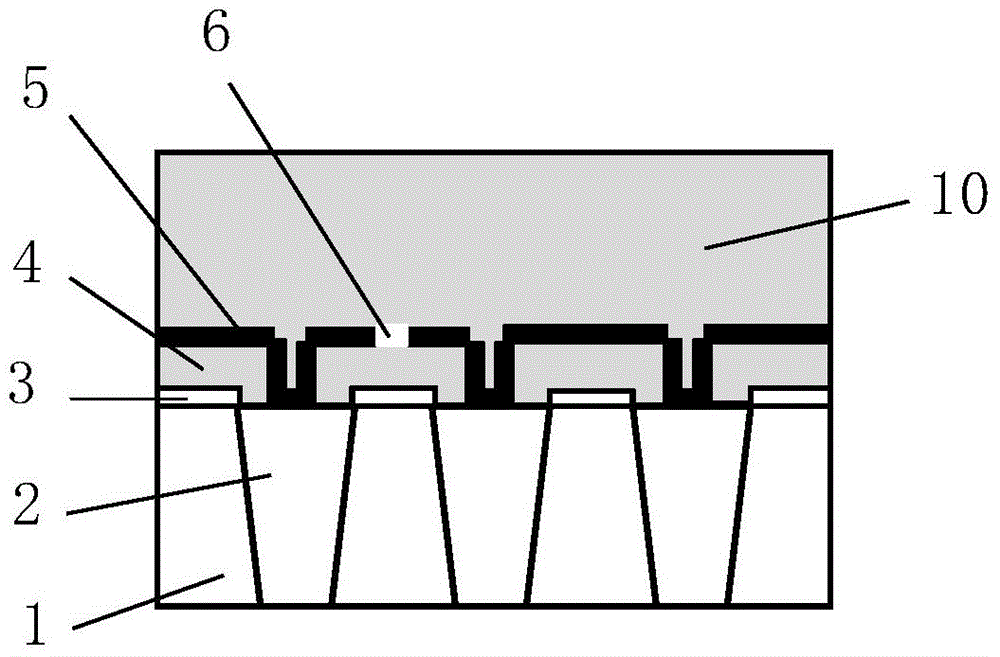

Semiconductor structure for testing an MIM (Metal-Insulating medium-Metal) capacitor

ActiveCN103367329AEasy to makeLow costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor structureLower pole

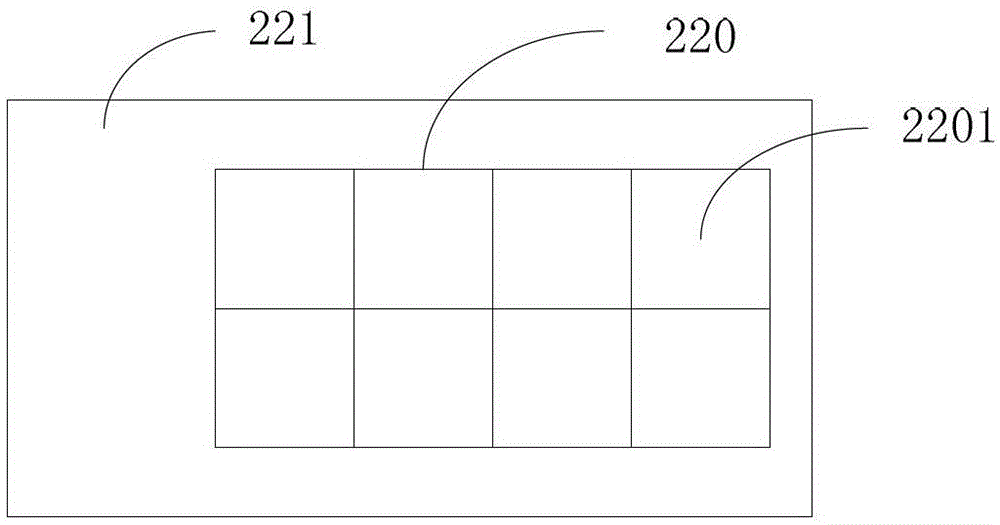

A semiconductor structure for testing an MIM (Metal-Insulating medium-Metal) capacitor comprises a plurality of layers, including a first metal layer, a second metal layer, an upper pole-plate and a lower pole-plate; the first metal layer at least comprises a first circuit area and a second circuit area; the second metal layer is arranged under the first metal layer, spaced from the first metal layer through a medium layer and electrically connected with the second circuit area; the upper pole-plate is arranged in the medium layer in a position near the first metal layer and electrically connected with the first circuit area; the lower pole-plate is opposite to the upper pole-plate in the vertical direction, arranged in the medium layer in a position near the second metal layer, spaced from the upper pole-plate through an insulating layer and electrically connected with the second circuit area. The semiconductor structure is formed on a P type semiconductor substrate, and the second metal layer is electrically connected with the P type semiconductor substrate through a first closed circuit, so that a second closed circuit from the upper pole-plate to the P type semiconductor substrate is formed when an electric leakage area exists in the insulating layer; the semiconductor structure can accurately detect whether an electric leakage area exists in the MIM capacitor, is simple to manufacture and low in cost, and is especially suitable for quickly positioning the electric leakage area of a large-area MIM capacitor.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

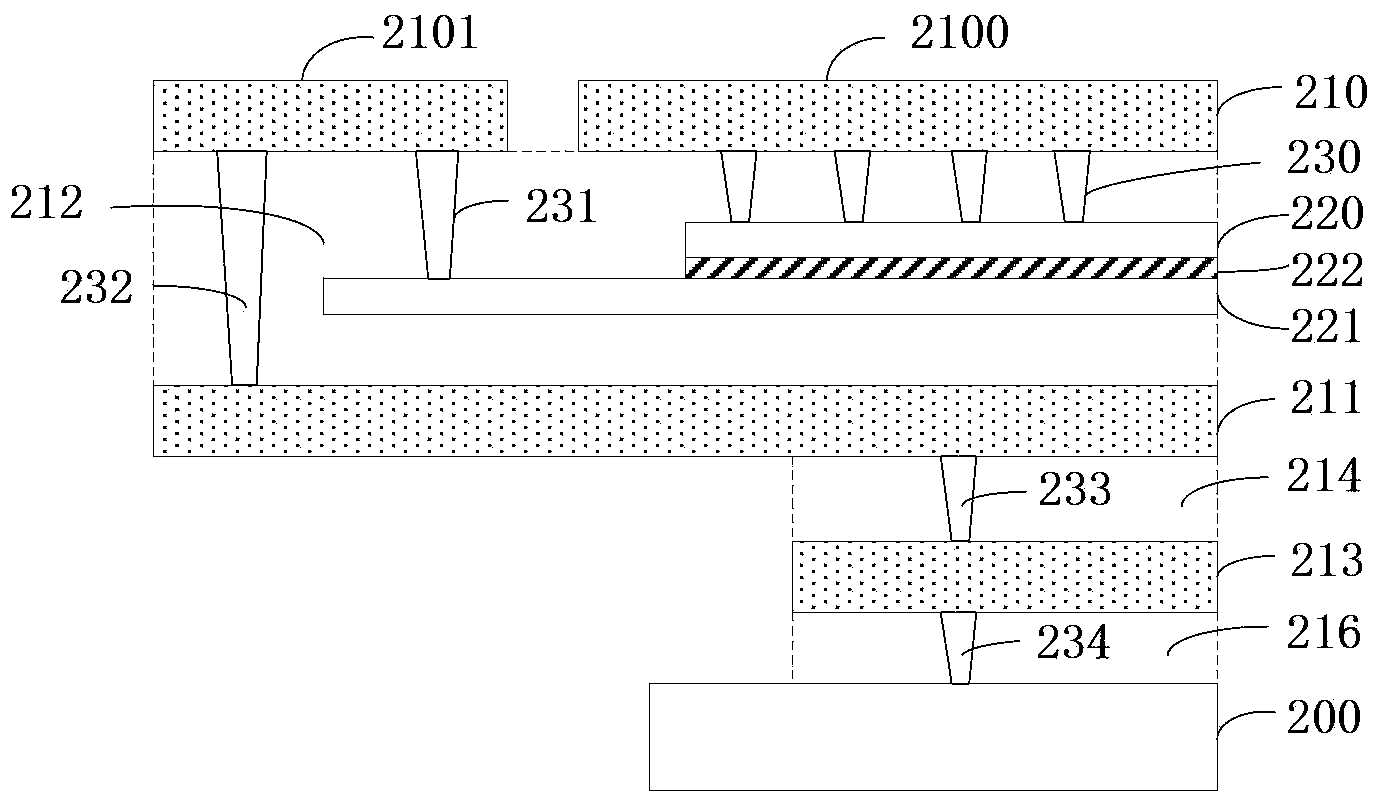

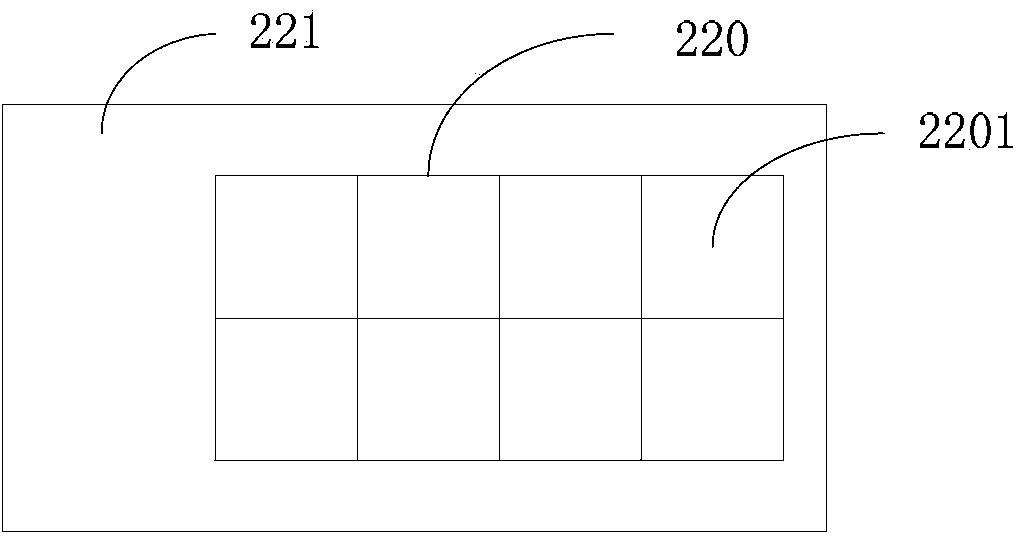

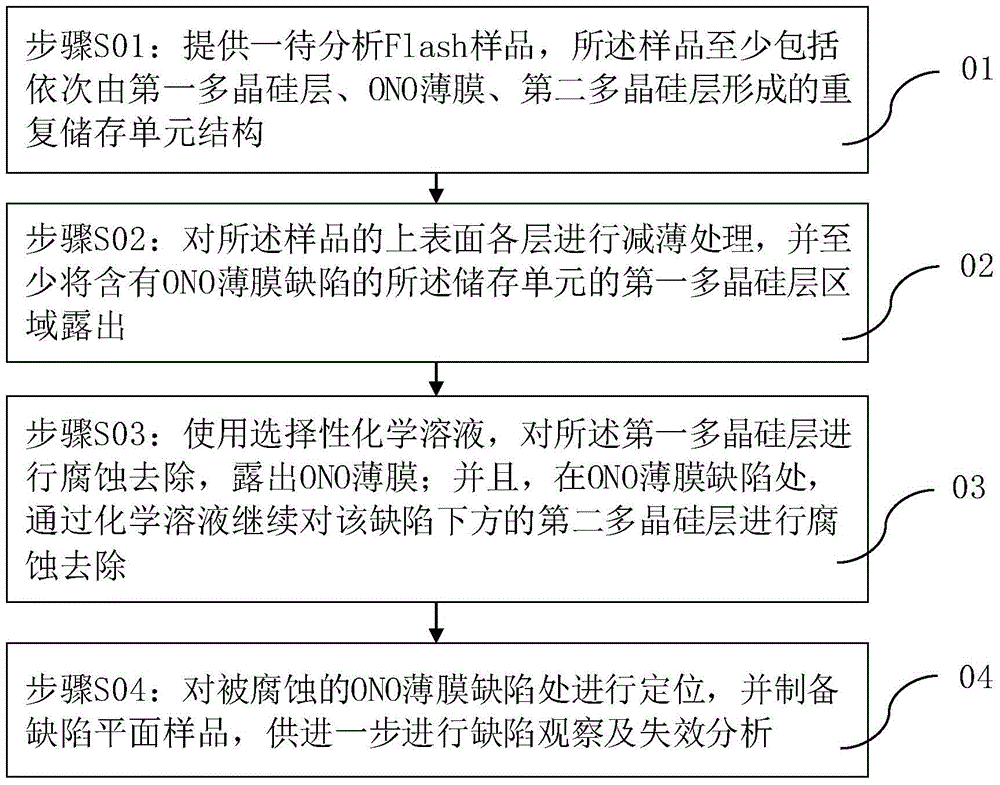

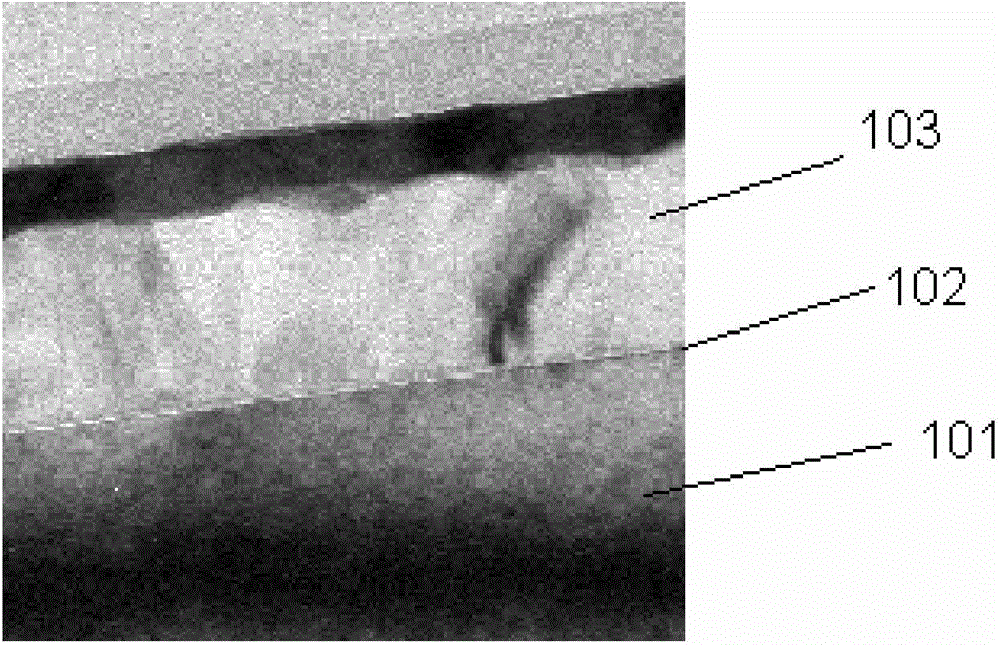

Method for analyzing failures due to defects of ONO (silicon oxide-silicon nitride-silicon oxide) thin films of Flash products

ActiveCN104795340AEasy to analyzeAnalysis is accurate and more granularSemiconductor/solid-state device testing/measurementChemical solutionSilicon oxide

The invention discloses a method for analyzing failures due to defects of ONO (silicon oxide-silicon nitride-silicon oxide) thin films of Flash products. The method includes thinning various layers of the upper surfaces of to-be-analyzed Flash samples and exposing first polycrystalline silicon layer regions of storage units; corroding and removing first polycrystalline silicon layers by the aid of selective chemical solution and exposing the ONO thin films; corroding and removing second polycrystalline silicon layers below the defects of the ONO thin films by the aid of the chemical solution and positioning the corroded defects of the ONO thin films; manufacturing planar samples of the defects for further observing the defects and analyzing the failures. The first polycrystalline silicon layer regions of the storage units contain the defects of the ONO thin films. The method has the advantages that the defects of the ONO thin films of the Flash products can be conveniently, accurately and finely analyzed, accordingly, the failure analysis efficiency can be greatly improved, and the method can assist in quickly increasing the yield of the Flash products and quickly improving the reliability of the Flash products.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

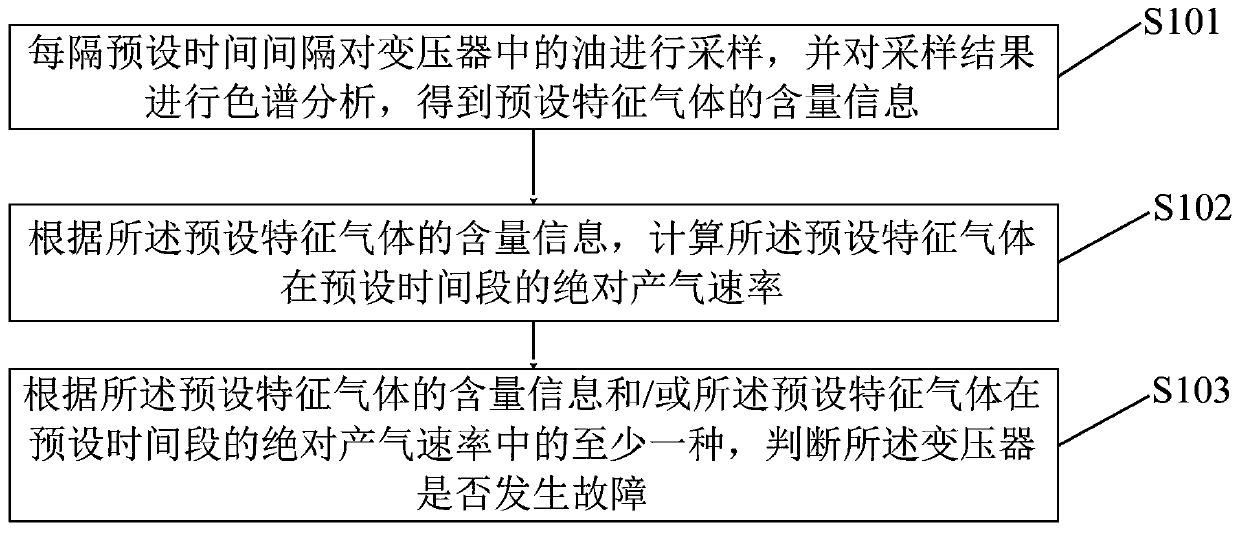

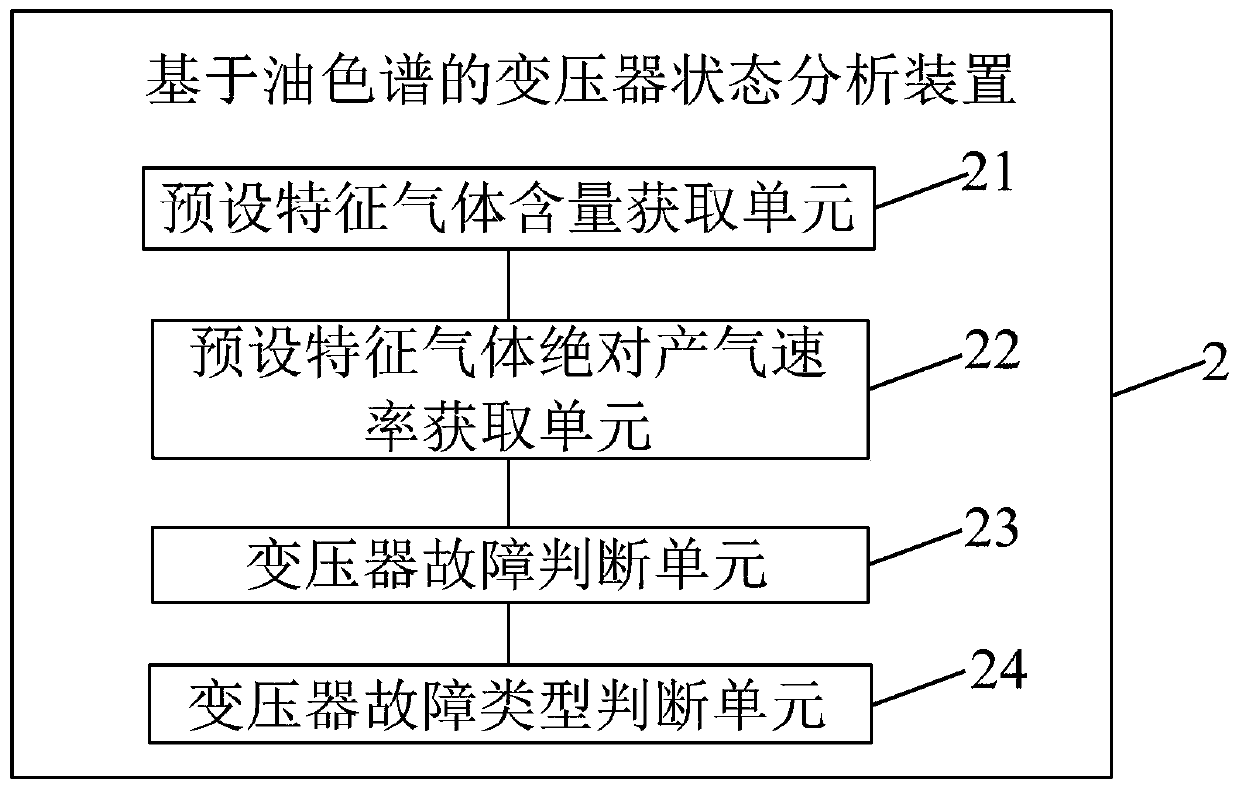

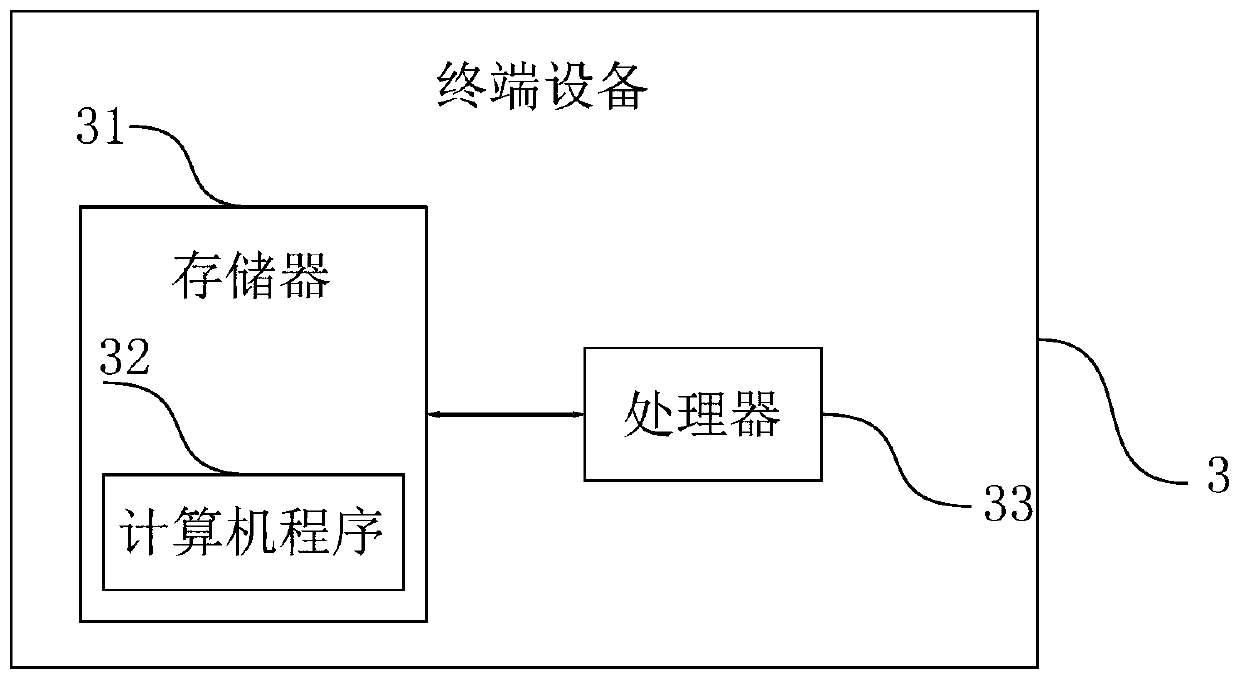

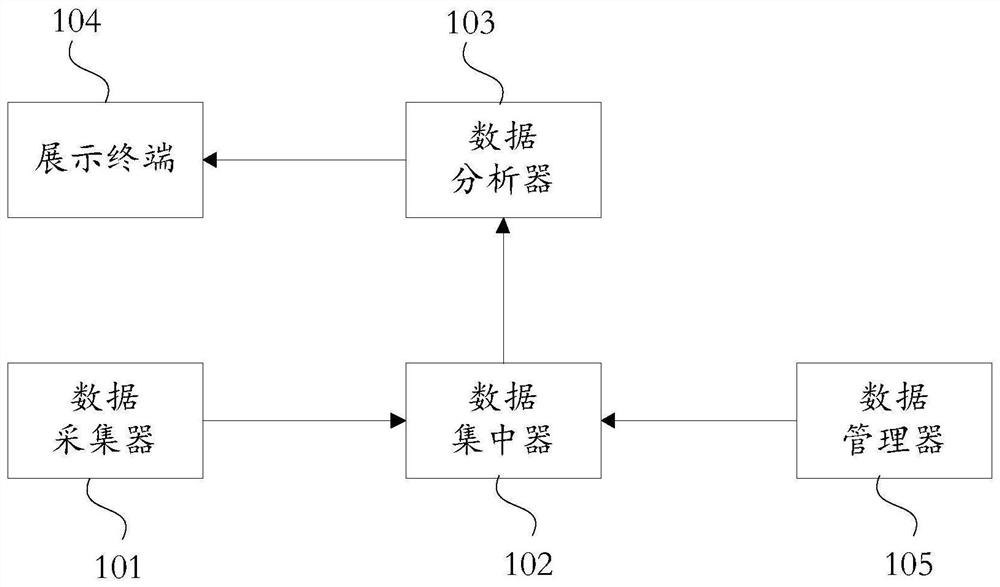

Transformer state analysis method based on oil chromatography, and terminal device

InactiveCN110220983AImprove the efficiency of failure analysisTesting dielectric strengthComponent separationProduction rateTerminal equipment

The invention provides a transformer state analysis method based on oil chromatography, and a terminal device. The method comprises the steps of: sampling oil in a transformer at preset time intervals, and performing chromatographic analysis on sampling results to obtain content information of a preset characteristic gas; calculating an absolute gas production rate of the preset characteristic gaswithin a preset time period according to the content information of the preset characteristic gas; and judging whether the transformer is faulty according to at least one of the content information of the preset characteristic gas and / or the absolute gas production rate of the preset characteristic gas within the preset time period. According to the transformer state analysis method provided by the invention, online monitoring is performed on the oil chromatography of the transformer to perform intelligent analysis on the state of the transformer in real time, thereby improving the efficiencyof fault analysis of the transformer.

Owner:STATE GRID CORP OF CHINA +1

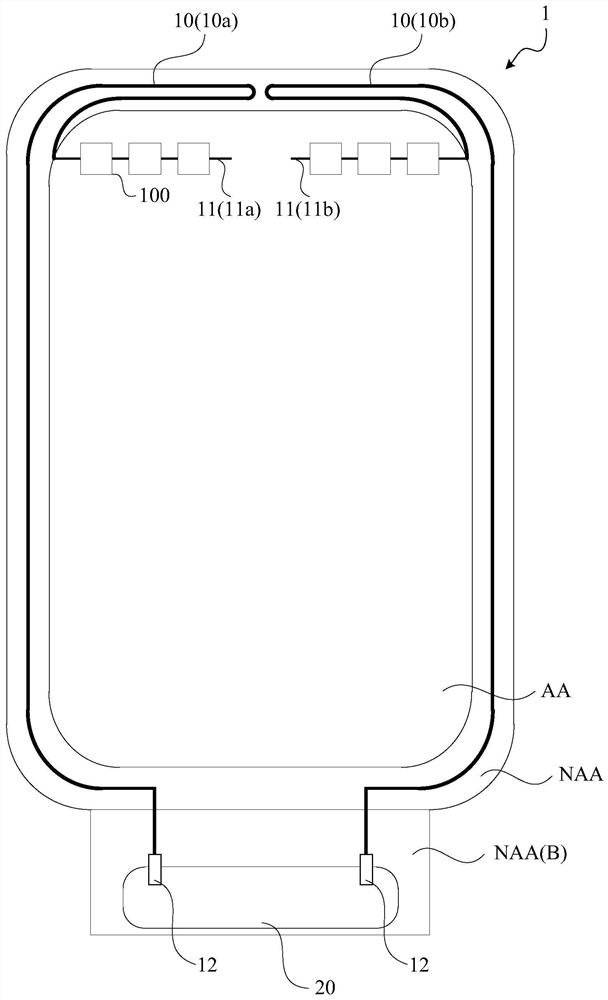

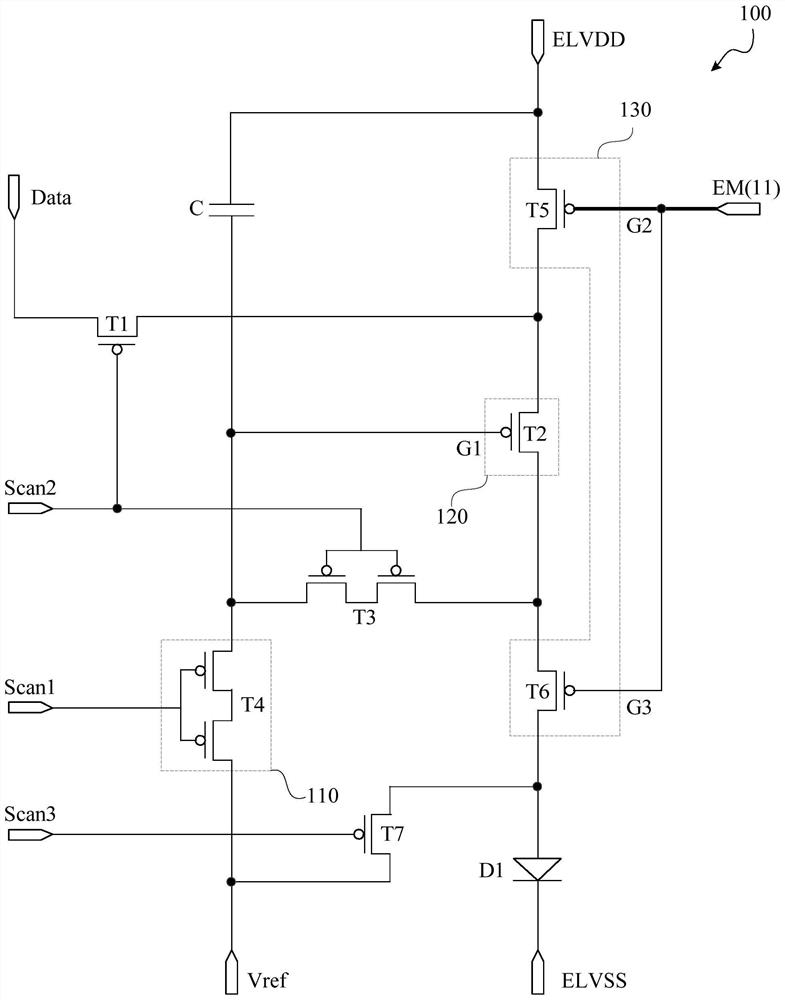

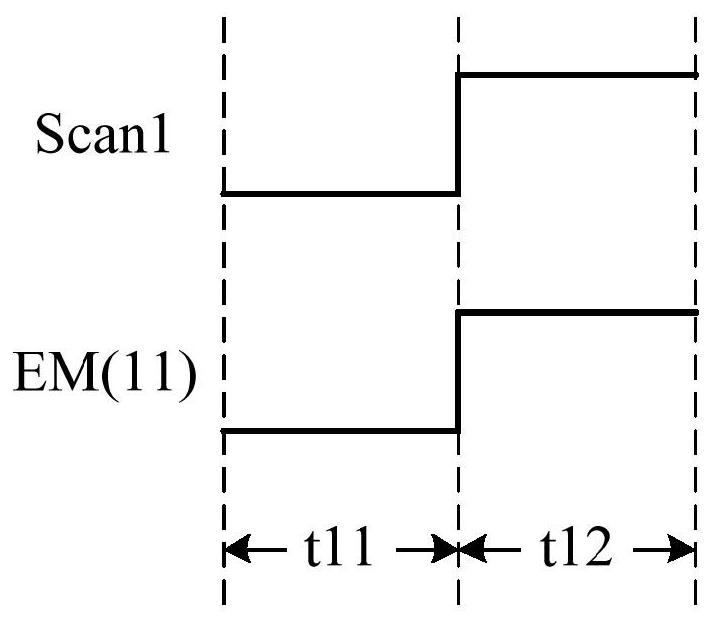

Display panel and crack detection method thereof and display device

PendingCN111833786AImprove the efficiency of failure analysisAvoid problems such as abnormal bright linesStatic indicating devicesComputer hardwareDisplay device

The embodiment of the invention discloses a display panel and a crack detection method thereof and a display device. The display panel is provided with a display area and a non-display area. The display panel includes a dummy pixel circuit and a light emitting device connected to the dummy pixel circuit; the crack detection line is located in the non-display area, one end of the crack detection line is connected with the test terminal, the other end of the crack detection line is connected with the driving signal line, the driving signal line is connected with the dummy pixel circuit, and signals transmitted to the driving signal line by the crack detection line can control the dummy pixel circuit to drive the light emitting device to emit light. According to the technical scheme providedby the embodiment of the invention,the crack detection lines, the corresponding driving signal lines and the dummy pixel circuit are connected through the test terminals, and the test signal is transmitted to the light-emitting device connected with the dummy pixel circuit, thereby achieving the crack detection of the display panel, facilitating the implementation of a narrow-frame design, reducing the abnormality risk of a detection image, and improving the failure analysis efficiency of the display panel and the detection efficiency of a defective product.

Owner:YUNGU GUAN TECH CO LTD

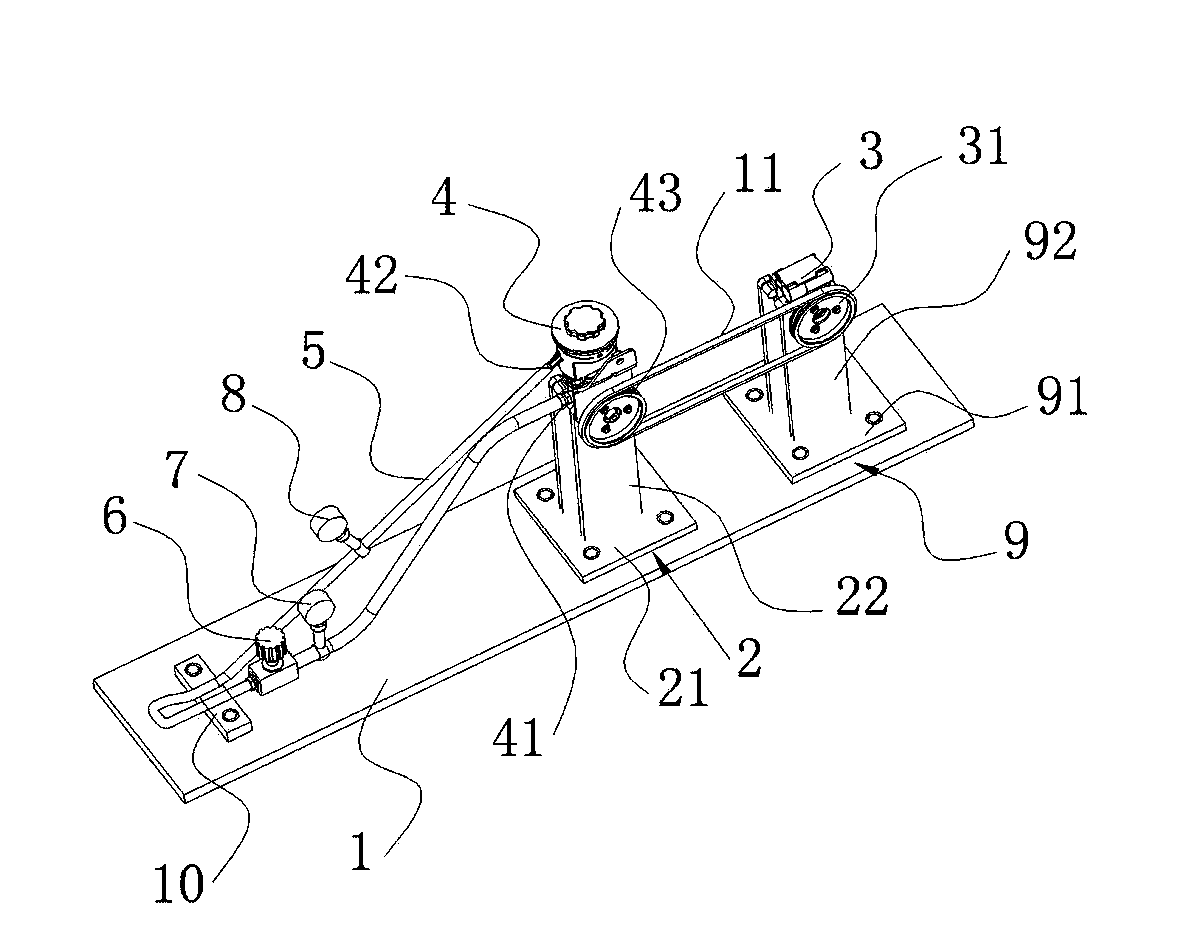

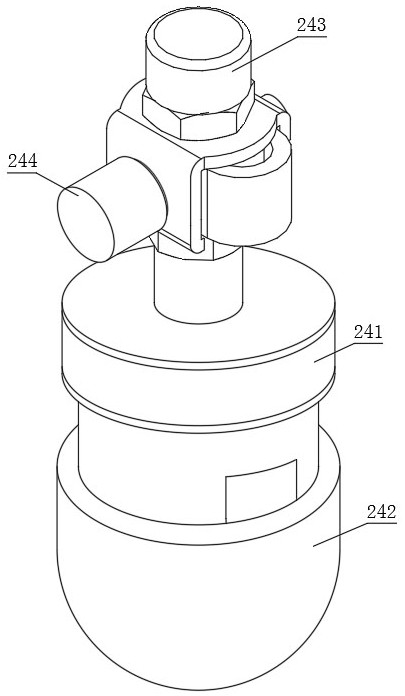

Testing device and testing method for steering oil pump assembly

InactiveCN103352840AGuaranteed uptimeQuick disassemblyPump testingPositive-displacement liquid enginesElectric machineryProcess engineering

The invention discloses a testing device and provides a testing device for a steering oil pump assembly, which has a simple structure, is convenient to use and can rapidly and accurately detect the steering oil pump assembly, and a testing method for the steering oil pump assembly. The invention solves the technical problems of high intensity, long detection period, high cost, incapability of carrying out durability test on each batch of new steering oil pump assembly and the like which are caused by the case that in the prior art, a steering oil pump can be detected only after being loaded. The testing device comprises a testing platform; the testing platform is provided with an oil pump fixing seat for fixing the steering oil pump assembly and a driving motor capable of driving the steering oil pump assembly to operate; an oil pipe is communicated between a high pressure oil outlet and a low pressure oil return port of the steering oil pump assembly; the oil pipe is provided with a pipeline control valve, a pressure valve and a flow valve.

Owner:ZHEJIANG HAOQING AUTOMOBILE MFG CO LTD +1

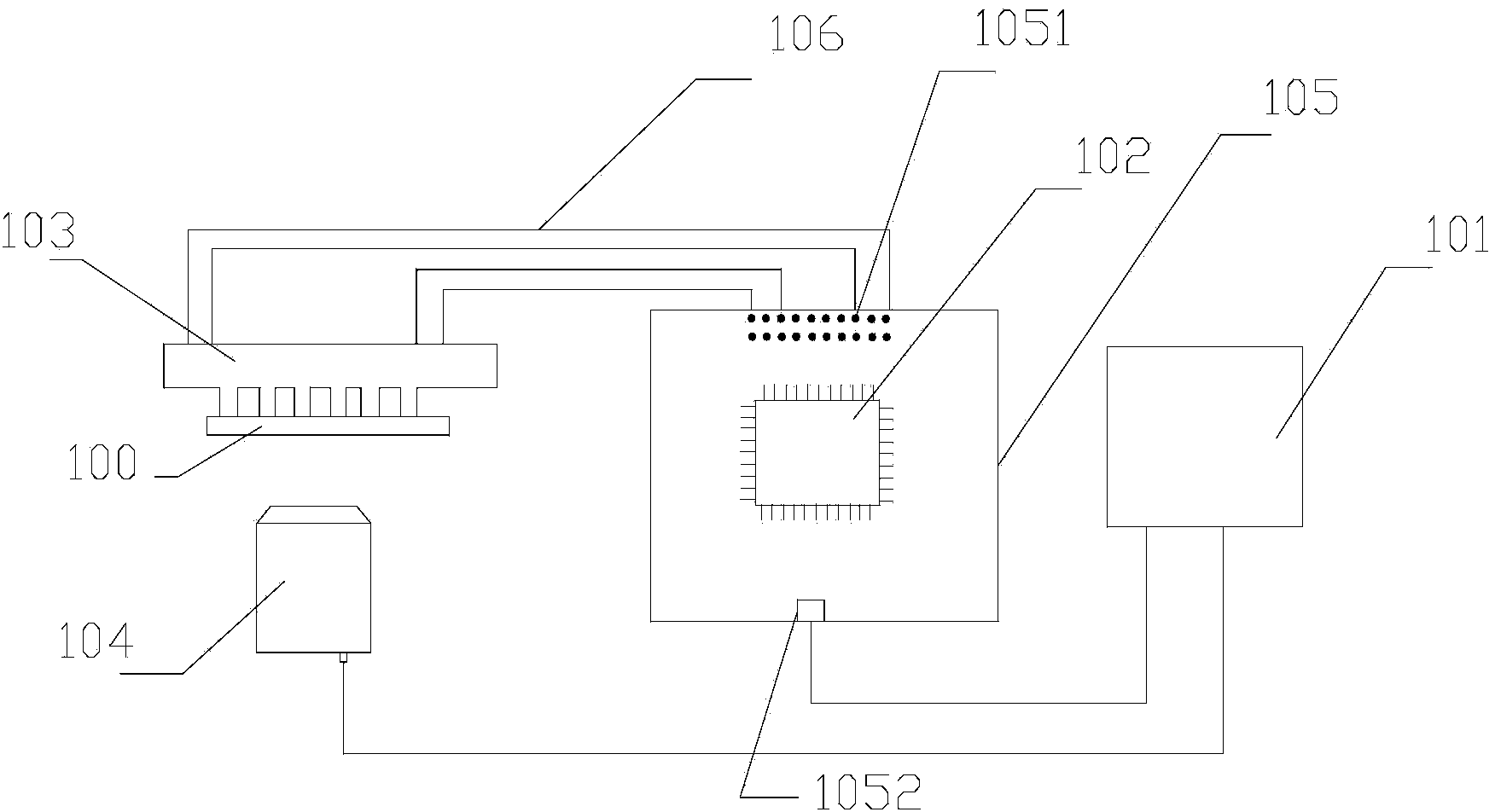

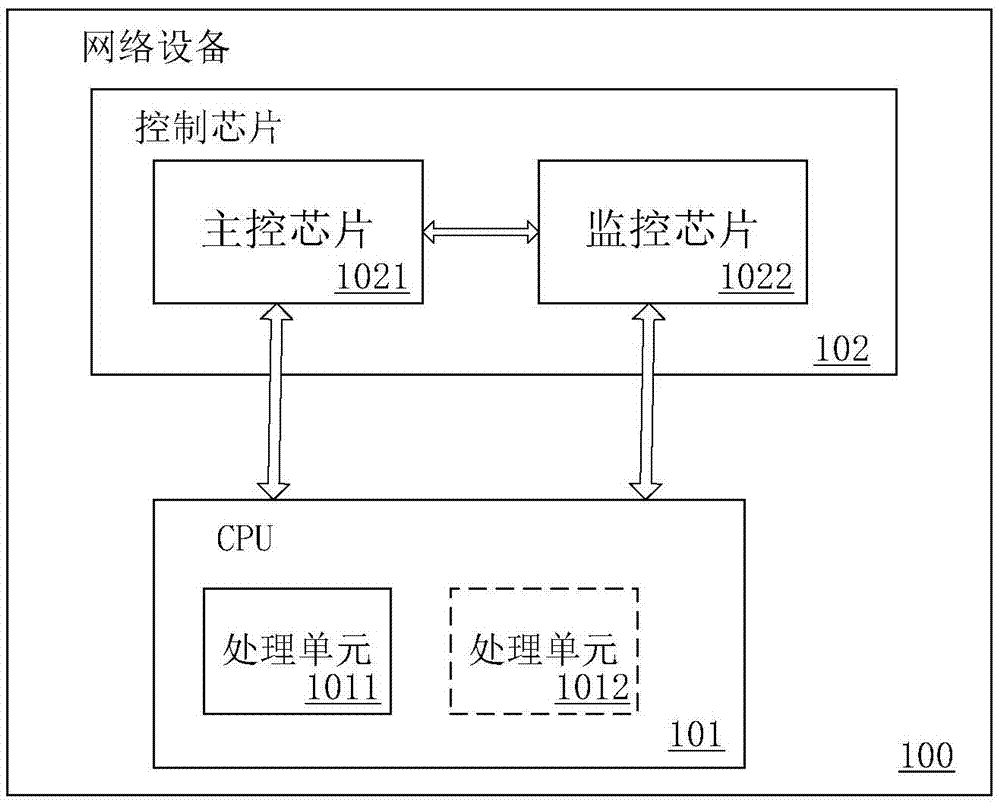

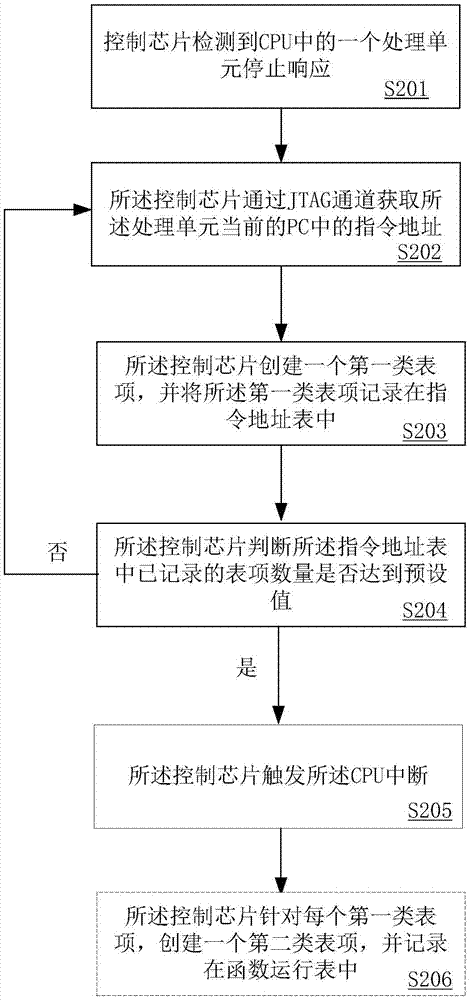

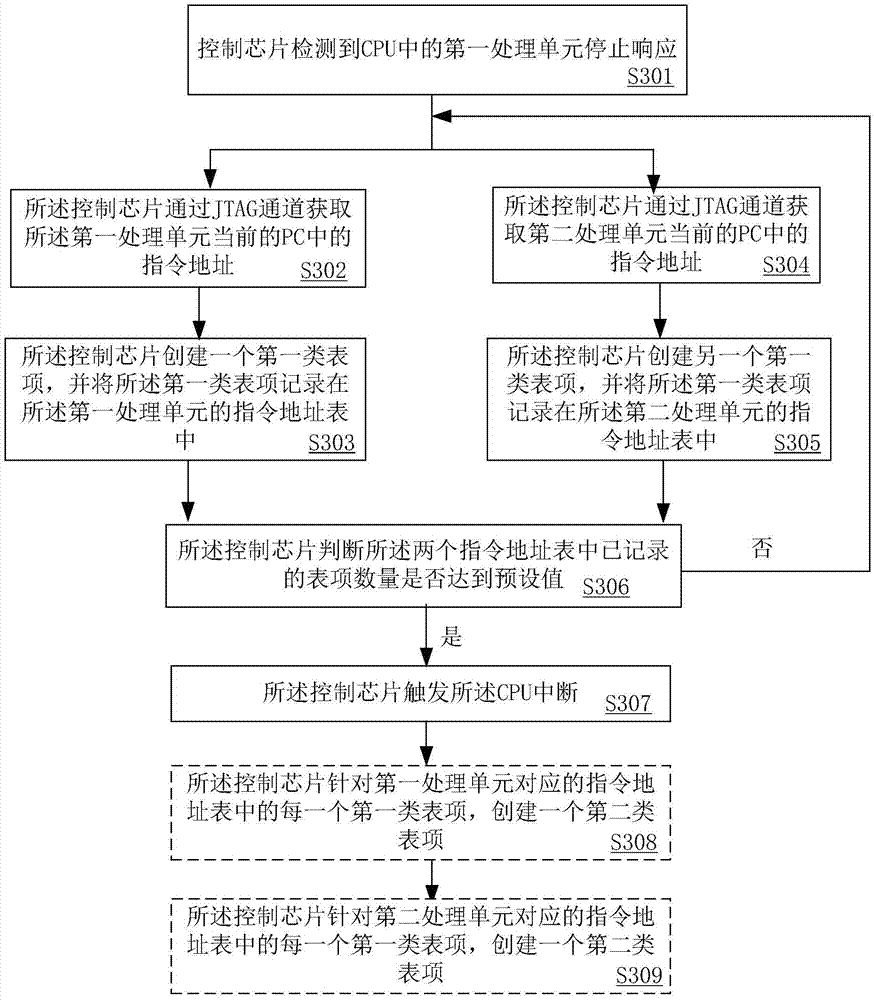

Processor fault record generation method and apparatus

ActiveCN106919462AImprove the efficiency of failure analysisAccurately reflectFault responseEmbedded systemFault analysis

The invention relates to the field of computers, in particular to a processor fault record generation method and apparatus. The processor fault record generation method comprises the steps of obtaining an instruction address in a current program counter (PC) of a processing unit through a JTAG channel when a control chip detects that the processing unit in a CPU stops responding, creating a first class table item comprising the instruction address in the current PC, and recording the first class table item in an instruction address table; and when the number of table items recorded in the instruction address table reaches a preset value, triggering CPU interrupt by the control chip. According to the scheme provided by the method and the apparatus, more information can be provided for processor fault analysis, so that the fault analysis efficiency is improved.

Owner:HUAWEI TECH CO LTD

Power transmission and transformation system risk early warning method

InactiveCN106651128AAccurately determineReduce patrol rangeResourcesElectric power transmissionPower grid

The invention discloses a power transmission and transformation system risk early warning method. The method includes the following steps that: S1, a power transmission line risk assessment establishing overall framework is established, a risk assessment model is established according to each component of a power transmission line, the quantization of state quantities is established, and the degrees of membership of the state quantities are solved; and S2, a calculation method and an evaluation standard for the correction of the risk value of the power transmission line by the operating years and operating environment of equipment and the operation status of a power grid are determined, and the aging coefficients of the components, the operating environment time coefficient and geographical position coefficient of the power transmission line are defined. With the power transmission and transformation system risk early warning method of the invention adopted, an interval of the power transmission line, where a fault occurs, can be determined more accurately, fault inspection can be performed in a targeted manner, the inspection range of line fault inspectors can be decreased, line fault inspection time can be decreased, the cause of the fault of the power transmission line can be determined more accurately, and the efficiency of fault analysis can be improved.

Owner:STATE GRID CORP OF CHINA +1

Gate oxide layer failure analysis method

ActiveCN105784743AImprove the efficiency of failure analysisMaterial analysis by measuring secondary emissionConventional transmission electron microscopeElemental analysis

The invention discloses a gate oxide layer failure analysis method; a prepared TEM sample is bombarded by using an ionic beam having certain energy, Poly in the TEM sample is non-crystallized, the Poly lattice contrast cannot be showed in a transmission electron microscope, the contrast of heavy metals still remains, heavy metal polluted positions can be clearly observed under the transmission electron microscope, elemental analysis is successfully carried out, and thus the gate oxide layer failure analysis efficiency is effectively improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

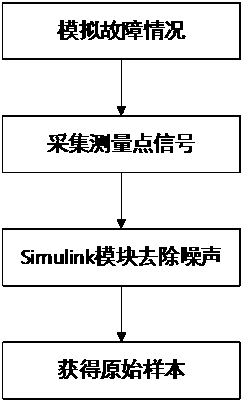

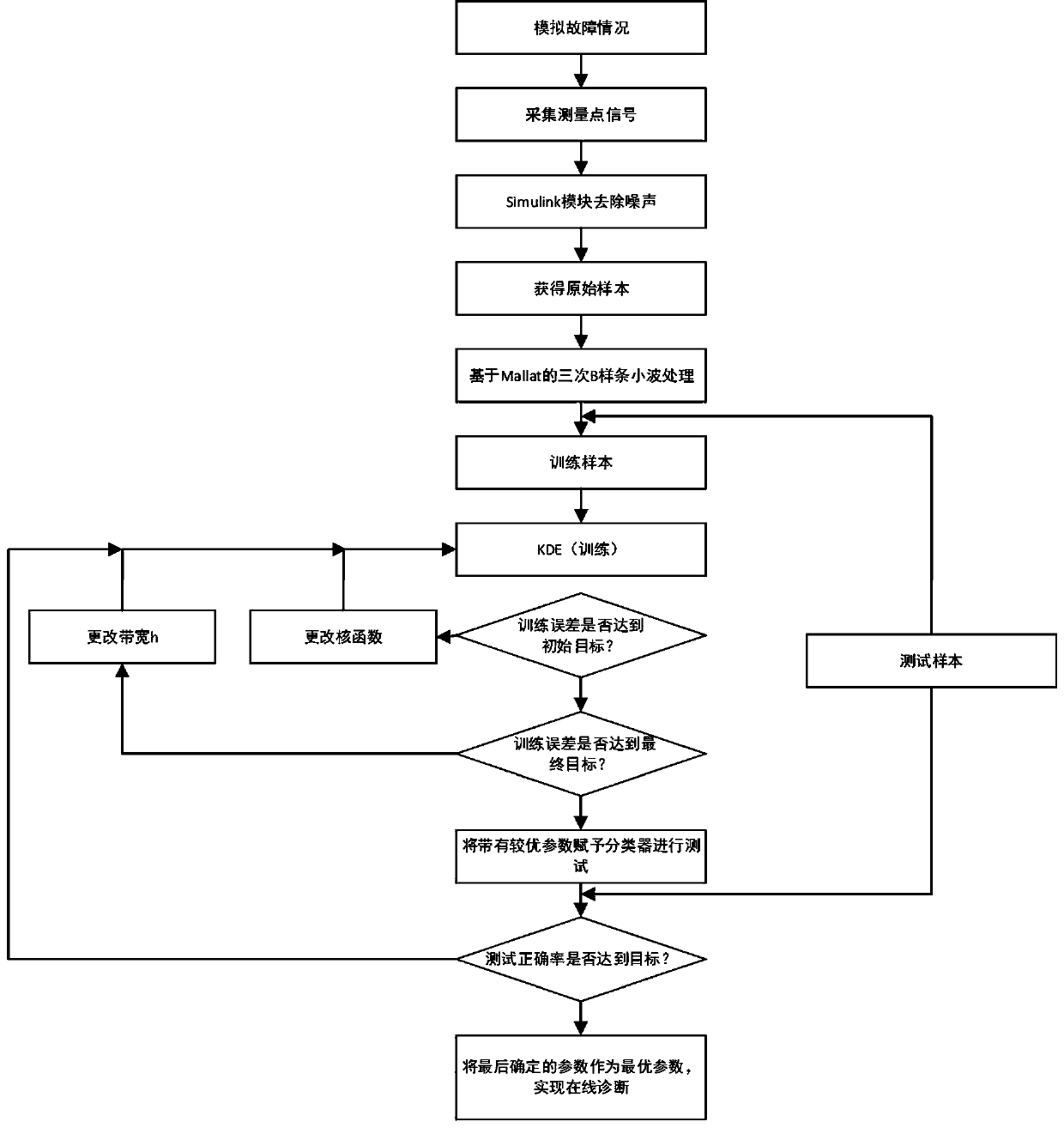

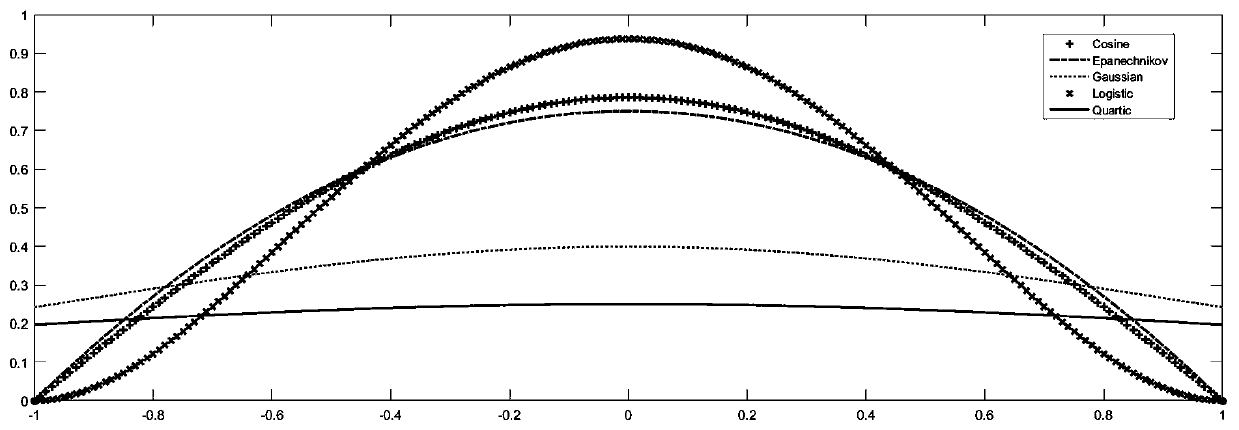

Converter fault diagnosis method based on kernel density estimation

InactiveCN109828168AThe principle is simpleReliable judgment of health statusElectrical testingCharacter and pattern recognitionSpectral density estimationDiagnosis methods

The invention relates to a converter fault diagnosis method based on kernel density estimation. The method comprises the steps of: performing pre-processing of collected data through cubic B-spline wavelet analysis based on a mallat algorithm to obtain samples with fault features; employing a KDE fault classifier to perform offline training to select better parameters of the fault classifier and accurately dividing the normal conditions and each type of fault condition included in the training samples, and using the better parameters into a classifier network to obtain the optimal parameters;implanting the classifier network with the optimal parameters into online simulation to perform real-time online monitoring fault diagnosis of an actual circuit; and allowing the classifier network with completion of optimal parameters to distinguish known fault type samples and normal samples, complete the location of the known fault types of faults and identify the unknown faults for achievementof circuit protection in a condition of generation of unknown types of faults. The converter fault diagnosis method based on kernel density estimation can determine the health condition of the converter more accurately and more reliably, and also can improve the efficiency of the fault diagnosis of the converter.

Owner:FUZHOU UNIV +1

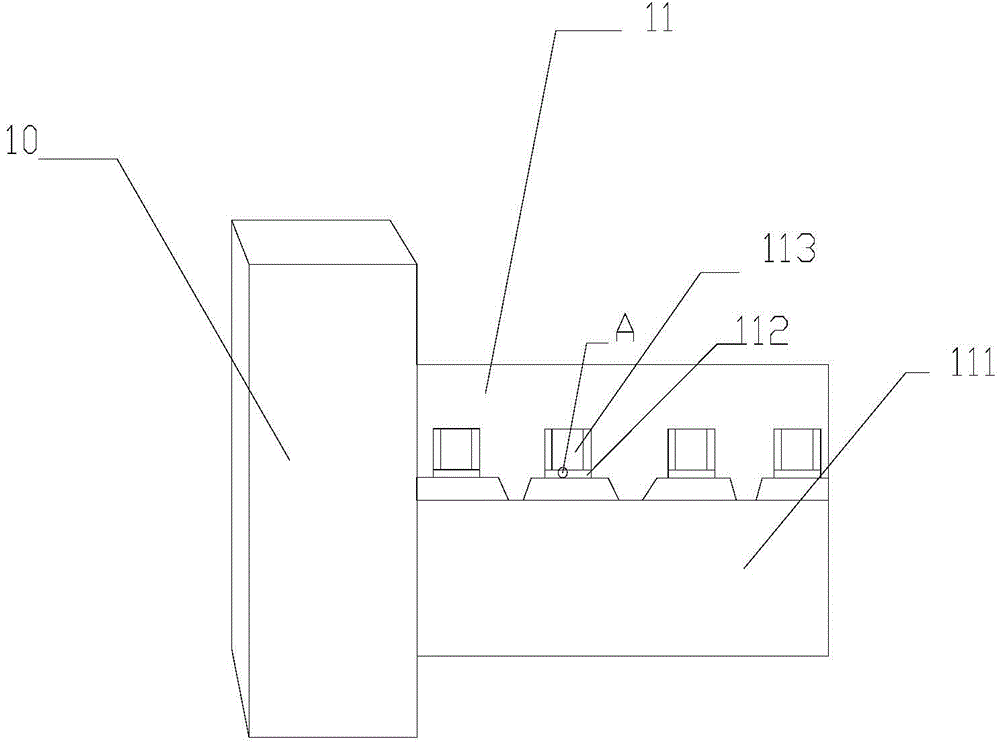

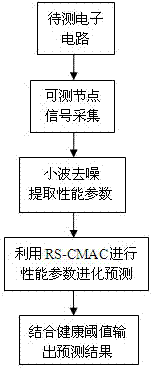

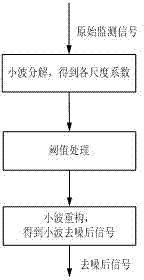

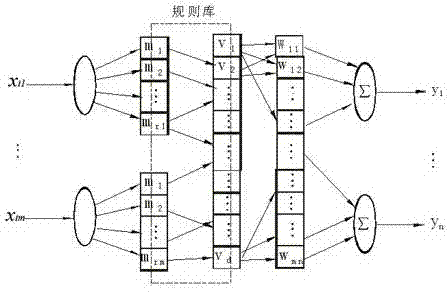

Online intelligent fault prediction method for power electronic circuit based on RS-CMAC (rough sets and cerebellar model articulation controller)

InactiveCN102830341ASimple data entryImprove the efficiency of failure analysisElectronic circuit testingWavelet denoisingRough set

The invention discloses an online intelligent fault prediction method for a power electronic circuit based on RS-CMAC (rough sets and cerebellar model articulation controller) and belongs to the technical field of fault testing for power electronic circuits. The method includes: monitoring node signals in real time, performing wavelet denoising to obtain a fault feature sample, extracting circuit performance parameters, and building an RS-CMAC model to predict a time sequence of the circuit performance parameters in future time. According to the rough set theory and the CMAC model, input data of the CMAC model are simplified by a rough set data analysis method, and the efficiency in analyzing faults of the power electronic circuit is improved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

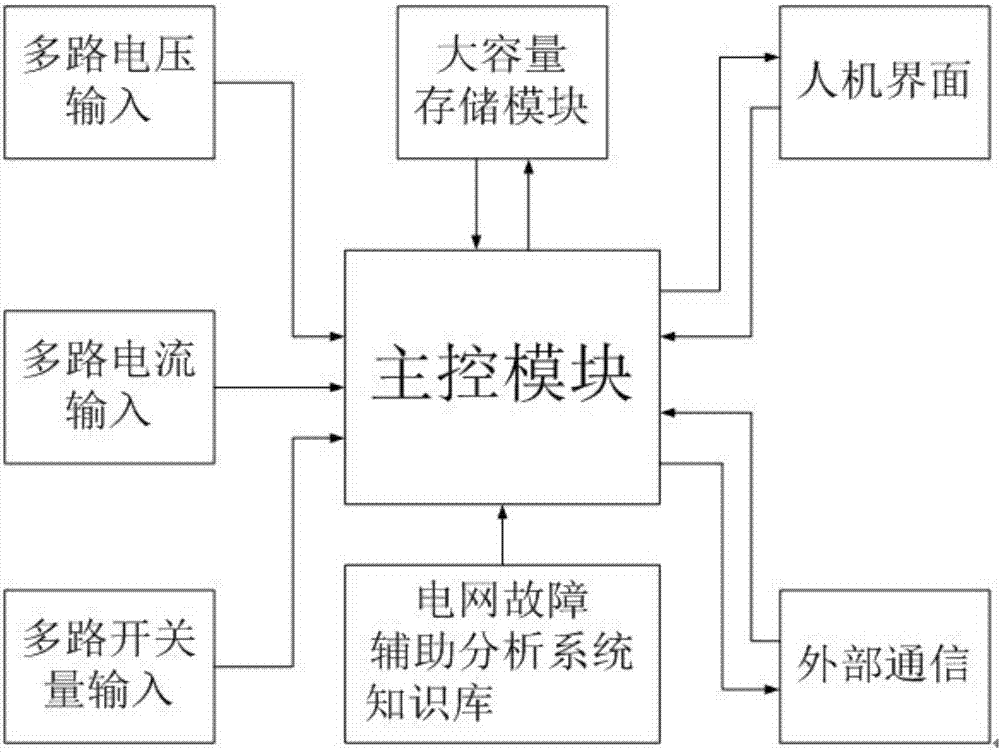

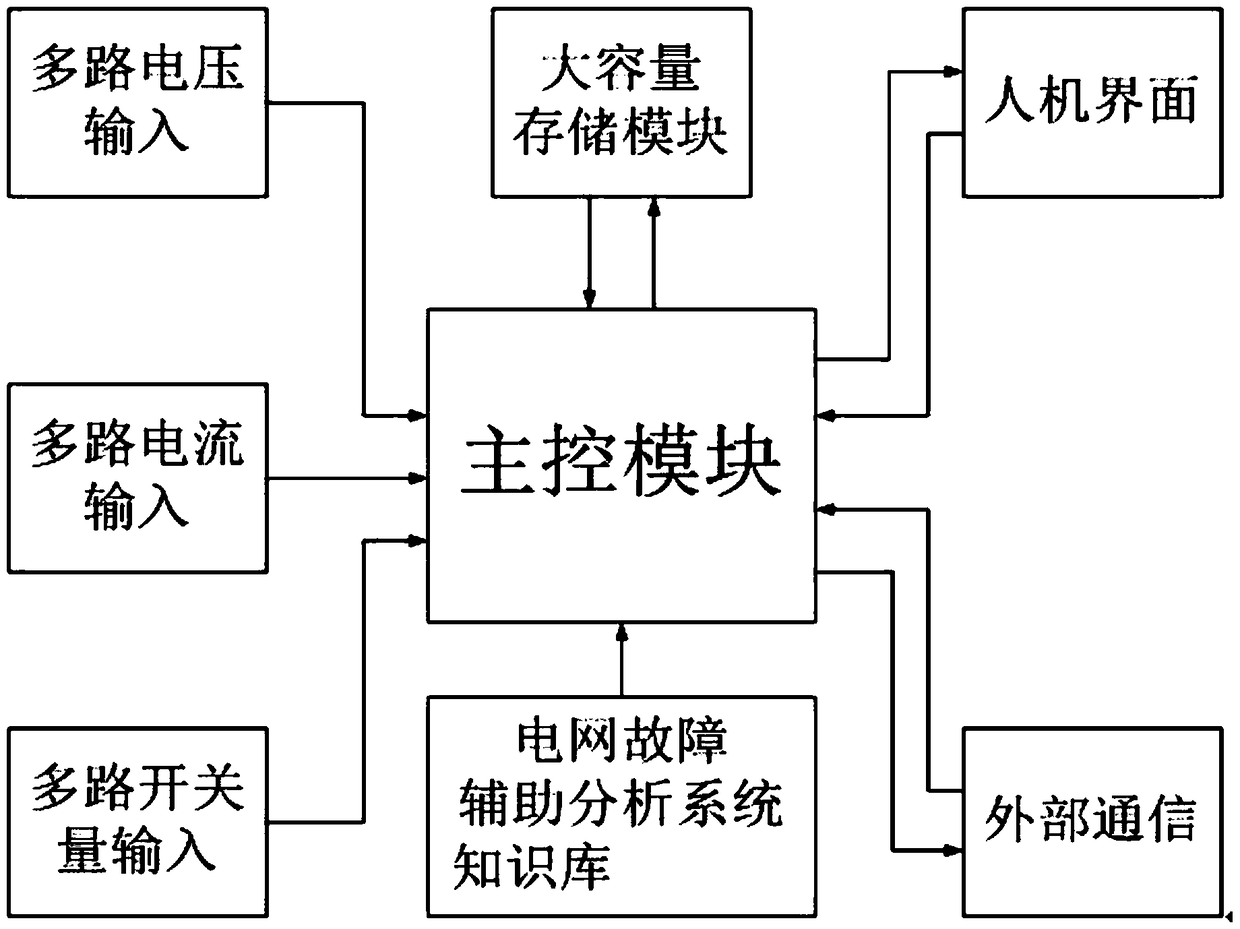

Auxiliary grid fault analysis system

ActiveCN104502797AMeet needsRealize real-time monitoringFault locationHuman–machine interfaceExternal communication

The invention discloses an auxiliary grid fault analysis system. The auxiliary grid fault analysis system comprises a main control module, wherein the main control module is connected with a plurality of paths of voltage input modules, a plurality of paths of current input modules, a plurality of switching value input modules, a high-capacity storage module, a human-computer interface, an external communication module and an auxiliary grid fault analysis system knowledge base; the three-phase voltage, the three-phase current waveform, the effective value, the period and the frequency are displayed in real time, and the single-phase or three-phase reactive power value, the active power value and the apparent power value are displayed in real time; one to eight alternating quantities are randomly selected from all alternating analog quantity channels, and the phasor diagrams are displayed; the first phasor phase fixedly serves as the reference, other phasors are based on the first phasor phase, drawing is carried out according to the phase corresponding to the reference phasor, and the effective value and the phase angle of the phasors are displayed; the positive sequence effective value, the positive sequence phase angle, the negative sequence effective value, the negative sequence phase angle, the zero sequence effective value and the zero sequence phase angle can be displayed in real time according to three-phase voltage or three-phase current, and the auxiliary grid fault analysis system has two harmonic analysis modes.

Owner:SHANGHAI HEKAI ELECTRICAL TECH

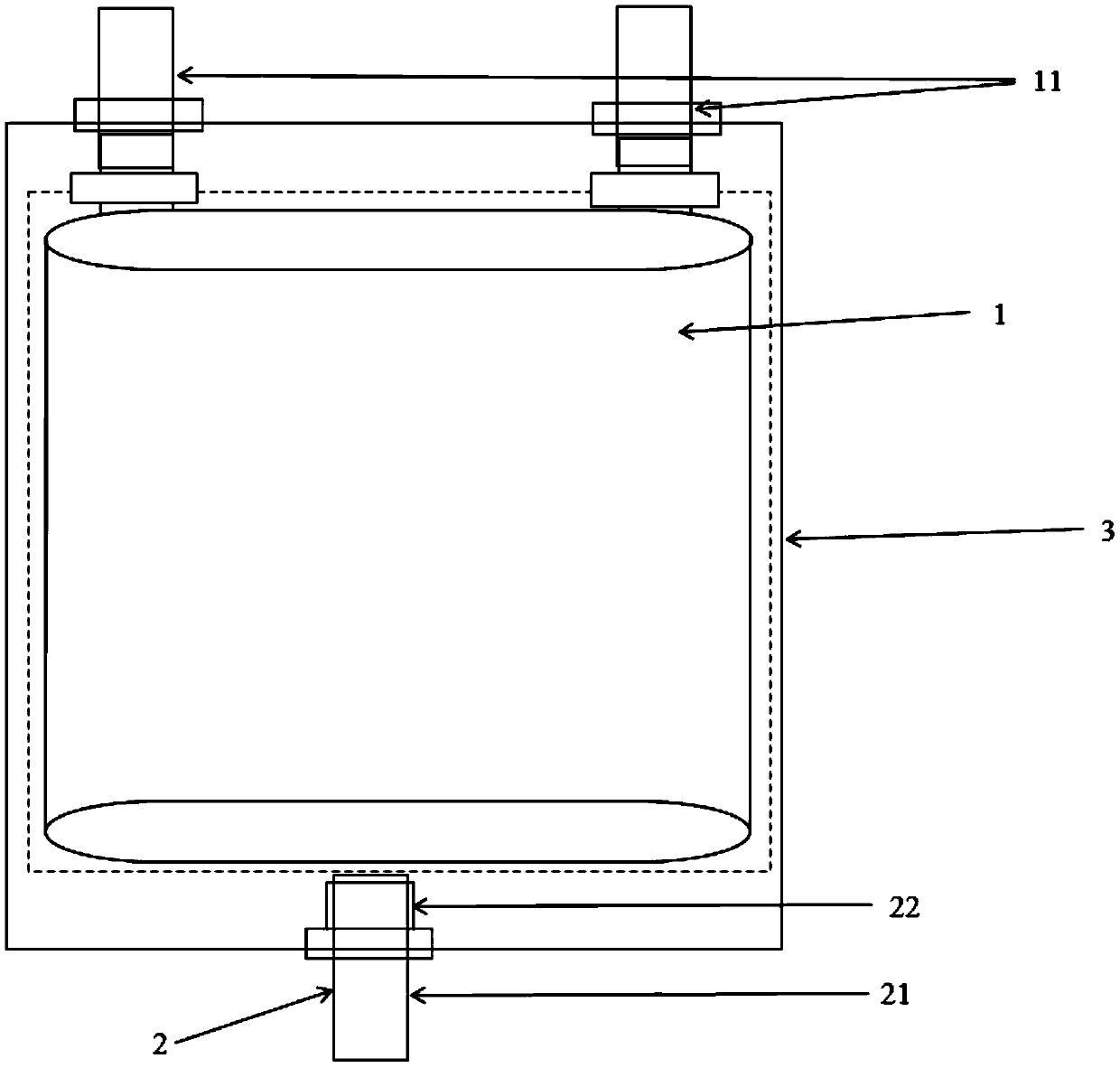

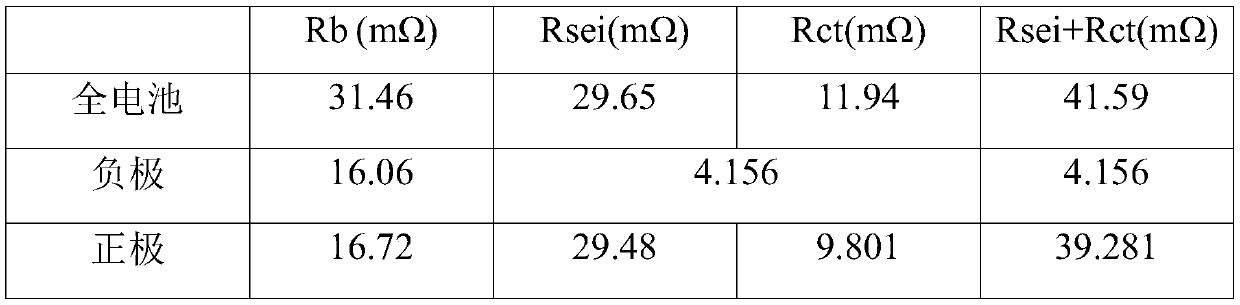

Three-electrode battery and preparation method thereof

PendingCN111063939AReduce mistakesAvoid damageFinal product manufactureCell component detailsBattery cellElectrical and Electronics engineering

The invention provides a three-electrode battery and a preparation method thereof. The preparation method comprises the following steps: S1, first tabs are connected to a positive tab and a negative tab of a charged battery cell body respectively, and the first tabs are partially exposed out of a battery shell; S2, a reference electrode is coated with a diaphragm and connected with a second tab, part of the second tab is exposed out of the battery shell, the diaphragm is arranged in the battery shell, and the reference electrode and the charged battery cell body are kept in a non-contact state; and S3, the three-electrode battery is packaged, then electrolyte is injected, and the injection coefficient of the electrolyte is 1.5-3 g / Ah; and then shelving aging and secondary sealing processesare carried out to finish the preparation of the three-electrode battery. Compared with the prior art, the charged lithium battery is reassembled on the basis of reserving the original battery cell body, so that a new three-electrode battery is obtained, and the problem that the charged lithium battery cannot be analyzed and detected in a targeted manner at present is solved.

Owner:东莞维科电池有限公司

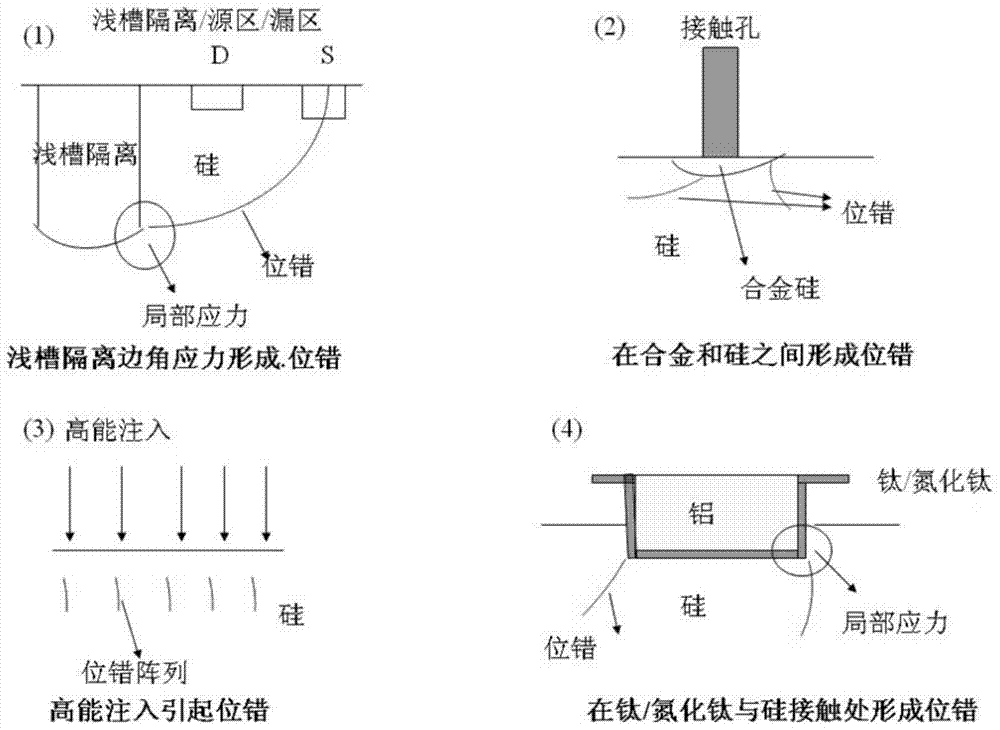

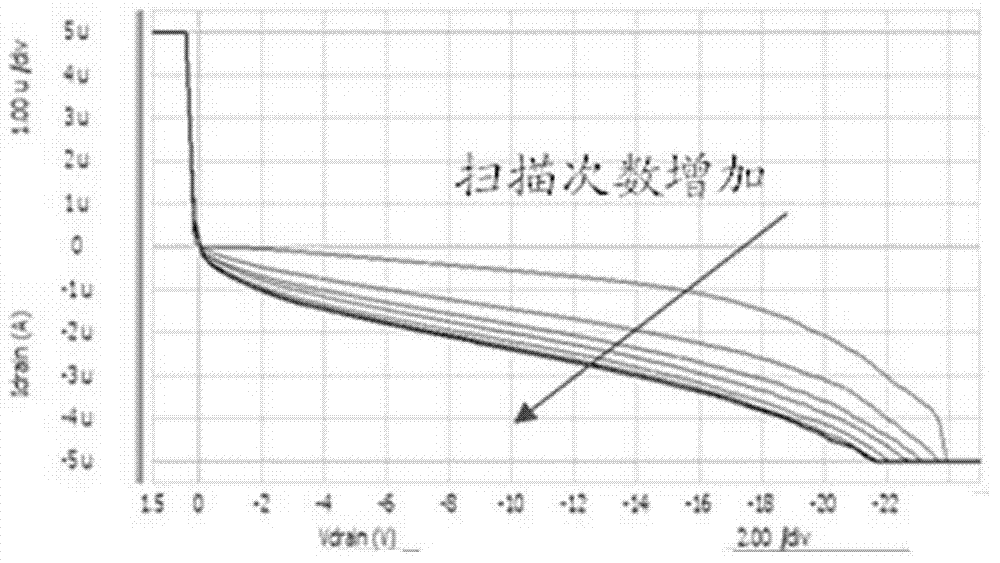

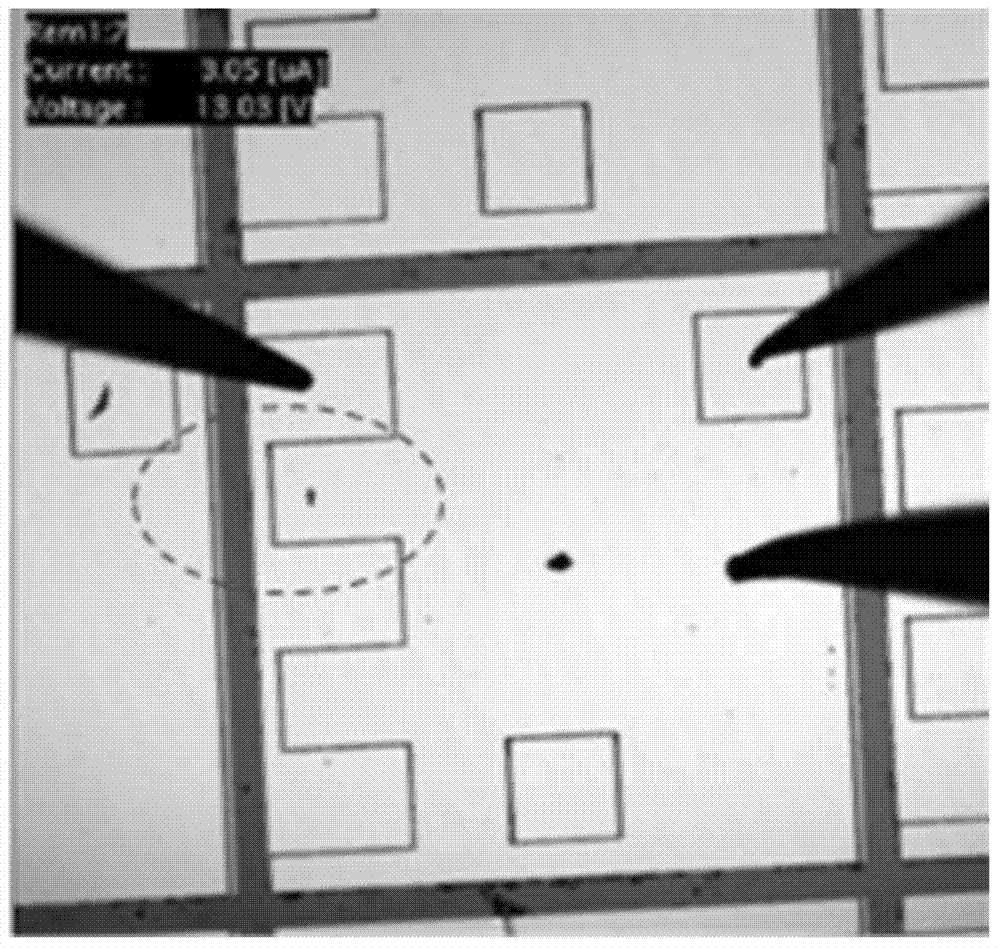

Crystal lattice dislocation detecting method

ActiveCN104297667AImprove efficiencyImprove the efficiency of failure analysisElectronic circuit testingScanning probe techniquesElectrical analysisDislocation

The invention discloses a crystal lattice dislocation detecting method. The method comprises the steps that an invalid device is selected for carrying out an electrical test, a voltage-current curve of the invalid device is scanned and measured repeatedly, and whether the voltage-current curve obtained through repeated scanning becomes larger or smaller is observed; the invalid device is roasted, the voltage-current curve of the invalid device is repeatedly measured again, and whether the voltage-current curve becomes larger or smaller is observed; if it is determined that the voltage-current curve of the device is changed, emission microscope positioning is carried out, and the dislocation range is reduced further; the device is ground, a focused ion beam is used for cutting the device, and a transmission electron microscope sample is formed through physical analytical sample preparation; a common transmission electron microscope observation way is adopted for dislocation observation to obtain a dislocation image. According to the crystal lattice dislocation detecting method, the dislocation is analyzed and the dislocation position is found from the electrical analysis process to the physical analysis process, the integrated circuit device invalidation analysis efficiency is improved, and the cost is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

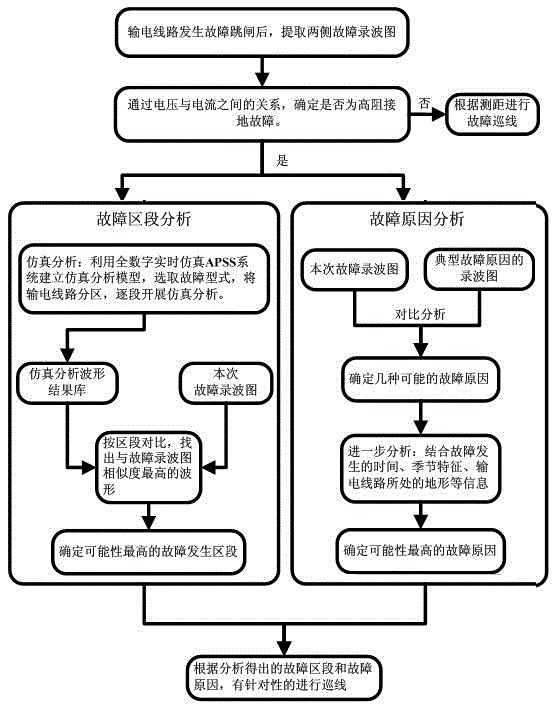

Reason analyzing and locating method for high resistance grounding fault of transmission line

InactiveCN104316791AAccurately determineReduce patrol rangeElectrical testingReal-time simulationEngineering

The invention discloses a reason analyzing and locating method for a high resistance grounding fault of a transmission line. The method comprises: obtaining simulated analysis chart of the high resistance grounding faults of the transmission line in different zones by an all-digital real-time simulation APSS system, and comparing with an actual fault oscillograph, wherein the zone corresponding to the highest waveform similarity is the specific zone where the fault is most likely to occur; comparing the typical fault type oscillograph with the actual fault oscillograph to obtain the most possible fault reason. According to the method provided by the invention, the zone where the high resistance grounding fault of the transmission line occurs can be more accurately determined, fault inspection can be performed in a targeted manner, inspection range of line fault inspectors is reduced, and fault inspection time is shortened; reason for the high resistance grounding fault of the transmission line can be more accurately determined, and fault analysis efficiency is improved.

Owner:STATE GRID CORP OF CHINA +1

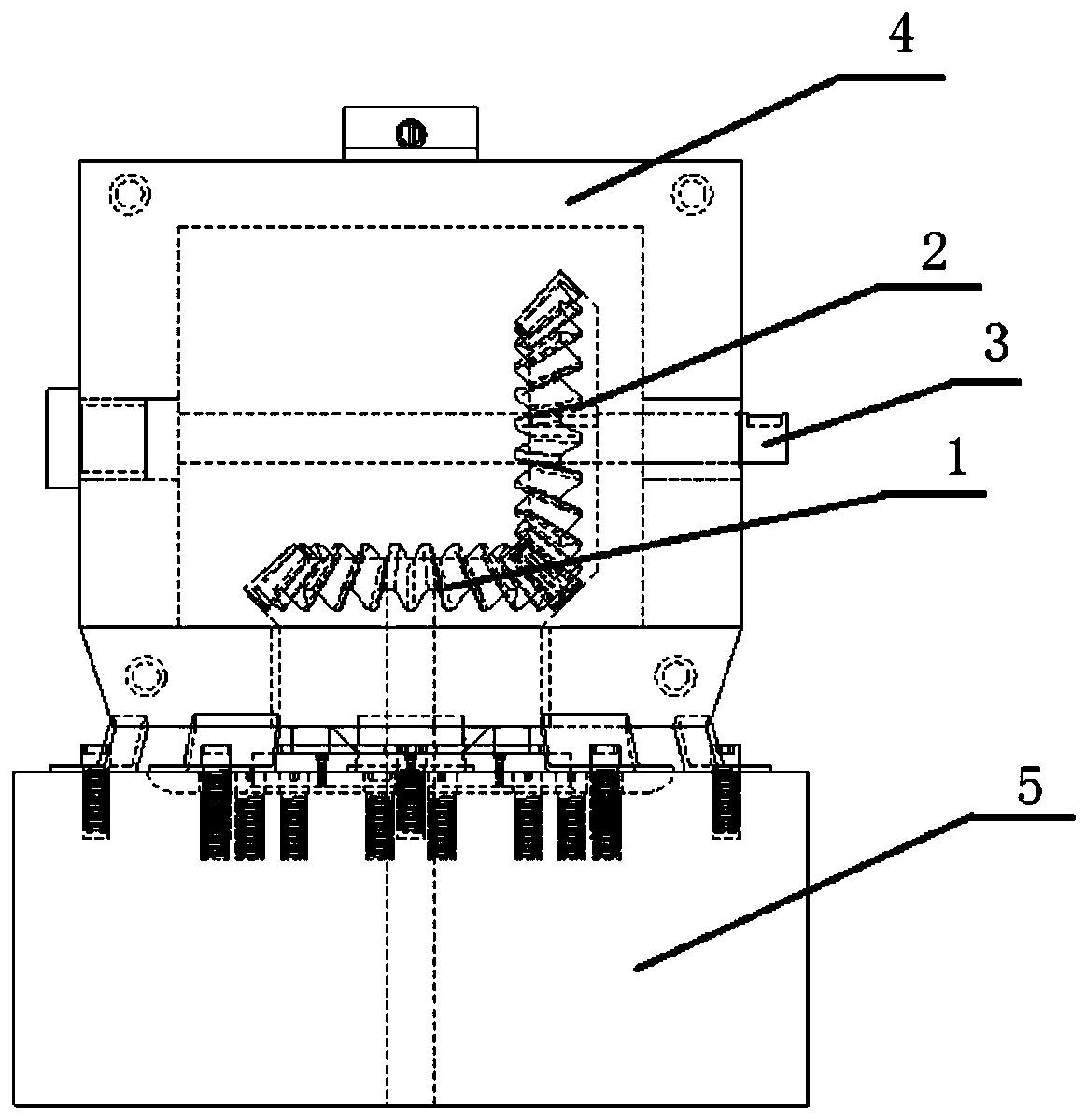

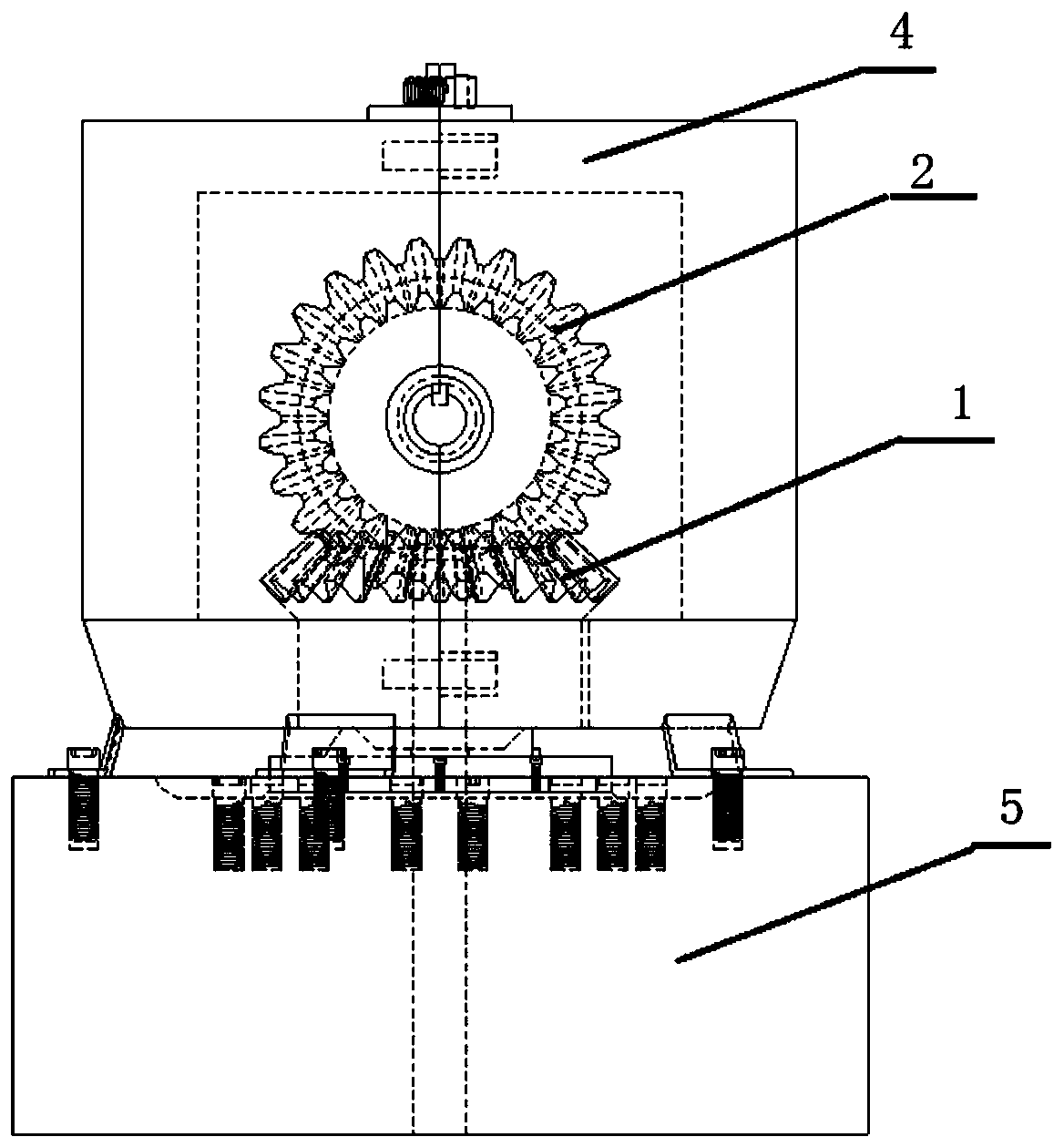

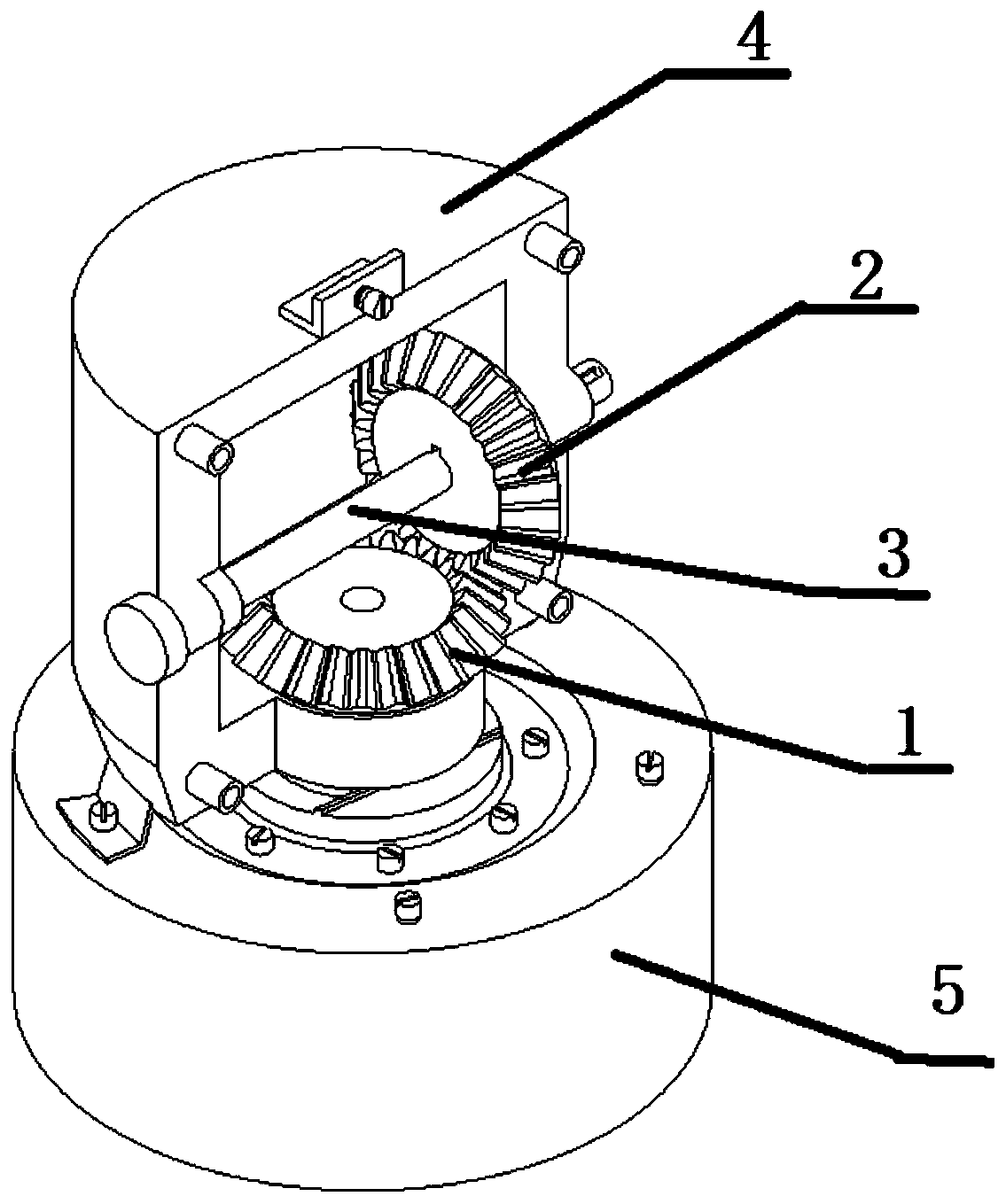

In-situ failure analysis sample table and scanning electron microscope

PendingCN110010435AEnables in-situ failure analysisRealize arbitrary flip observationMaterial analysis using wave/particle radiationElectric discharge tubesScanning electron microscopeElectron microscope

The invention provides an in-situ failure analysis sample table and a scanning electron microscope. The in-situ failure analysis sample table comprises a reversing portion, a clamping portion and a driving portion, wherein the reversing portion includes a first bevel gear and a second bevel gear, and the first bevel gear is meshed with the second bevel gear; the first bevel gear is sleeved and fixed on a first gear shaft; the second bevel gear is sleeved and fixed on a second gear shaft; the clamping portion is installed on the end part of the second gear shaft and used for clamping a sample;and the driving portion is connected with the first gear shaft and used for driving the first bevel gear to rotate, driving the second bevel gear to rotate in-situ and thus driving the sample to rotate by 360 degrees around the second gear shaft so as to achieve in-situ failure analysis of the sample.

Owner:SHANDONG ANALYSIS & TEST CENT

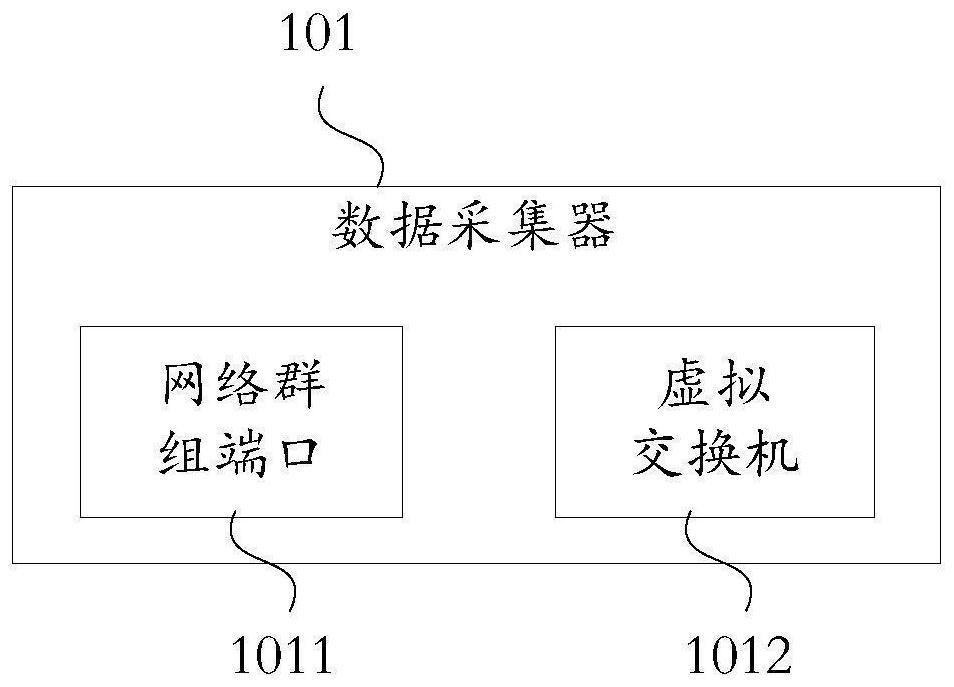

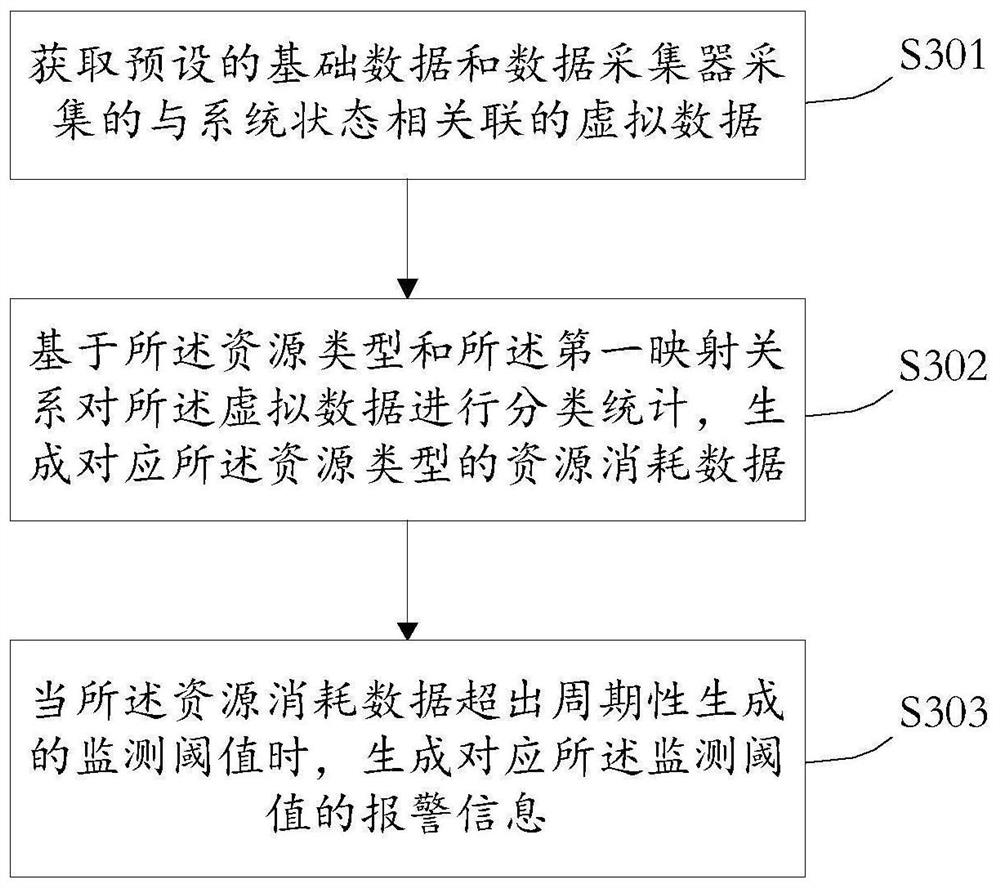

A method and system for monitoring virtual data

PendingCN112214281AImprove monitoring efficiencyLow costSoftware simulation/interpretation/emulationVirtualizationProcessing type

The invention provides a method and a system for monitoring virtual data. Service application quality is taken as guidance, virtual data is subjected to classified statistics based on the resource types in the basic data, the resource consumption data corresponding to the resource types under the data processing types is generated, and then the resource consumption data is analyzed through the monitoring threshold value to generate the alarm information corresponding to the monitoring threshold value. Automatic hierarchical monitoring and alarming are realized for a complex network architecture in a virtualized data center, the monitoring efficiency is improved, and an effective guarantee is provided for stable operation of service applications.

Owner:明辰智航(北京)测试技术有限公司

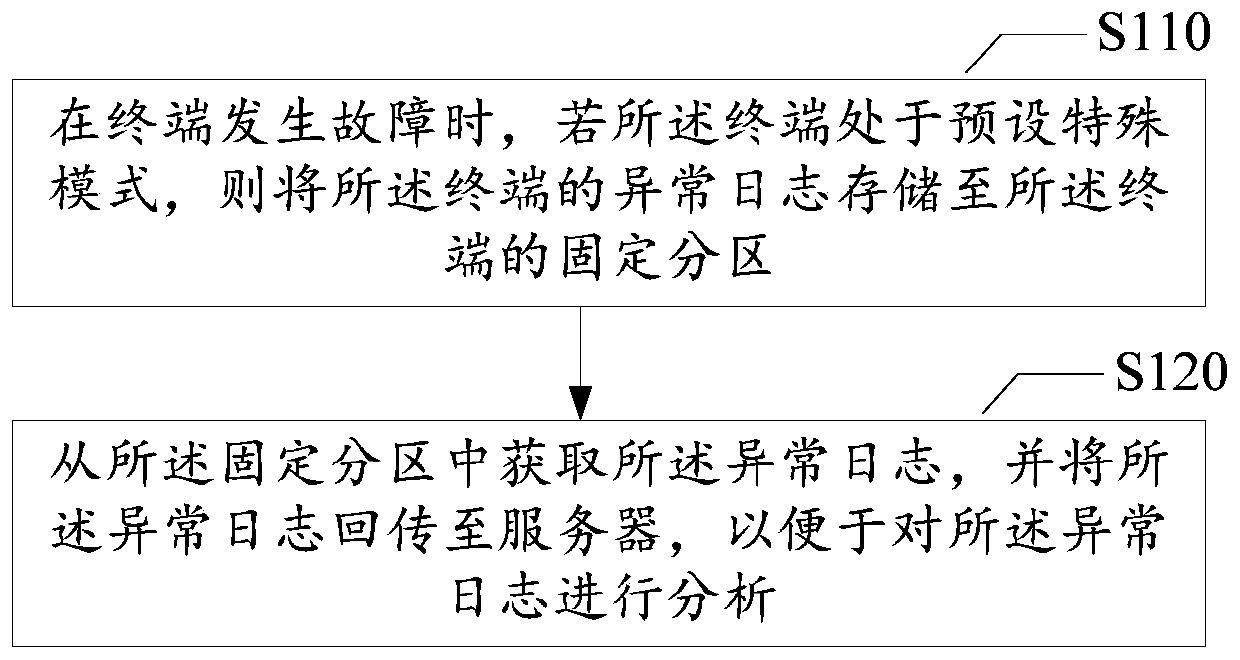

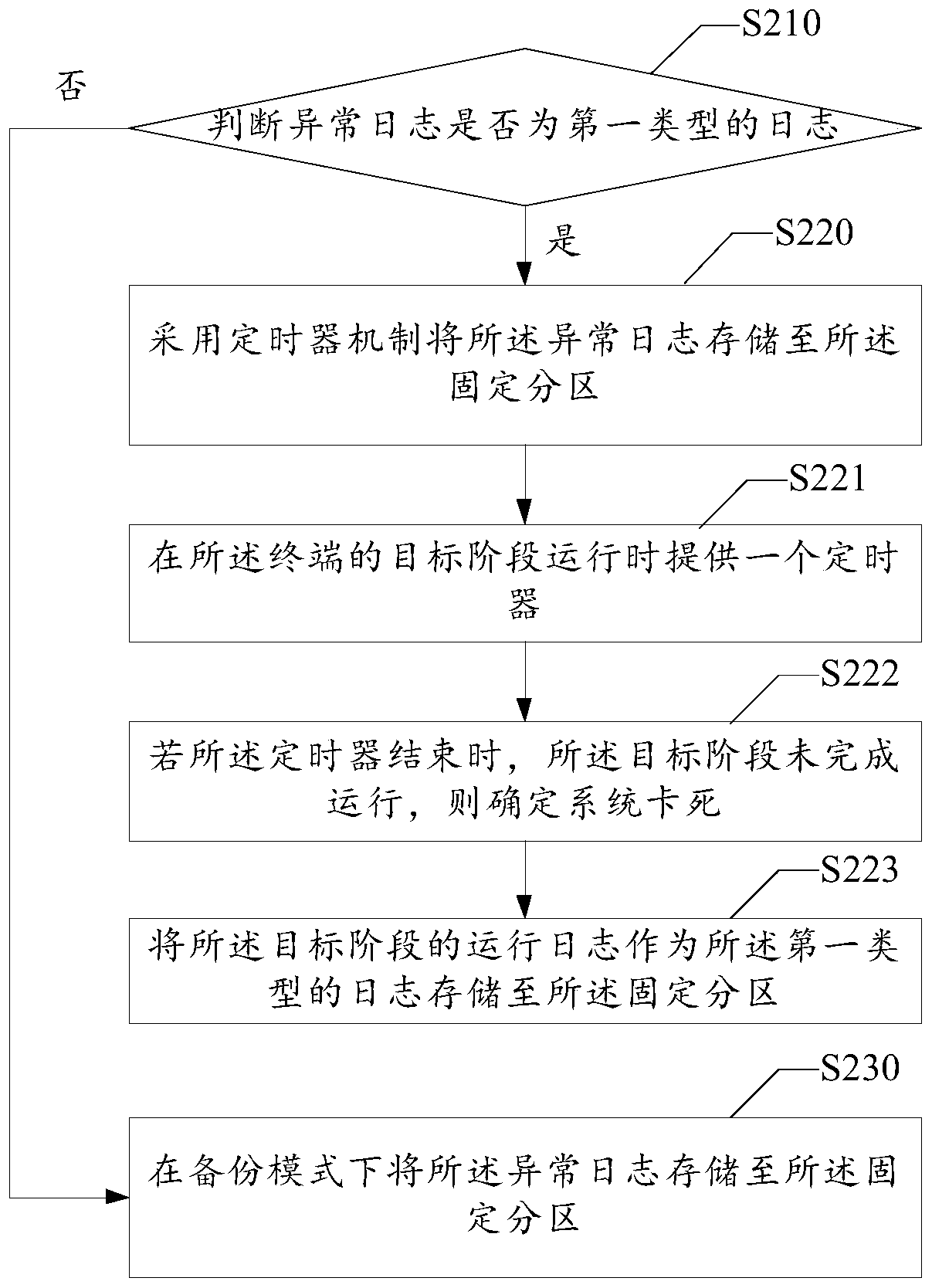

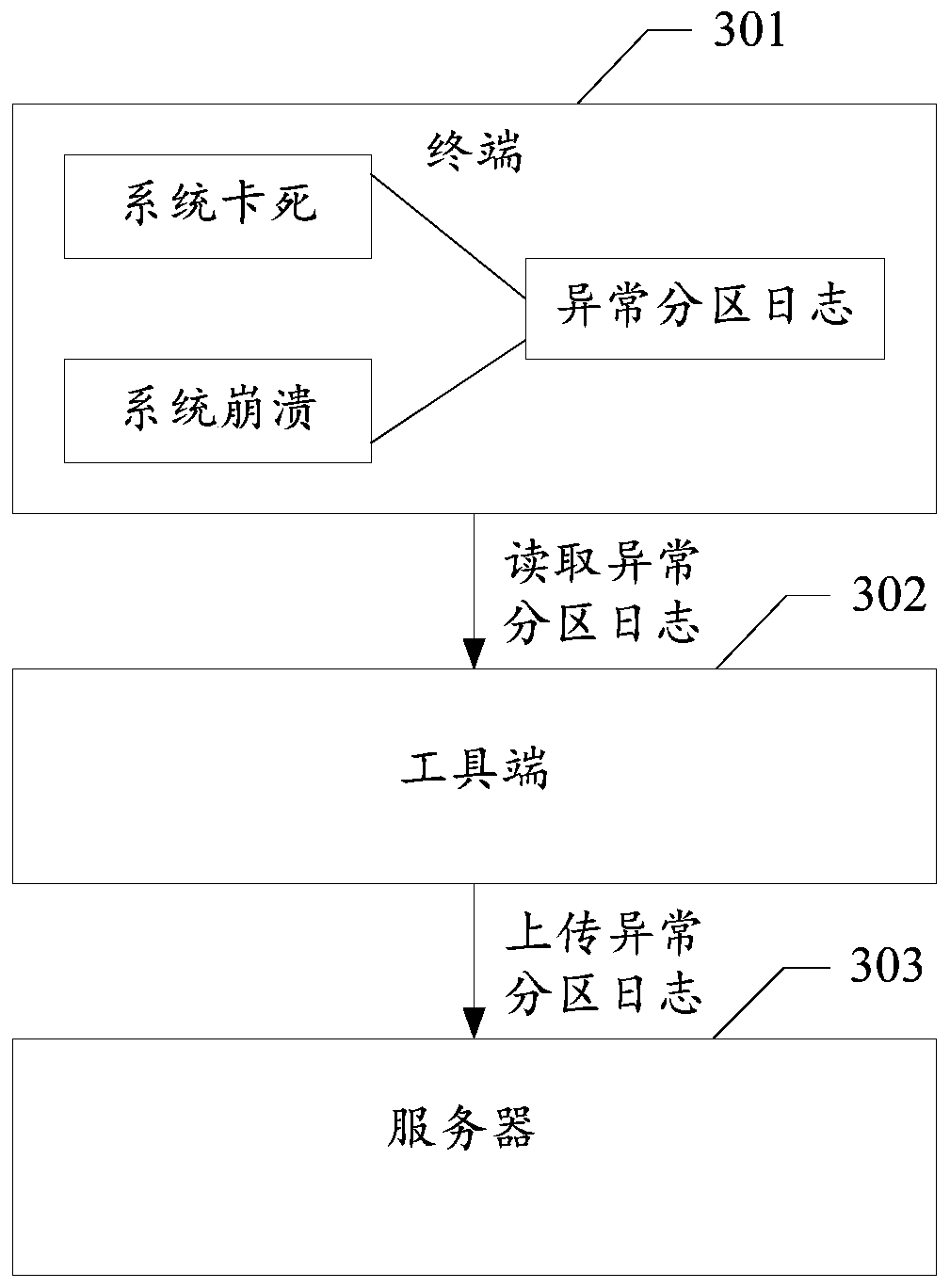

Abnormal log processing method and device, electronic equipment and storage medium

ActiveCN110333964AEasy to analyzeImprove efficiencyFault responseHardware monitoringComputer hardwareElectronic equipment

The invention relates to an abnormal log processing method and device, electronic equipment and a storage medium, and relates to the technical field of computers. The method comprises the steps that when a terminal breaks down, if the terminal is in a preset special mode, storing an abnormal log of the terminal in a fixed partition of the terminal; and obtaining the abnormal log from the fixed partition, and returning the abnormal log to a server so as to analyze the abnormal log. The abnormal log can be uploaded in time, and rapid and accurate analysis can be carried out according to the abnormal log when the terminal cannot be started.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

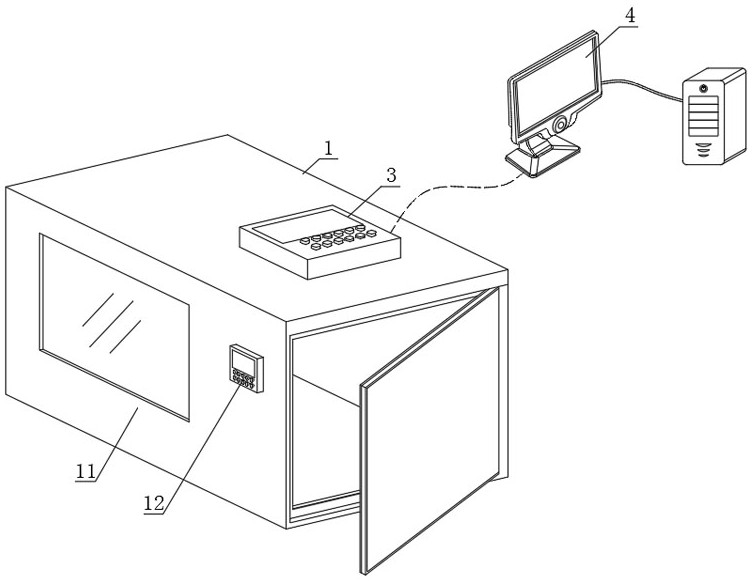

Visual intelligent management system for intelligent laboratory

ActiveCN114240406AHigh precisionQuality assuranceTelevision system detailsMeasurement devicesExperimental laboratoryThe Internet

The invention discloses a visual intelligent management system for an intelligent laboratory, belongs to the technical field of intelligent laboratories, and aims to solve the problem that the interior of the laboratory cannot be reasonably managed by using an existing laboratory. The existing internal experiment data cannot be well recorded and stored, data disorder is easily caused, the experiment can only be performed on site, real-time teaching cannot be performed on the internet, and the visualization efficiency is low. According to the intelligent laboratory visual intelligent management system, information can be transmitted in real time, the quality of the internal environment in the experiment process is guaranteed, real-time monitoring is achieved, understanding can be carried out at any time, experimenters are reminded to carry out processing, the experiment safety is effectively guaranteed, the management efficiency can be guaranteed in real time, and the management efficiency is improved. According to the invention, comprehensive intelligent management of laboratory places, personnel, equipment, environment and safety guarantee is realized, classroom reservation information can be displayed in non-class time periods in a class schedule area, the monitoring management efficiency of the laboratory places is improved, and the convenience of real-time reservation is also ensured.

Owner:SHENZHEN UNIV

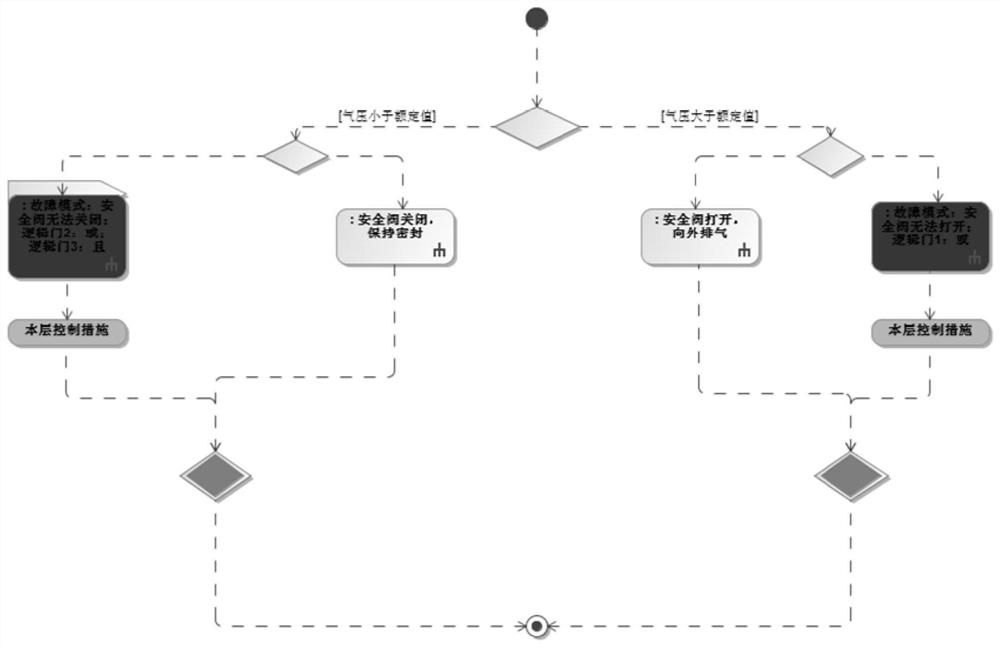

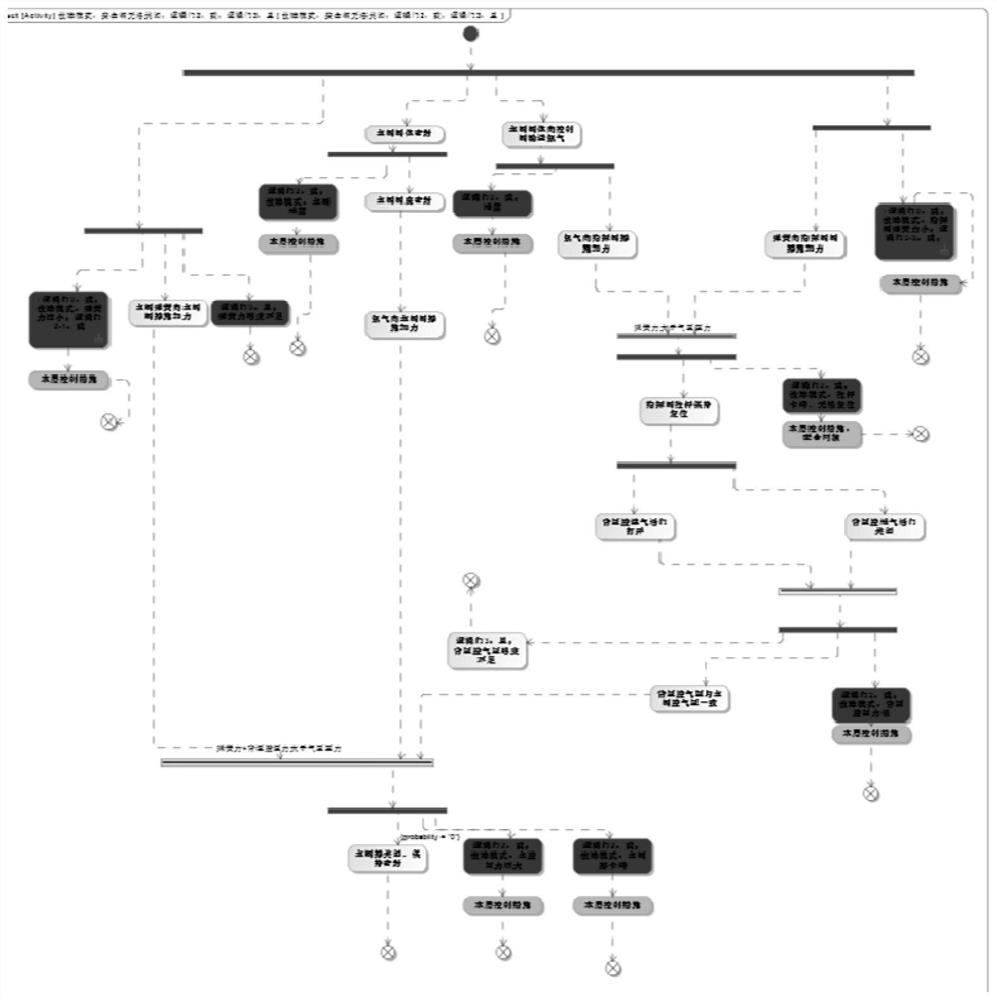

FTA and FMEA integrated analysis method based on MBSE

PendingCN114218772AImprove consistencyImprove the efficiency of failure analysisDesign optimisation/simulationSpecial data processing applicationsAlgorithmActivity diagram

The invention provides an MBSE-based FTA and FMEA integrated analysis method. The MBSE-based FTA and FMEA integrated analysis method comprises the following steps: S1, determining an analysis object; performing function design by adopting an activity graph in the MBSE; s2, carrying out fault analysis on each module in the activity graph, listing corresponding faults of functional modules, and indicating a relationship; s3, along with layer-by-layer refinement of the function design of the MBSE, continuing to implement the step S2 at the corresponding level; s4, the MBSE is operated, and EXCEL is output; s5, the EXCEL is read through a plug-in, data are processed, and FTA and FMEA are automatically generated at the same time; and S6, the design process information is maintained in time, and the steps S2 to S5 are repeated. According to the method, the MBSE theory and method are utilized, fault analysis is synchronously carried out with function design, and FMEA and FTA are integrally implemented; the consistency of fault analysis information is improved, and the efficiency of fault analysis is improved.

Owner:SHANGHAI AEROSPACE SYST ENG INST

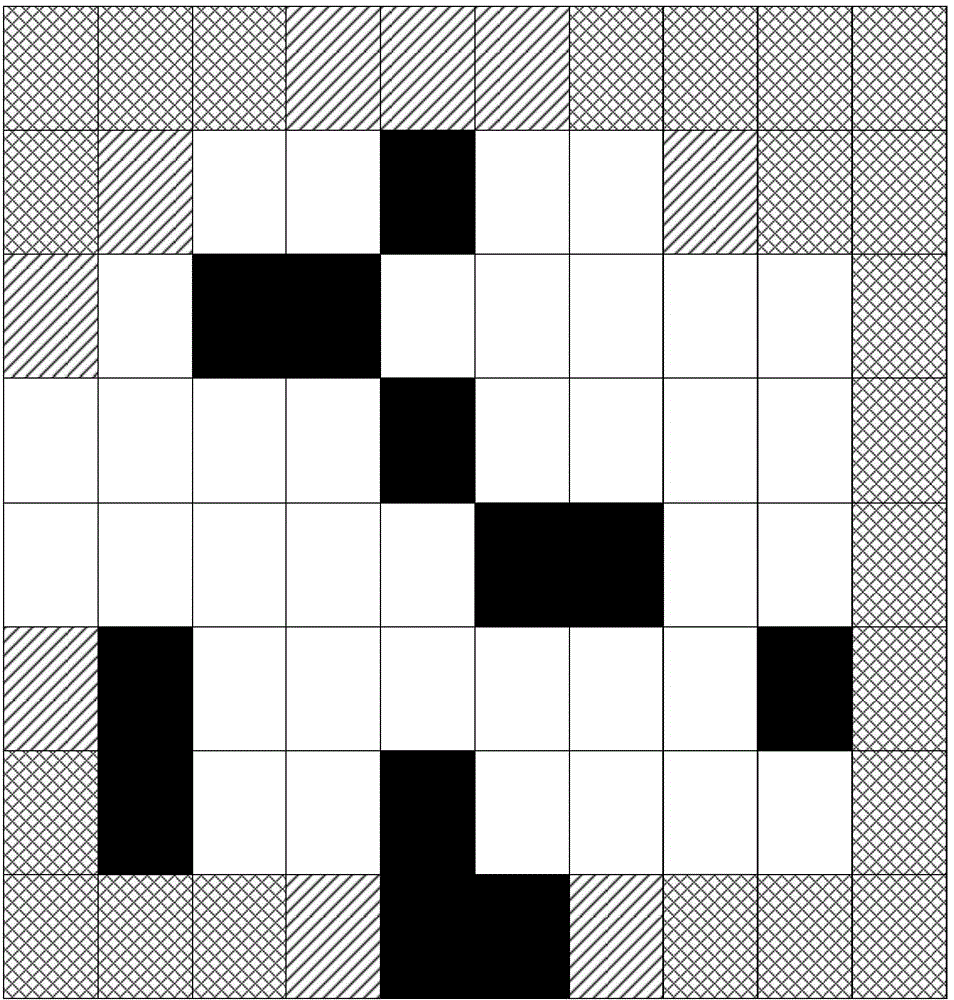

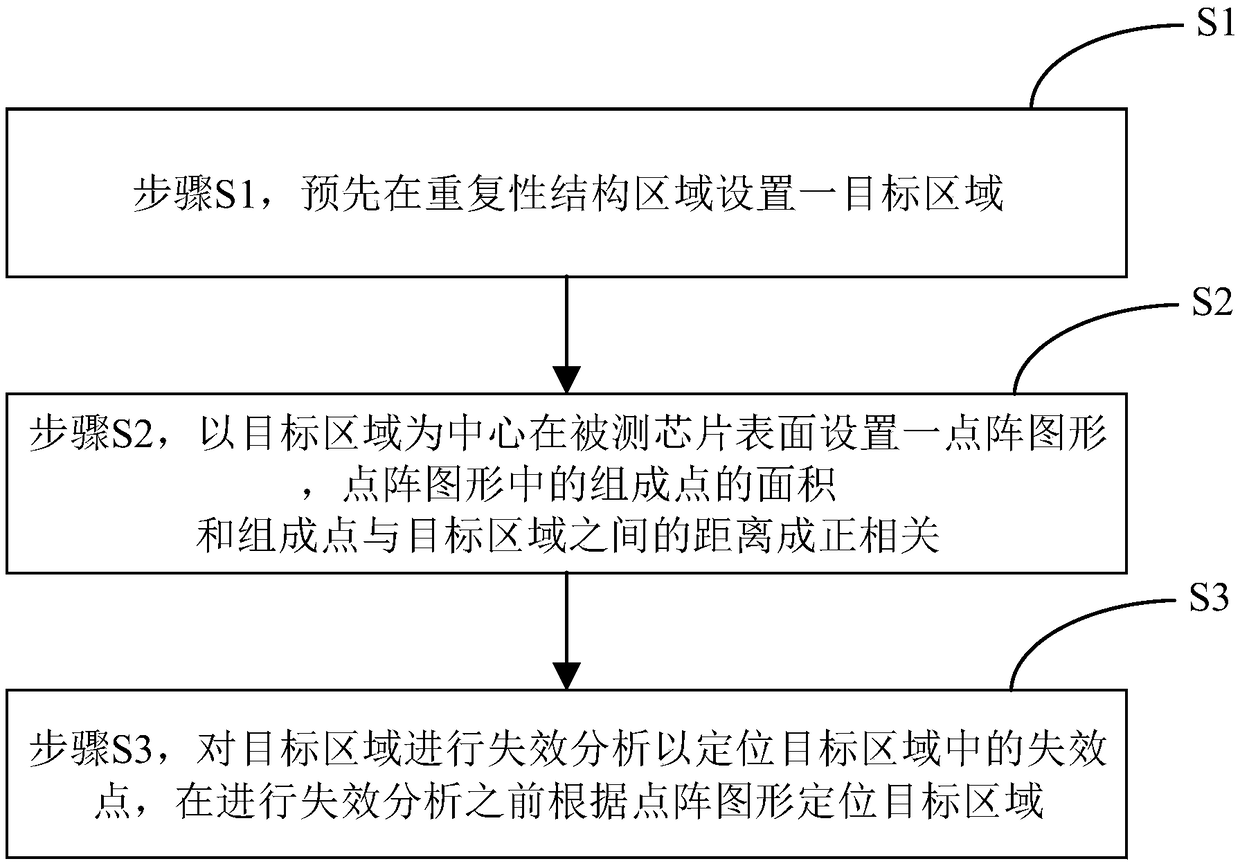

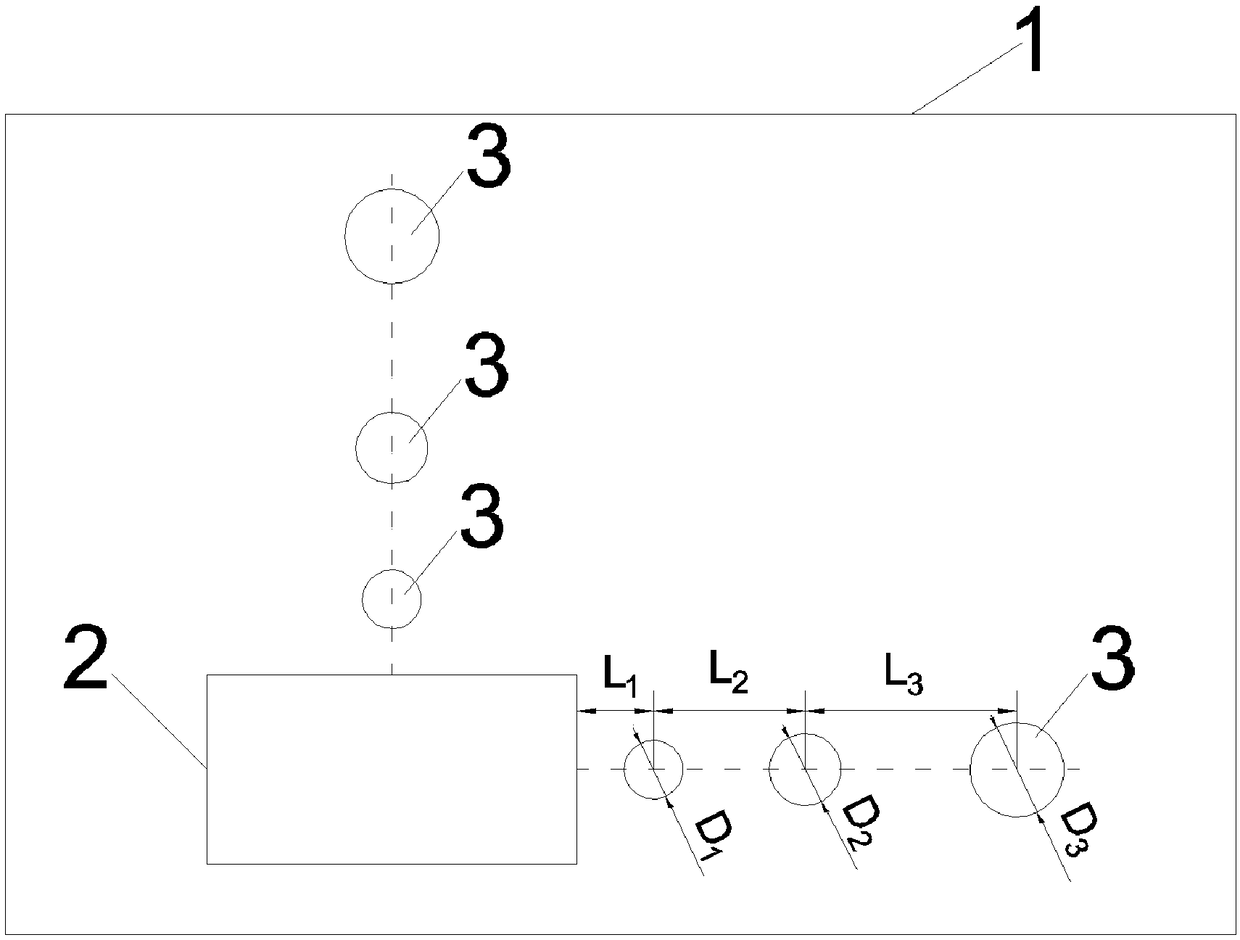

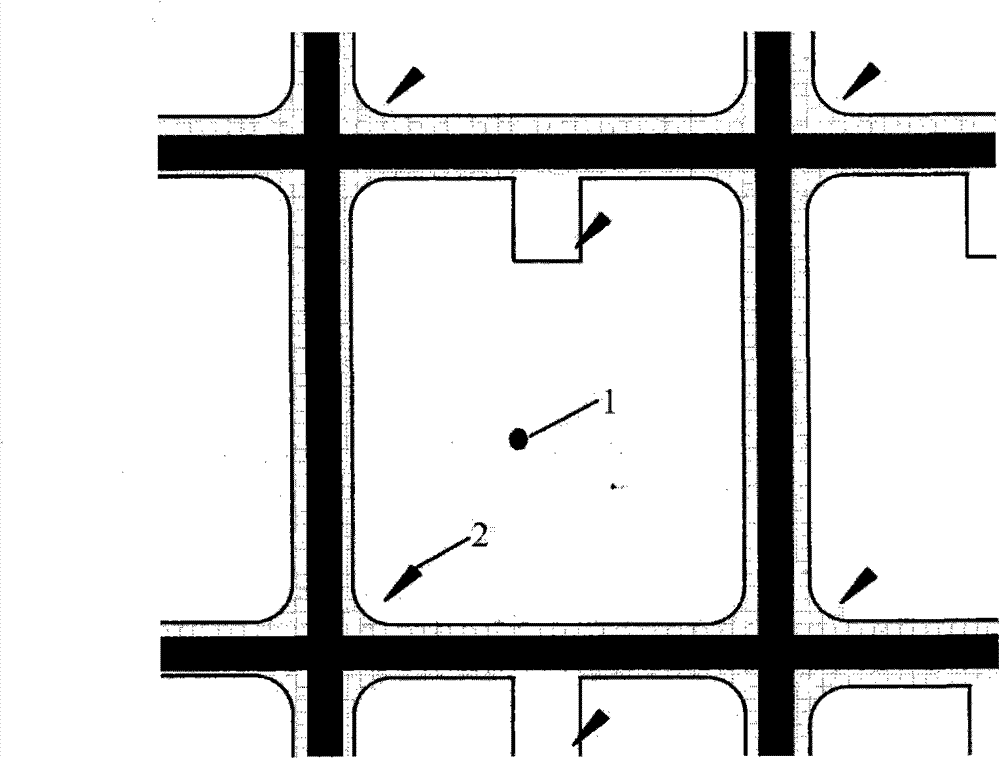

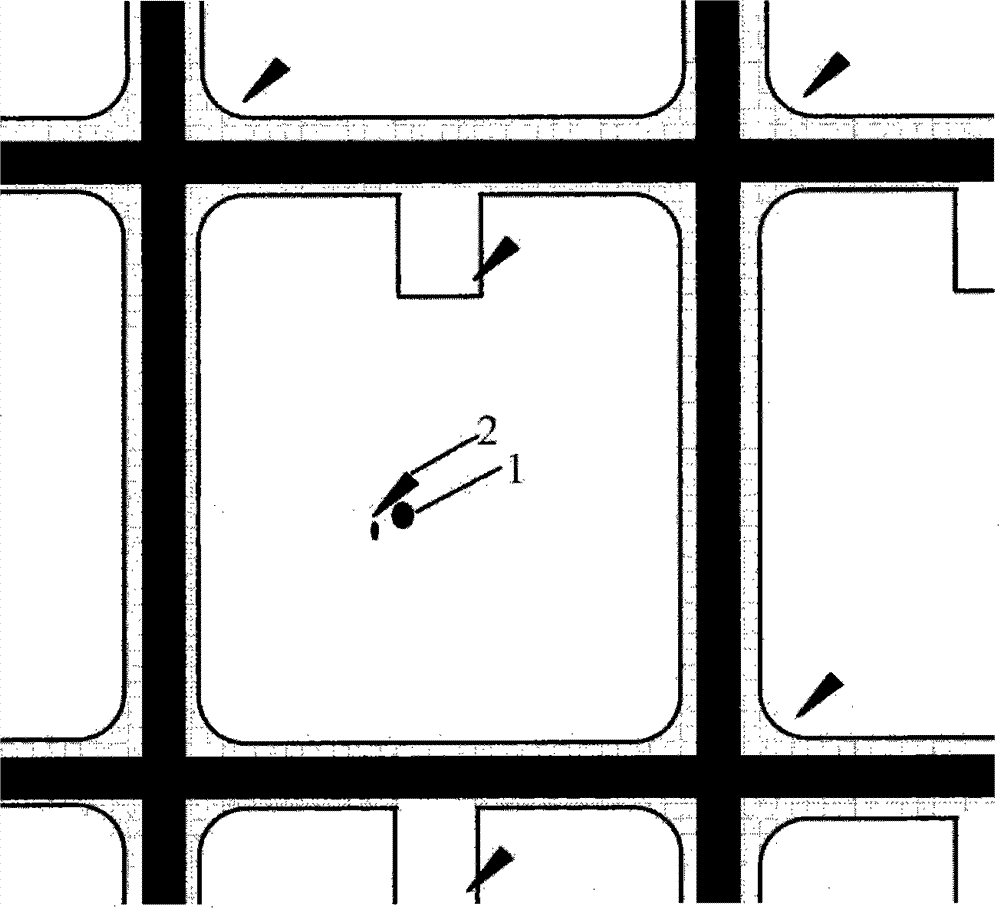

Failure analysis positioning method

InactiveCN108918552ARapid positioningQuick analysisMaterial analysis by optical meansGraphicsDot matrix

The invention discloses a failure analysis positioning method, and belongs to the technical field of semiconductors. The failure analysis positioning method comprises the following steps: steps S1, arranging a target area in a repetitive structural region in advance; step S2, arranging a dot-matrix graphic on the surface of a tested chip by taking the target area as a center, the area of composition dots in the dot-matrix graphic is in positive correlation with the distance between the composition dots and the target area; step S3, performing failure analysis on the target area to position failure dots in the target area, positioning the target area according to the dot-matrix graphic before performing the failure analysis. The beneficial effect of the failure analysis positioning method is that the time of grasping the failure dots can be reduced, so that the failure analysis can be performed quickly, the efficiency of the failure analysis is improved, and the fast positioning and analysis of the failure dots in the repetitive structural area on the chip are realized.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Semiconductor structure for testing mim capacitance

ActiveCN103367329BEasy to makeLow costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCapacitanceSemiconductor structure

A semiconductor structure for testing MIM capacitance, which is divided into multiple layers, including: a first metal layer, at least including a first circuit area and a second circuit area; a second metal layer, arranged on the first Below the metal layer, it is electrically connected to the second circuit area; the upper plate is located in the dielectric layer close to the first metal layer, and is electrically connected to the first circuit area; the lower plate is arranged opposite to the upper plate. In the dielectric layer close to the second metal layer, it is separated from the upper plate by an insulating layer and electrically connected to the second circuit area; the structure is formed on a P-type substrate, and the second metal layer is connected to the semiconductor substrate. The bottom is electrically connected by a first circuit path to form a second circuit path from the upper plate to the semiconductor substrate when there is a leakage region in the insulating layer. The method can accurately detect whether there is a leakage area in the MIM capacitor; the preparation is simple and the cost is low; and it is especially suitable for quickly locating the leakage area of a large-area MIM capacitor.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Power Grid Fault Auxiliary Analysis System

ActiveCN104502797BMeet needsRealize real-time monitoringFault locationMass storageHuman–machine interface

A power grid fault auxiliary analysis system, including a main control module, the main control module is connected to a multi-channel voltage input module, a multi-channel current input module, a multi-channel switch value input module, a large-capacity storage module, a man-machine interface, an external Communication module and grid fault auxiliary analysis system knowledge base; real-time display of three-phase voltage, three-phase current waveform, effective value, cycle, frequency, real-time display of single-phase or three-phase reactive power, active power, and apparent power value; from all Randomly select 1 to 8 AC quantities in the AC analog channel to display their phasor diagrams. The phase of the first phasor is fixed as the reference, and the other phasors are drawn according to the phase relative to the reference phasor, and Display the effective value and phase angle of the phasor. According to the three-phase voltage or three-phase current, the positive sequence, negative sequence, zero sequence effective value and phase angle can be displayed in real time, and it has two harmonic analysis methods.

Owner:SHANGHAI HEKAI ELECTRICAL TECH

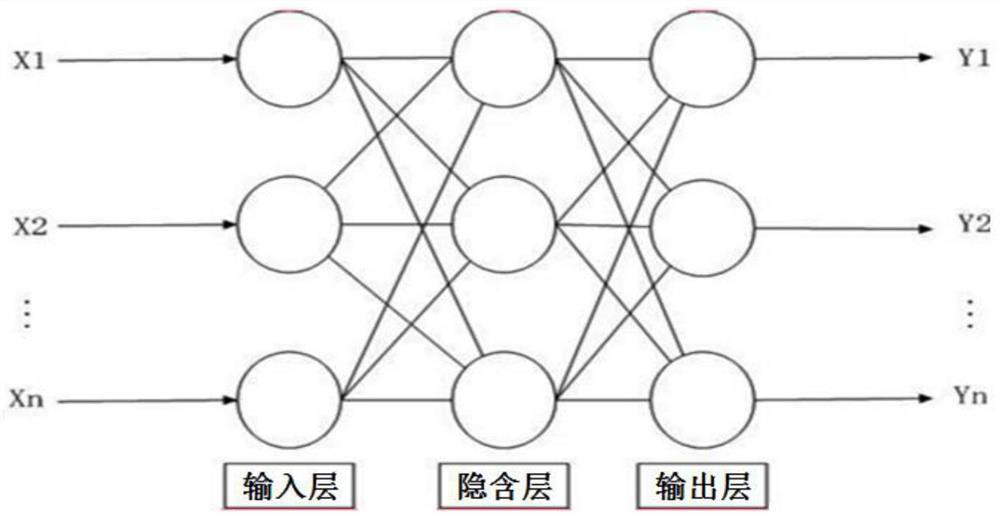

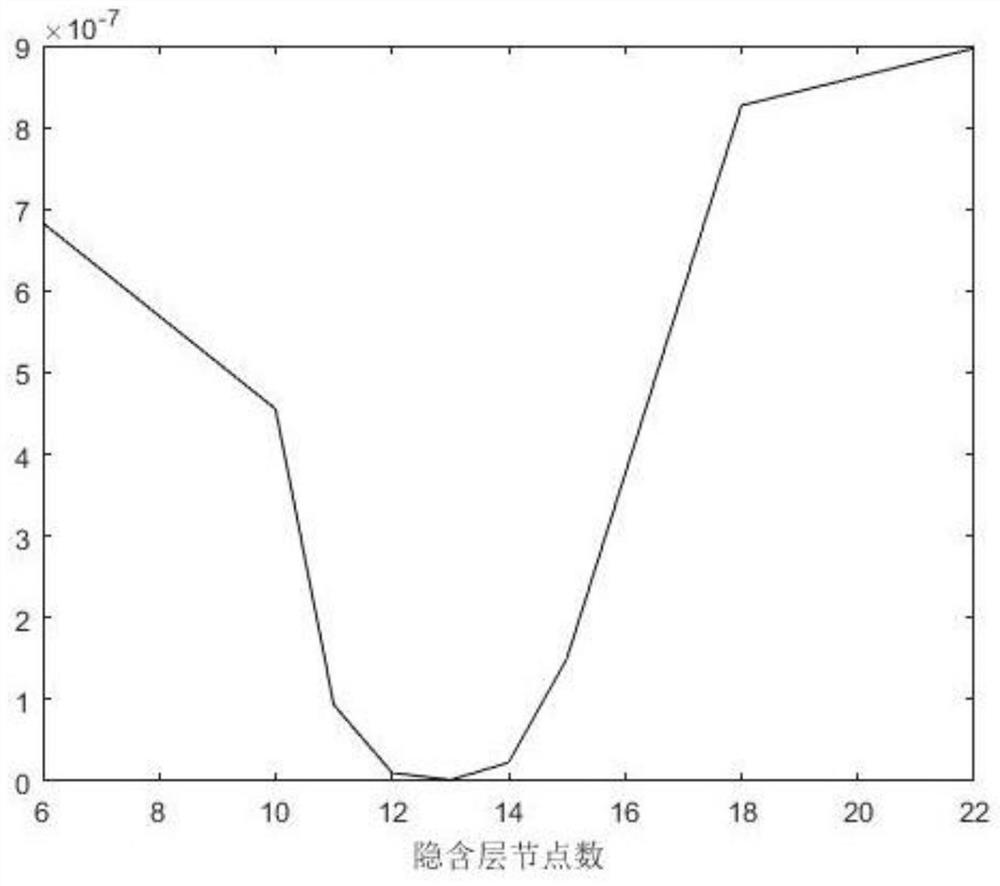

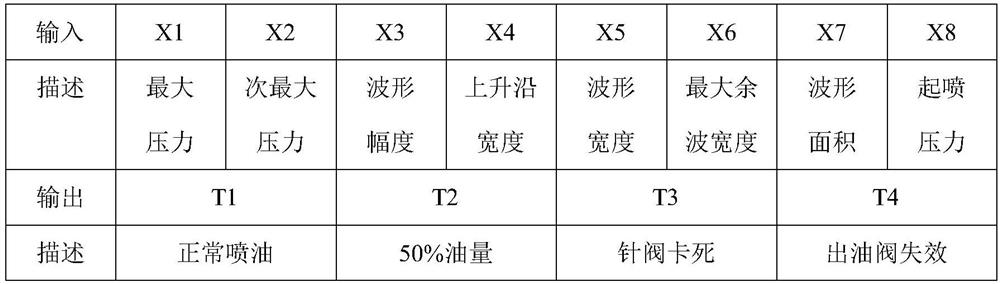

Engine fault diagnosis method based on bp neural network

ActiveCN110470481BEffective positioningOptimize output dataInternal-combustion engine testingNeural architecturesHidden layerEngineering

The invention discloses a method for diagnosing engine faults based on BP neural network, comprising (1) collecting engine fault data and listing the causes of engine faults; (2) determining the optimal hidden layer node number of BP neural network model, and establishing Neural network model; (3) Train the BP neural network model according to the existing fault data; (4) Use the trained BP neural network model to analyze the collected engine data to determine the cause of the fault corresponding to the data. In the past, engine fault diagnosis had defects such as complex mechanism, low detection accuracy, high cost, and failure to display the cause of the fault. The present invention is mainly used in engine fault diagnosis and diagnosis, which is more advantageous than previous methods, saves costs, and improves modeling Efficiency, can quickly lock the optimal number of hidden layer nodes.

Owner:舯南氢能动力科技(无锡)有限公司

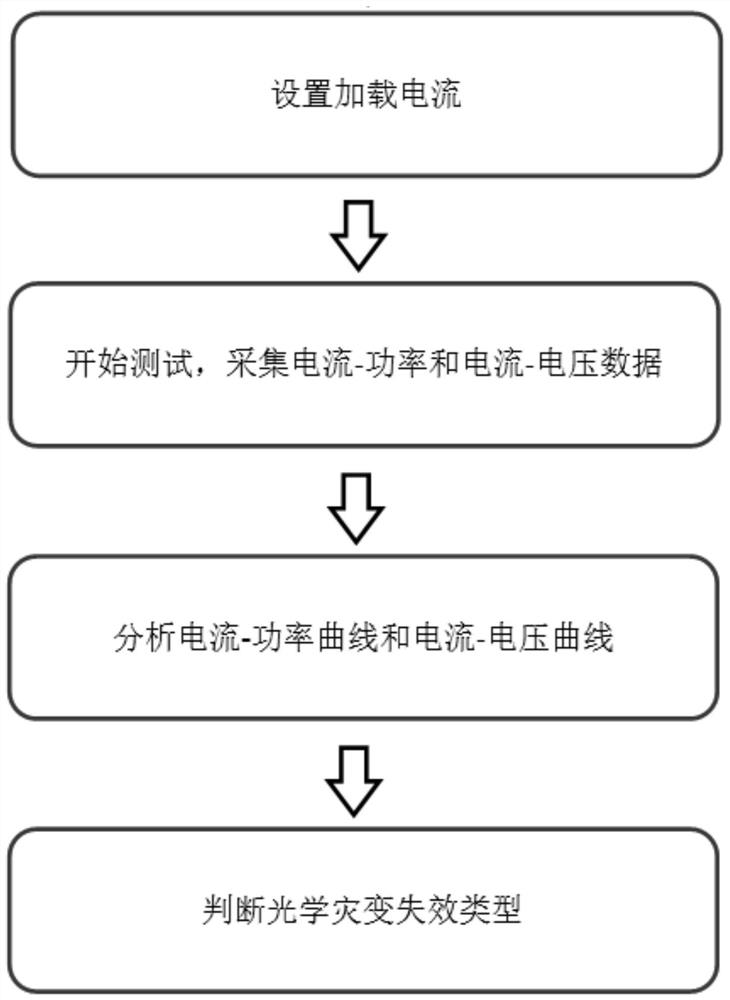

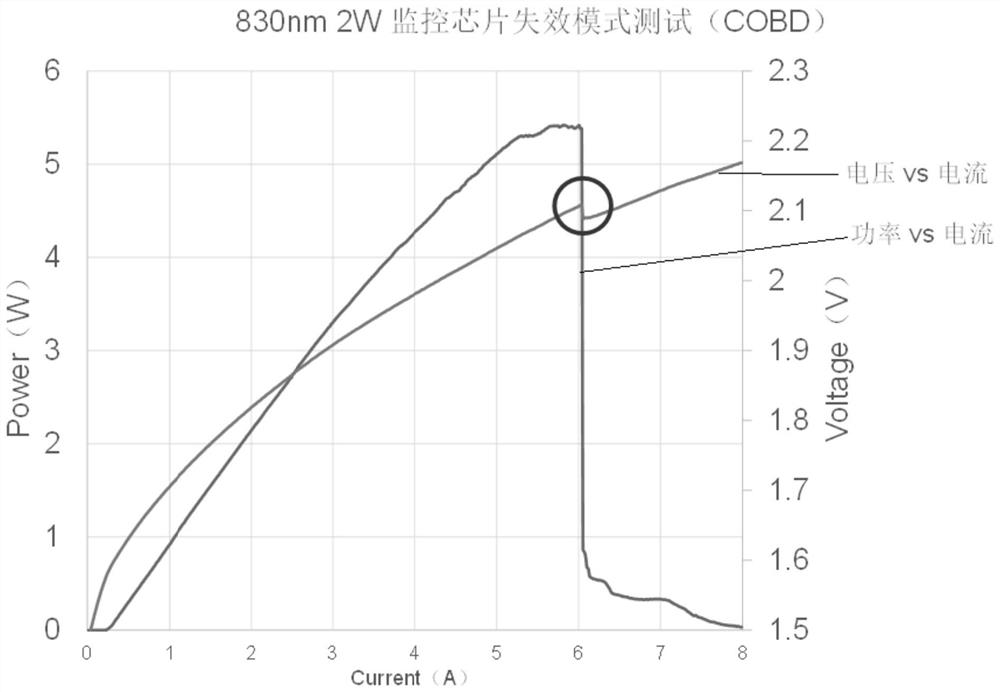

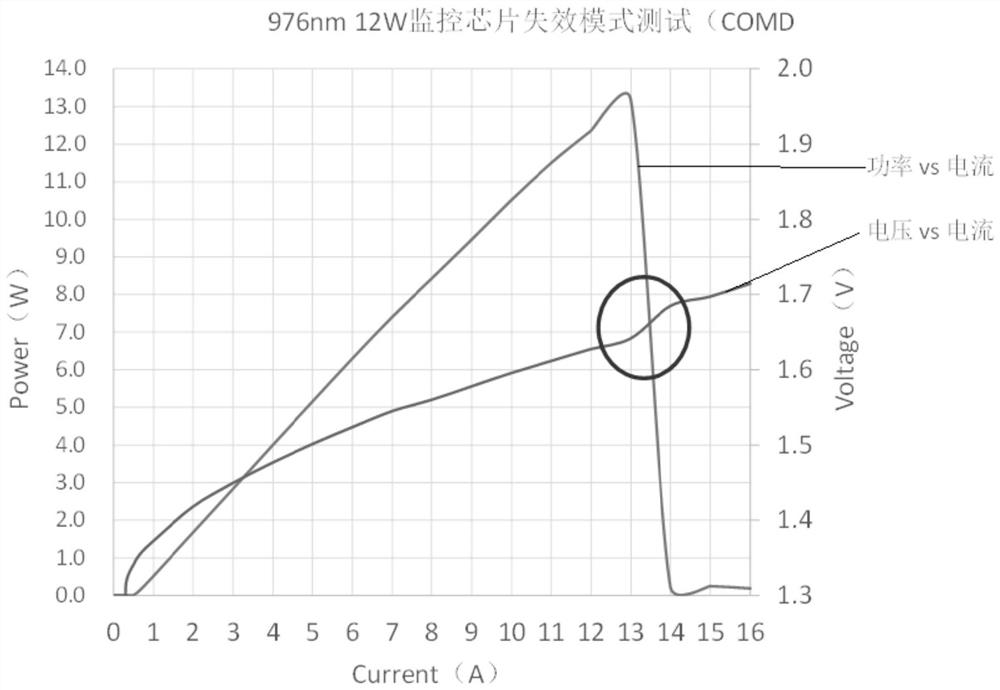

A method for judging optical catastrophe type of semiconductor laser chip

ActiveCN111934186BLow costJudgment failureLaser detailsSemiconductor lasersComputational physicsErbium lasers

The invention provides a method for judging the optical catastrophe type of a semiconductor laser chip, which solves the problems of high judgment cost, long judgment time and low production efficiency of existing semiconductor laser chips COBD and COMD. The method includes: Step 1, setting the loading current; Step 2, loading the loading current on the semiconductor laser chip; Step 3, collecting the current-power curve and current-voltage curve of the semiconductor laser chip; Step 4, if the current-power curve If the current-voltage curve suddenly drops and the current-voltage curve suddenly rises, it is judged that the optical catastrophe of the chip is COMD; if the current-power curve suddenly drops and the current-voltage curve suddenly drops, it is judged that the optical catastrophe of the chip is COBD. The method of the present invention does not require professional equipment, and only needs to collect the current, power value and voltage value in the test process to judge COBD and COMD. The detection equipment is simple and the cost is low, and only ordinary technicians can realize the judgment of failure .

Owner:灵素医疗科技(陕西)有限公司

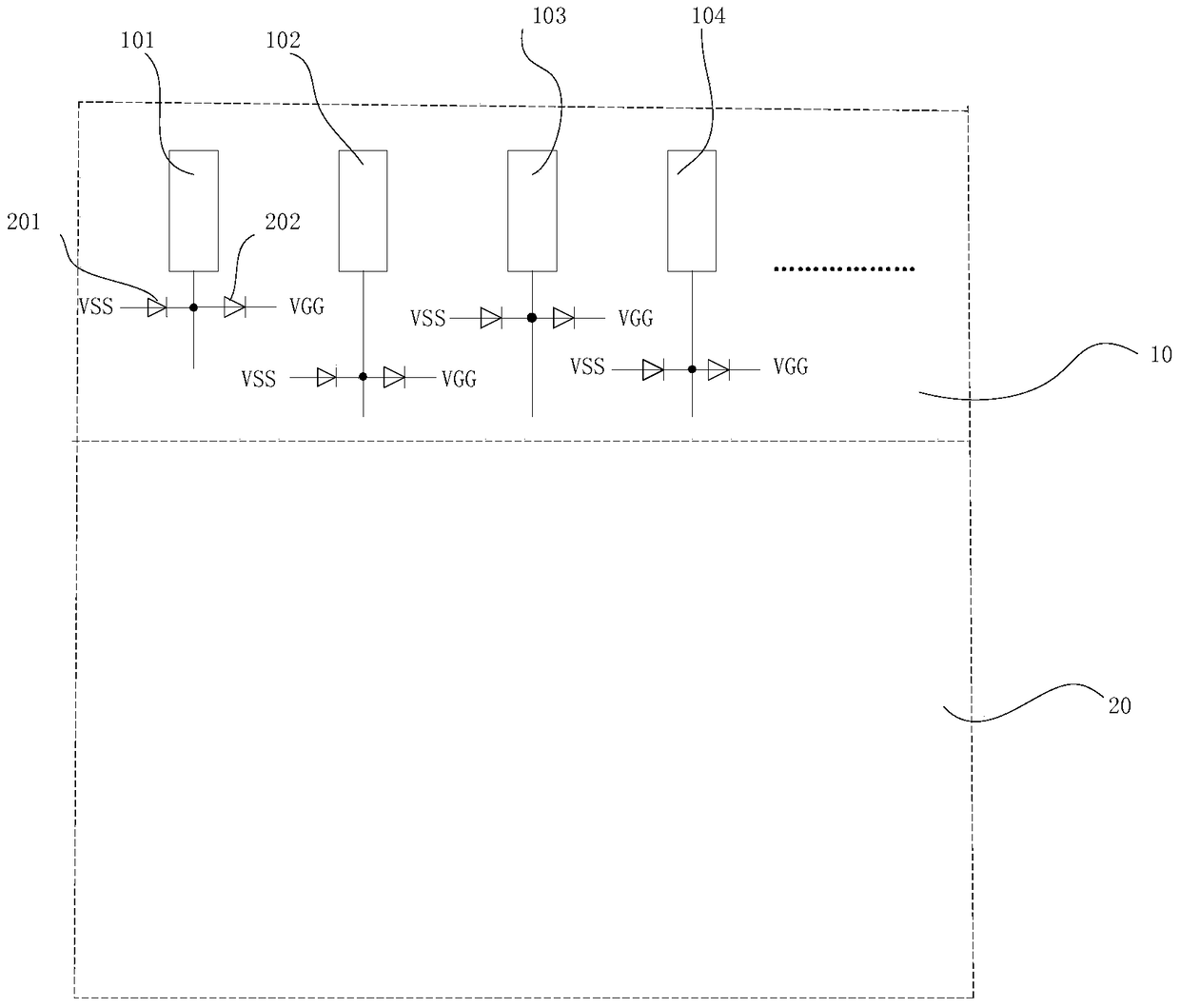

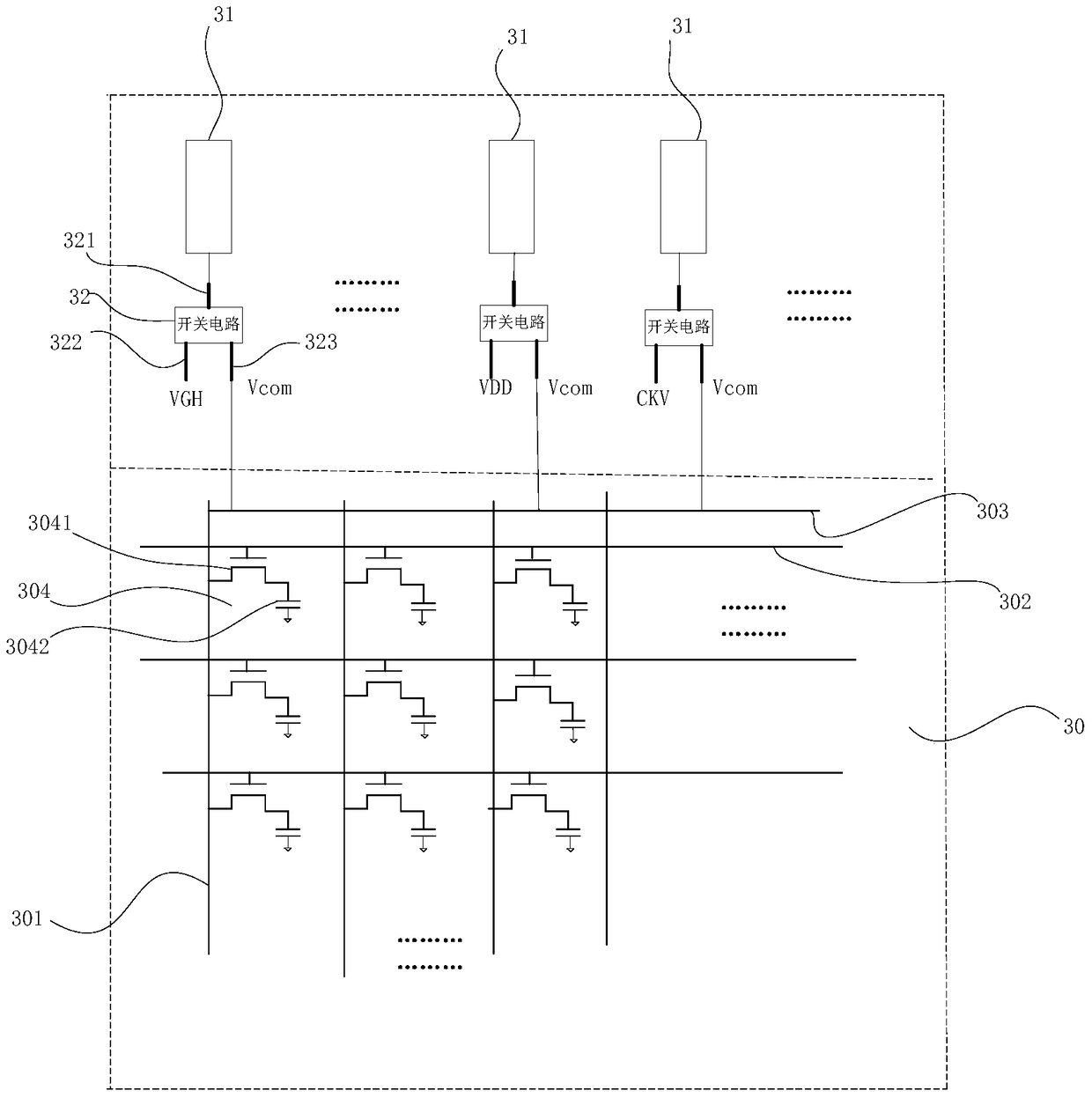

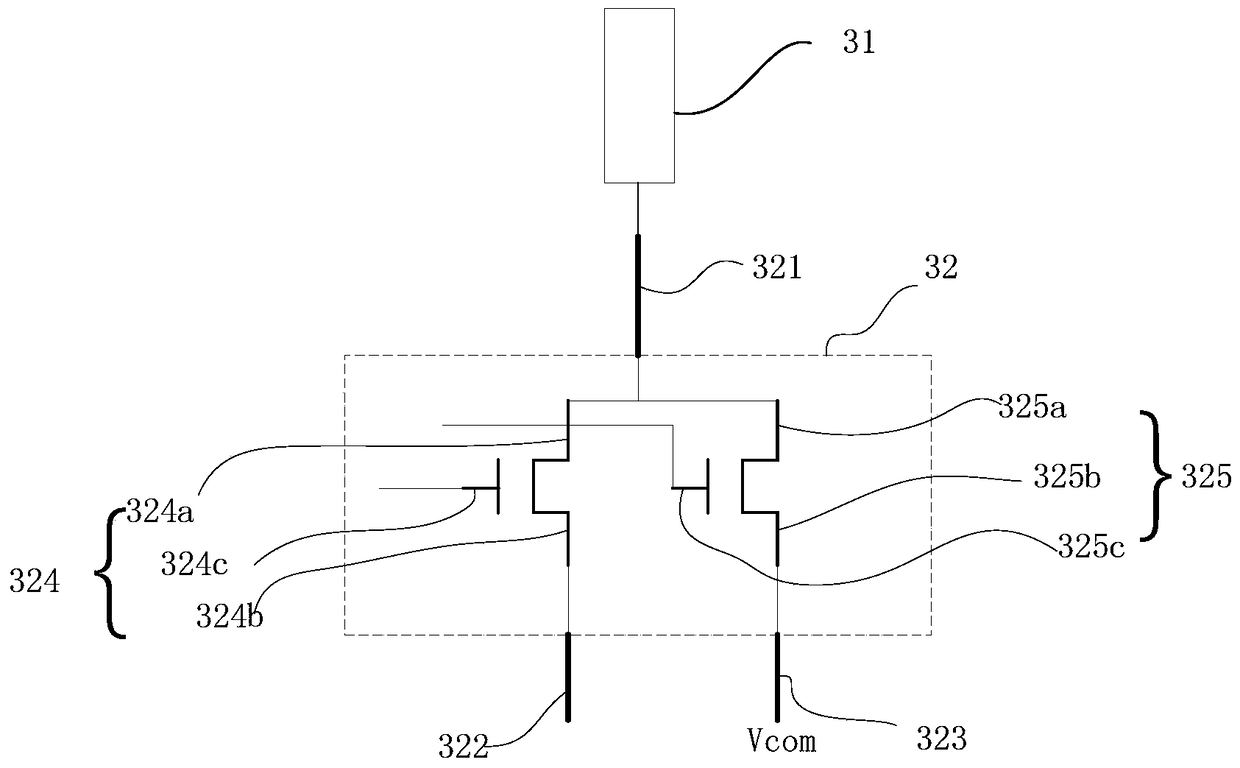

A liquid crystal display panel

ActiveCN105070239BExtended service lifeAvoid damageStatic indicating devicesNon-linear opticsLiquid-crystal displayStatic electricity

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

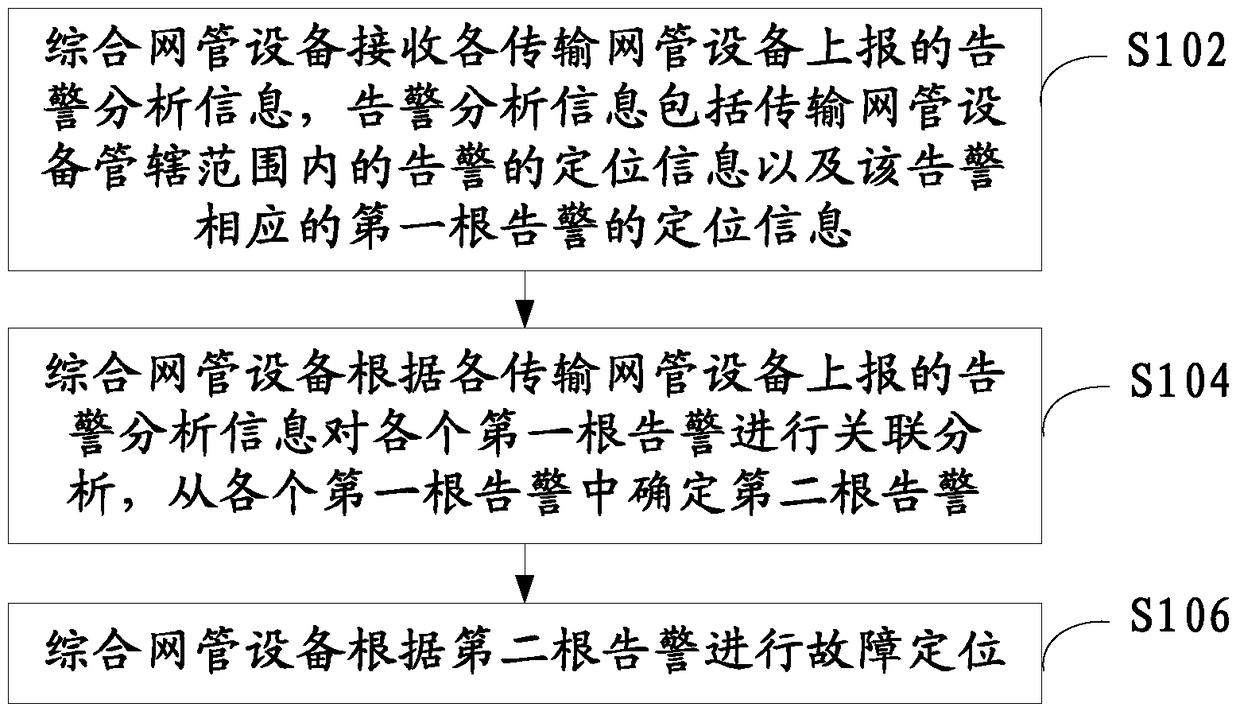

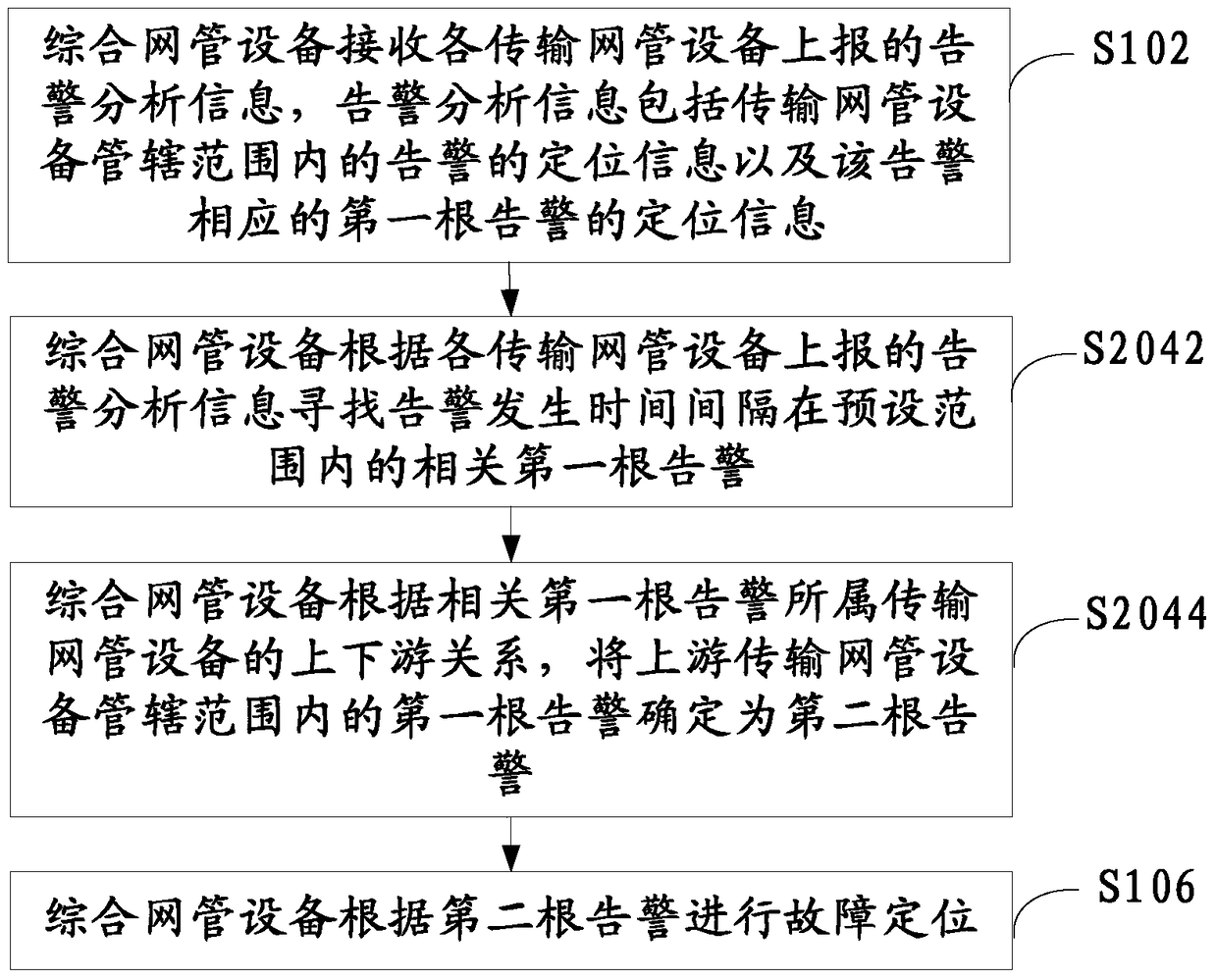

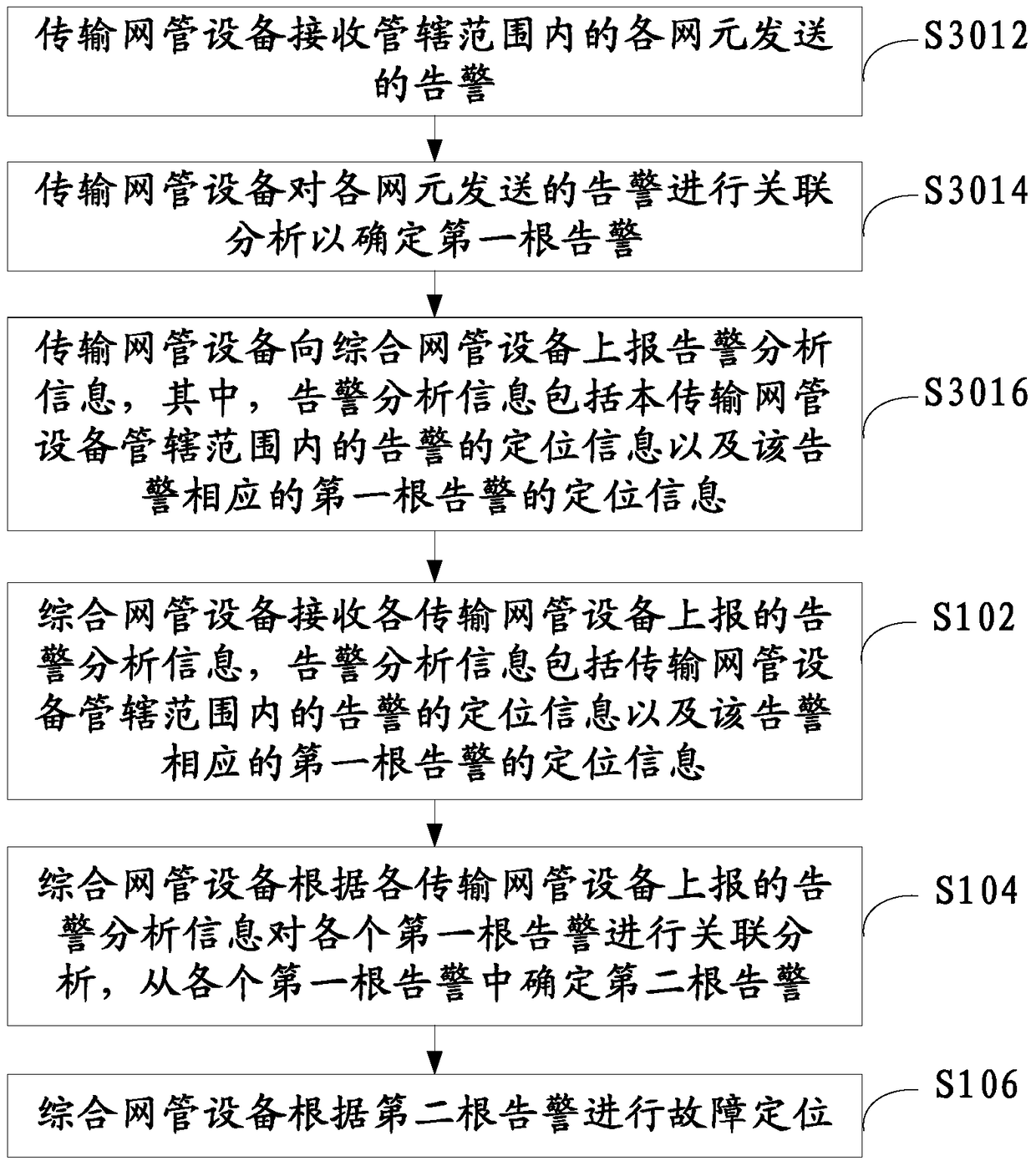

Fault analysis method and system and network management equipment

ActiveCN105071970BAlarm data reductionImprove the efficiency of failure analysisData switching networksNetwork managementFault analysis

The invention discloses a failure analysis method, a failure analysis system and network management equipment. Comprehensive network management equipment can obtain positioning information of alarms in a jurisdiction range of transmission network management equipment and positioning information of a first alarm corresponding to the alarms by receiving alarm analysis information reported by various transmission network management equipment; then, when further analyzing, the comprehensive network management equipment is only necessary to perform association analysis of various first alarms, so that a second alarm can be determined; thus, failure positioning is completed; all the alarms are unnecessary to process; alarm data in need of being reported and analyzed is greatly reduced; and thus, the failure analysis efficiency is improved.

Owner:CHINA TELECOM CORP LTD

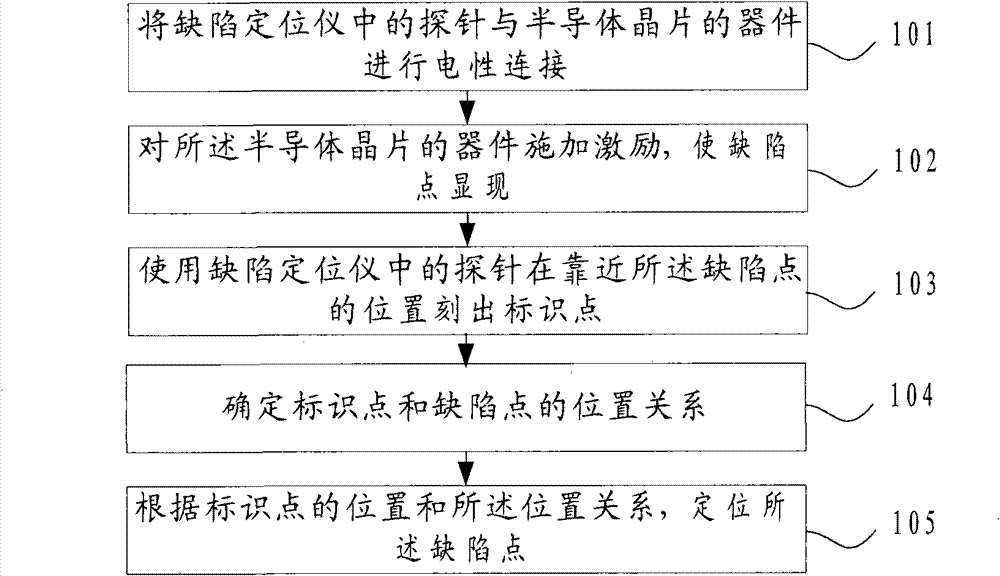

Defect point locating method of semiconductor device

ActiveCN102385028BLow costImprove the efficiency of failure analysisIndividual semiconductor device testingSemiconductor chipFailure analysis

The invention discloses a defect point locating method of a semiconductor device, which comprises the following steps: a probe in a defect locator is electrically connected with a device of a semiconductor chip; the device of the semiconductor chip is excited so as to enable a defect point to appear; the probe of the defect locator is used to carve an identification point in a position close to the defect point; and the position relationship between the identification point and the defect point is confirmed. According to the method provided by the invention, when the defect point in the device of the semiconductor chip appears due to excitation, the probe of the existing defect locator is used to set the identification point nearby the defect point, so the defect point can be located according to the position of the identification point and the position relationship between the identification point and the defect point. The method has the advantages that an expensive laser marking machine does not need to be adopted, the cost of failure analysis can be reduced, the existing equipment does not need to be refitted at the same time, the failure analysis can be realized conveniently and rapidly, the simplicity and the practicality are achieved, and the efficiency of the failure analysis is improved.

Owner:CSMC TECH FAB2 CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com