Wafer-level packaging method for a semiconductor device

A wafer-level packaging and semiconductor technology, used in semiconductor devices, electrical components, circuits, etc., can solve the problem of large differences in mechanical properties between phosphor layers and substrates, cracking and breaking of photodiode packaging products, and limiting the space for packaging light sources, etc. problem, to achieve the effect of easy holding, easy processing, and reducing thermal stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

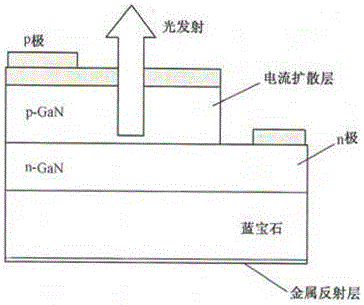

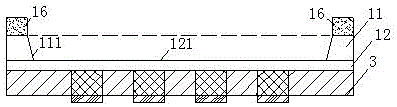

[0050] see figure 2 , the technological process of the wafer-level packaging method of a semiconductor device of the present invention is as follows:

[0051] S101: Take a silicon wafer, on which an epitaxial layer is grown on the silicon substrate;

[0052] S102: forming an array of metal bumps on the surface of the epitaxial layer, encapsulating them, and thinning them to expose the surface of the other end of the metal bumps;

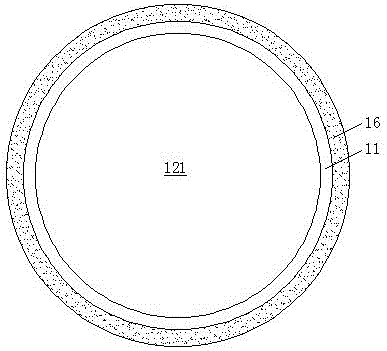

[0053] S103: Thinning the silicon substrate, removing the middle region of the silicon substrate to expose the light-emitting surface of the epitaxial layer;

[0054] S104: Divide the epitaxial layer, and sequentially form a phosphor layer and a light-transmitting layer on the epitaxial layer;

[0055] S105: cutting the silicon wafer that has completed the packaging process into packages of individual semiconductor devices.

[0056] The present invention will now be described more fully hereinafter with reference to the accompanying drawings, in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More