Manufacturing method for low-temperature polycrystalline silicon and manufacturing method for TFT substrate

A technology of low-temperature polysilicon and its production method, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc. It can solve the problems of polysilicon layer with many metal residues, expensive ELA equipment, and low density of polysilicon gap states, so as to reduce crystallization Process temperature, shorten crystallization process time, and improve crystallization effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

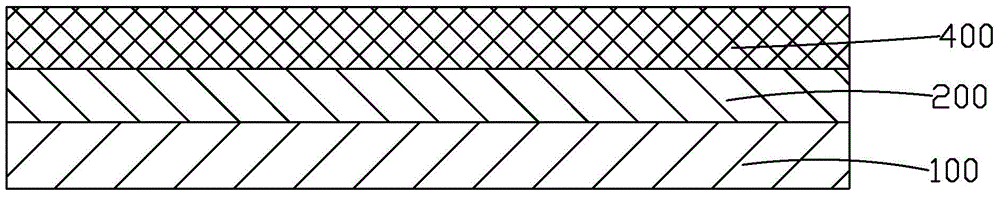

[0053] see Figure 6 and Figure 8 to Figure 13 , the invention provides a method for manufacturing low-temperature polysilicon, comprising the steps of:

[0054] Step 1, providing a substrate 1 .

[0055] The substrate 1 is a common transparent substrate, preferably, the substrate 1 is a glass substrate.

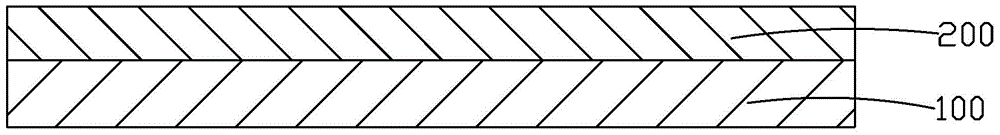

[0056] Step 2, such as Figure 8 As shown, a buffer layer 2 is deposited on a substrate 1 .

[0057] Specifically, the buffer layer 2 may be a single layer of SiNx, a single layer of SiOx, a double layer of SiNx, a double layer of SiOx, or a combination of both SiNx and SiOx layers.

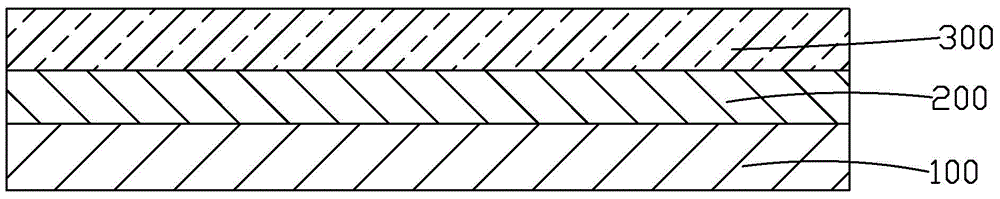

[0058] Step 3, if Figure 9 As shown, a metal mesh film 3 is coated on the buffer layer 2.

[0059] Specifically, the metal mesh 3 is made of aluminum. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More