Suppression method for zero-sequence voltage caused by dual inverter switching dead area

A zero-sequence voltage, dual-inverter technology, which is applied in motor generator control, AC motor control, electronic commutation motor control, etc., can solve the problems of zero-sequence voltage in the system and affect system performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

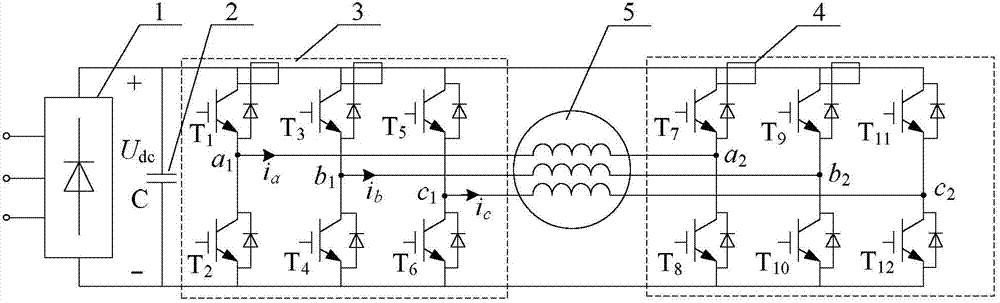

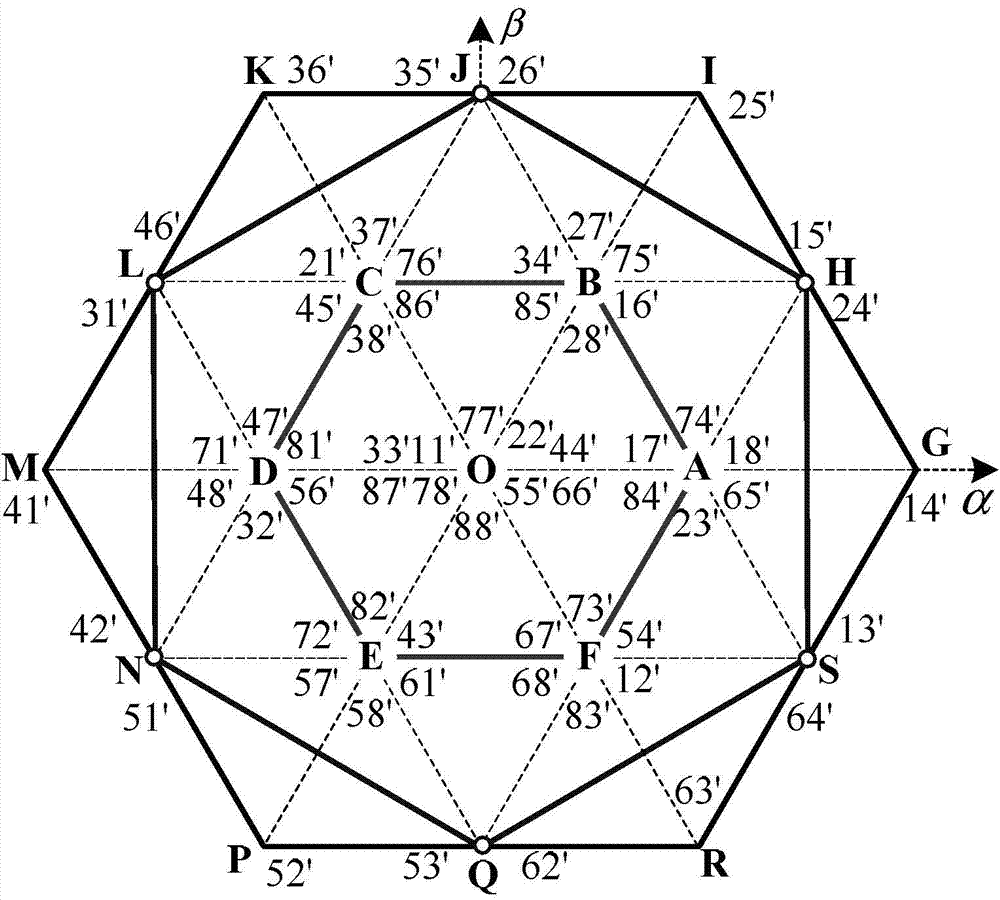

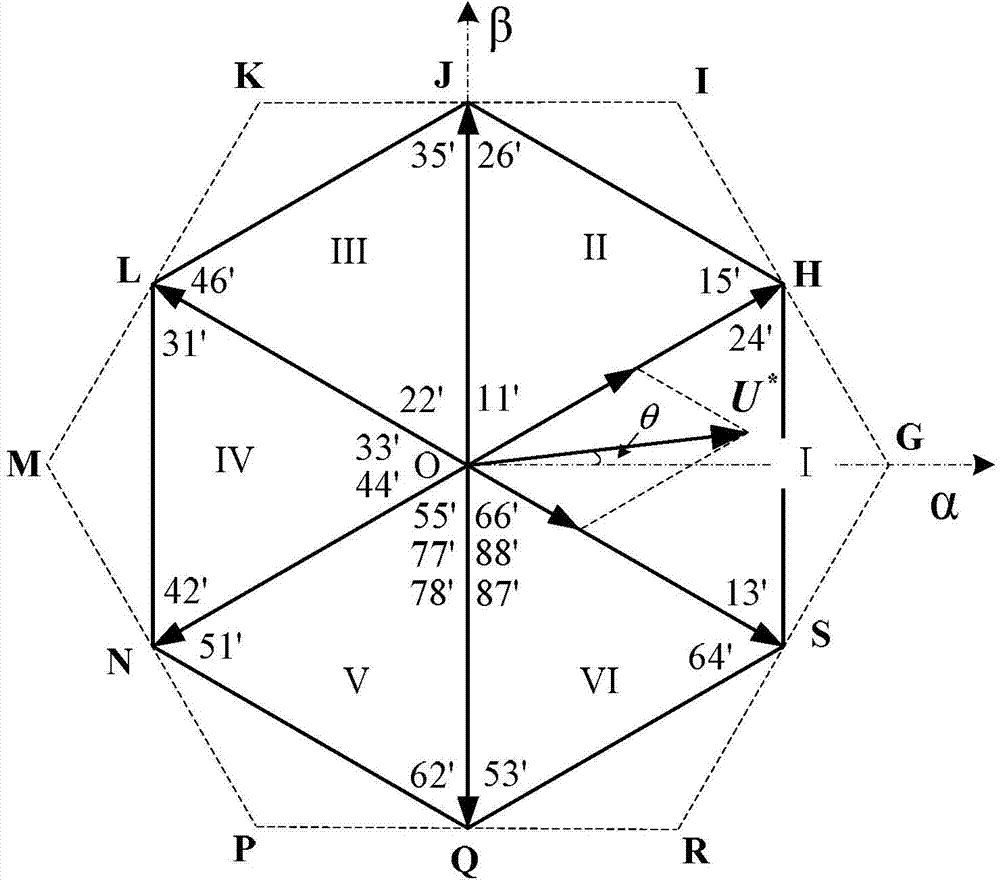

[0060] Specific implementation mode one: the following combination Figure 1 to Figure 15 Describe this embodiment, the suppression method of the zero-sequence voltage caused by the dead zone of the double inverter switch described in this embodiment, the suppression method is based on the SVPWM modulation using a combination of switches that do not generate zero-sequence voltage, the suppression method first The three-phase voltage signal of the double inverter is collected by the voltage sensor, and the three-phase voltage signal is the three-phase voltage signal after RC low-pass filtering; then the three-phase voltage signal is processed to obtain the system zero-sequence voltage; then according to The zero-sequence voltage of the system is calculated in the dead zone to obtain the compensation voltage vector, so that the zero-sequence voltage generated by the compensation voltage vector offsets the zero-sequence voltage of the system to realize the suppression of the zero-...

specific Embodiment approach 2

[0062] Specific Embodiment 2: This embodiment will further explain Embodiment 1. The method for obtaining the zero-sequence voltage of the system is: the three-phase voltage signals of the dual inverters collected by the voltage sensor are summed and calculated through an operational amplifier circuit, The calculated result is converted into a digital system zero-sequence voltage through an analog-to-digital converter.

[0063] The conversion of the summation result in this embodiment can be realized by the A / D of the DSP, and the analog quantity is converted into a digital quantity.

specific Embodiment approach 3

[0064] Specific implementation mode three: this implementation mode further explains implementation mode two, and the method for obtaining the compensation voltage vector is:

[0065] First, reverse the polarity of the zero-sequence voltage of the system to obtain the polarity of the zero-sequence voltage generated by the compensation voltage vector;

[0066] Then according to the polarity of the zero-sequence voltage generated by the compensation voltage vector and the sector where the reference voltage vector U* is located, determine the switch combination of the compensation voltage vector;

[0067] Then by increasing the conduction time of one of the two switch signals with the maximum duty cycle, the conduction time of the switch signal is increased to 2 times the dead zone time, thereby obtaining an action time of 2 times the dead zone Time-compensated voltage vector.

[0068] The zero-sequence voltage generated by the compensation voltage vector obtained in this embodi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More