Digital FNPLL (Fractional-N Phase-Locked Loop) control method and PLL (Phase-Locked Loop)

A technology of fractional frequency division and phase-locked loop, applied in the field of electronics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

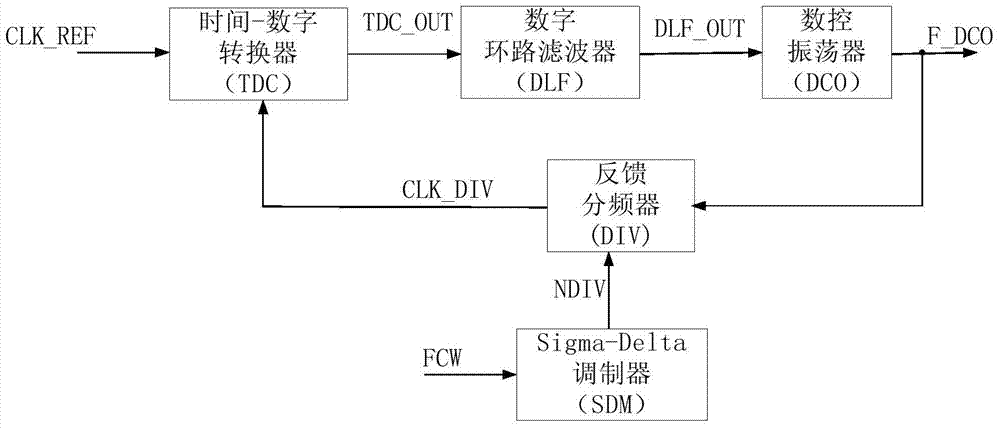

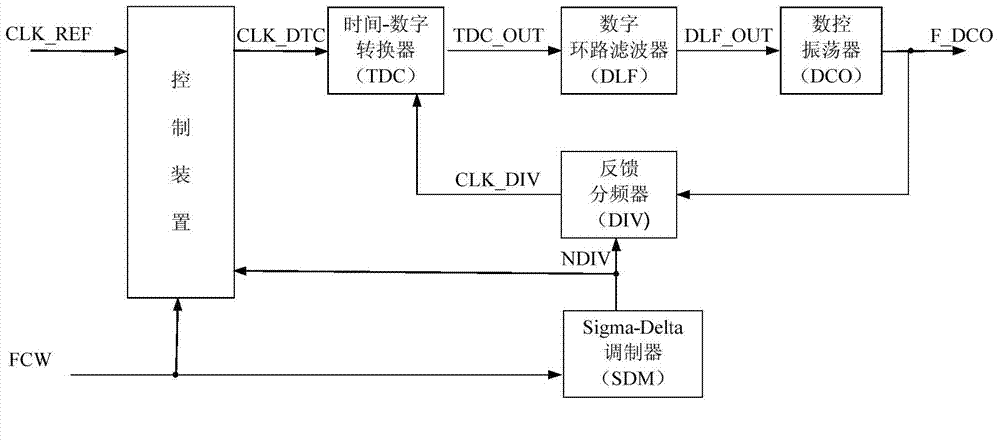

[0086] image 3 A schematic structural diagram of a digital fractional frequency-division phase-locked loop provided in Embodiment 1 of the present invention, as shown in image 3 As shown, the phase-locked loop includes a control device and a time-to-digital converter TDC, a digital loop filter DLF, a digitally controlled oscillator DCO, a feedback frequency divider DIV and a Sigma-Delta modulator SDM.

[0087] Wherein, the output end of the control device is connected to the first input end of the TDC; the output end of the TDC is connected to the input end of the DLF, the output end of the DLF is connected to the input end of the DCO, and the output end of the DCO is connected to the first input end of the DIV ; The output end of DIV is connected with the second input end of TDC; The second input end of DIV is connected with the output end of SDM, the first input end of the control device is connected with the output end of SDM, the second input end of the control device is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More