Film transistor and manufacturing method thereof

A technology of thin film transistors and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of inability to meet the on-state current requirements of AMOLED, increase the complexity of the manufacturing process, and low carrier concentration, and achieve Reduce the number of process photomasks, save the number of ion implantations, and have good process compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

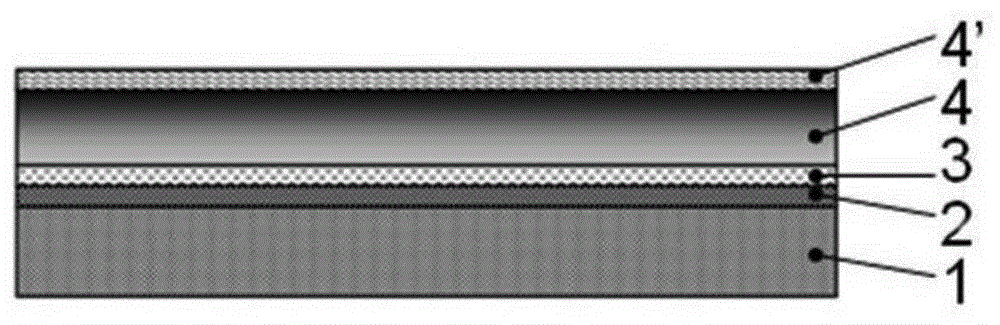

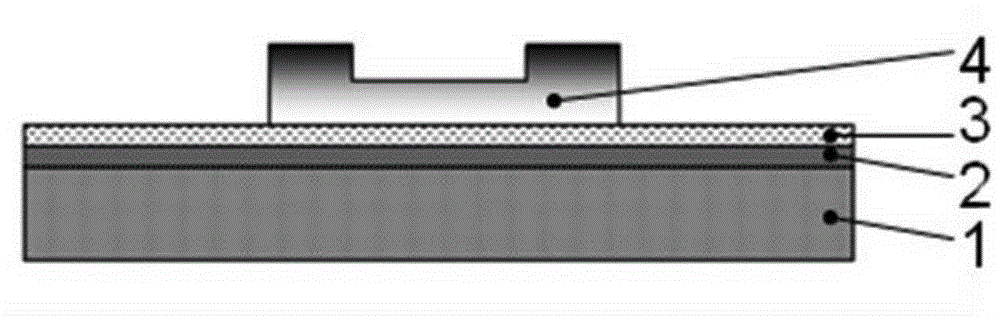

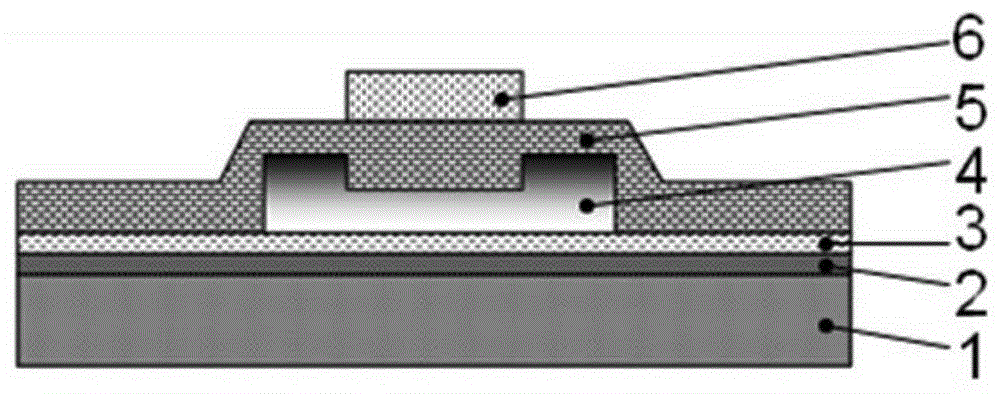

[0030] Figure 1A to Figure 1E It is a schematic diagram of the manufacturing process of the thin film transistor according to the first embodiment of the present invention.

[0031] refer to Figure 1A As shown, buffer layers 2 and 3 are sequentially deposited on a substrate 1 . The material of the substrate 1 can be glass, quartz, organic polymer, or opaque / reflective material. The buffer layers 2 and 3 can be formed by a low-pressure chemical vapor deposition process or an ion-increased chemical vapor deposition process. The buffer layer can prevent impurities contained in the substrate from entering the polysilicon layer 41 . In a specific embodiment, the buffer layer may be a single layer of silicon oxide or a double layer structure of silicon oxide / silicon nitride. Then deposit an amorphous silicon layer on the buffer layers 2 and 3, and crystallize the amorphous silicon layer. The crystallization method can be selected from any one of excimer laser crystallization, so...

no. 2 example

[0039] Figure 2A to Figure 2E It is a schematic diagram of the manufacturing process of the thin film transistor according to the second embodiment of the present invention.

[0040] refer to Figure 2AAs shown, buffer layers 2 and 3 are sequentially deposited on a substrate 1 . Then a first amorphous silicon layer is deposited on the buffer layers 2 and 3, and the first amorphous silicon layer is crystallized. The first amorphous silicon layer is transformed into a polysilicon layer 41 after crystallization. The difference between the second embodiment and the first embodiment is that the second amorphous silicon layer 42 is deposited before the barrier layer 4' is deposited on the polysilicon layer 41. Preferably, the thickness of the second amorphous silicon layer 42 is 1-5000 ?, the thickness of the polysilicon layer is 1~5000 ?. Because in the crystallization process, if the polysilicon layer 41 is too thick, it is not conducive to generating polysilicon with good un...

no. 3 example

[0043] Figure 3A to Figure 3E It is a schematic diagram of the manufacturing process of the thin film transistor according to the third embodiment of the present invention.

[0044] The difference between this embodiment and the previous two embodiments lies in the method of forming the polysilicon layer whose dopant ion concentration is distributed in a gradient from high to low from the upper surface to the lower surface. refer to Figure 3A As shown, buffer layers 2 and 3 are sequentially deposited on substrate 1 . Then, an ion-enhanced chemical vapor deposition process (Plasma Enhanced Chemical Vapor Deposition, PECVD) is used to deposit an amorphous silicon layer on the buffer layer. While depositing the amorphous silicon layer 4, a dopant gas is introduced. For the p-type channel B-containing gas can be introduced, and P or As-containing gas can be introduced for N-type doping, and the concentration of doping gas is controlled to gradually increase, and finally the co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com