Variable doped junction terminal preparation method

A technology of junction termination and variable doping, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of increasing the number of ion implantations, achieve the effect of reducing the number of times and avoiding film thickness changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The technical solution of the present invention will be further elaborated below in conjunction with the accompanying drawings.

[0039] The invention discloses a method for preparing a variable doping junction terminal, comprising the following steps:

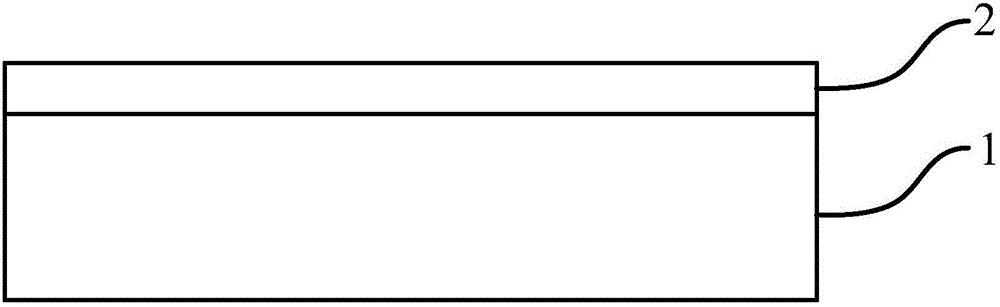

[0040] S1: grow the first dielectric layer 2 on the silicon carbide epitaxial layer 1, such as figure 1 shown;

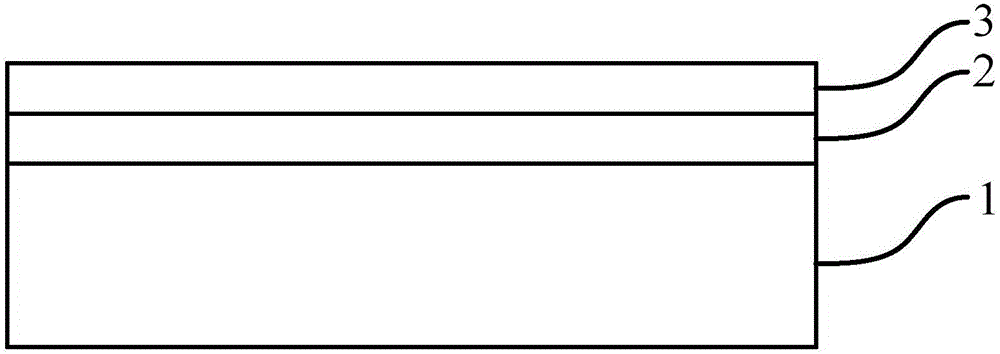

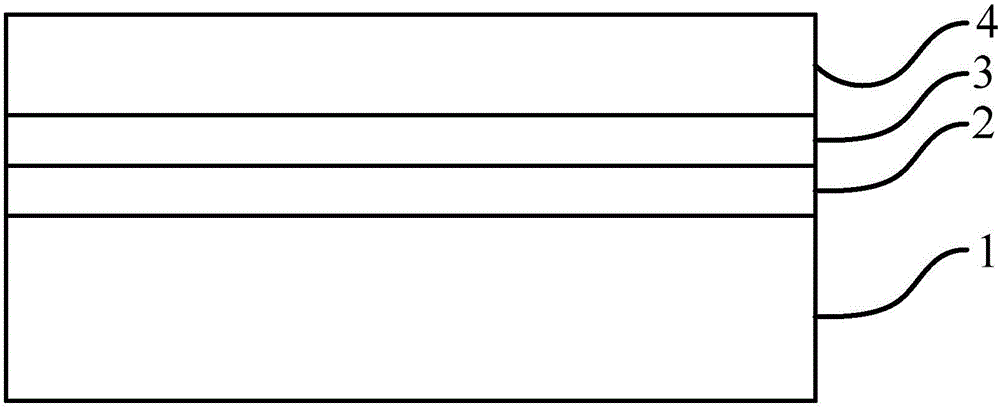

[0041] S2: growing the second dielectric layer 3 on the first dielectric layer 2, such as figure 2 As shown; the first etch barrier layer 4 is processed on the surface of the second dielectric layer 3, such as image 3 shown, and remove part of the first etch barrier layer 4 by etching, such as Figure 4 As shown, the unremoved first etch barrier layer 4 is still covering the second dielectric layer 3, and then the area not covered by the first etch barrier layer 4 in the second dielectric layer 3 is removed by etching, as Figure 5 As shown, the area covered by the first etch barrier layer 4 in the seco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More