Time delay-based double-track pre-charge logic NAND gate circuit and Time delay-based double-track pre-charge logic exclusive or gate circuit

A technology of NOT gate circuit and logical difference, applied in the direction of logic circuit with logic function, etc., can solve the problem of unbalanced circuit power consumption, and achieve the effect of solving the problem of charge sharing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

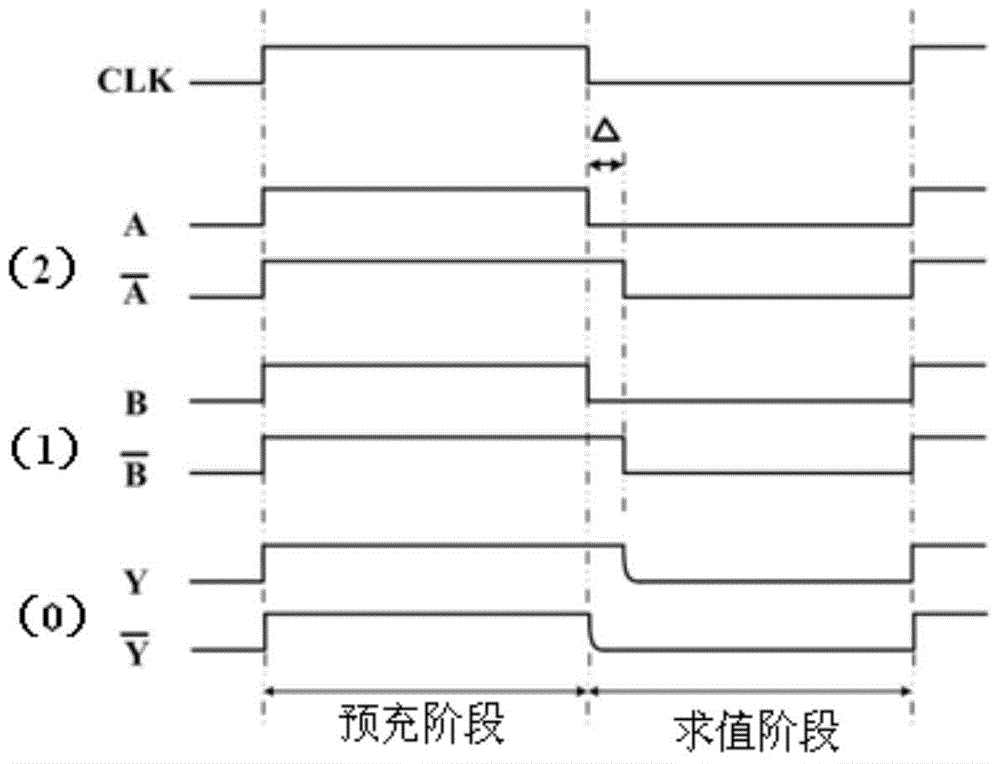

[0050] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but should not be used to limit the scope of the present invention.

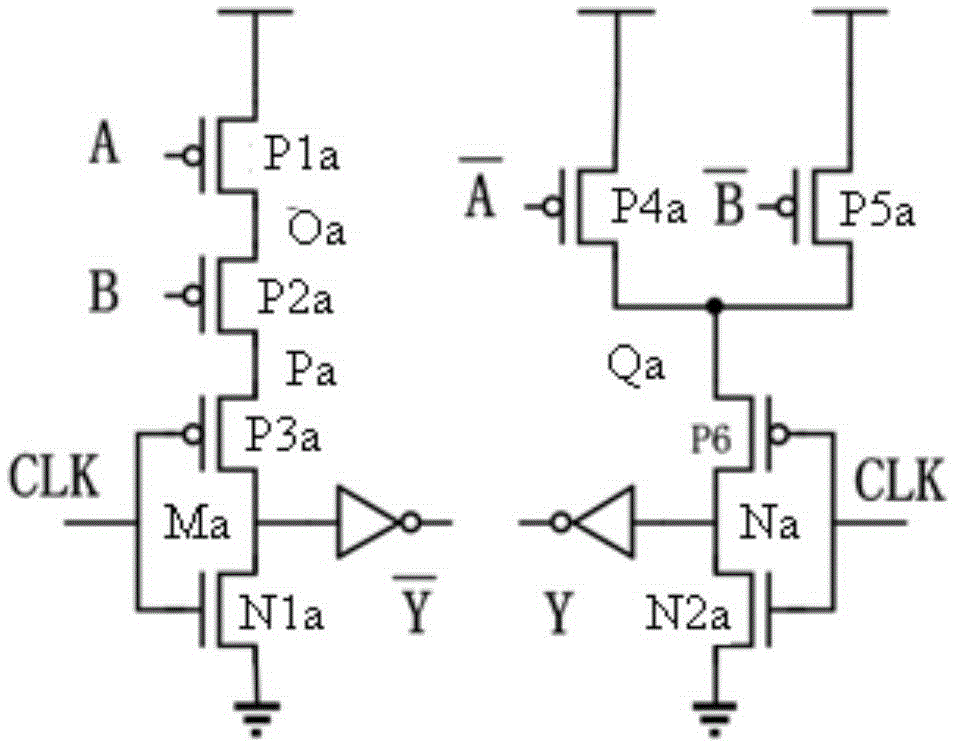

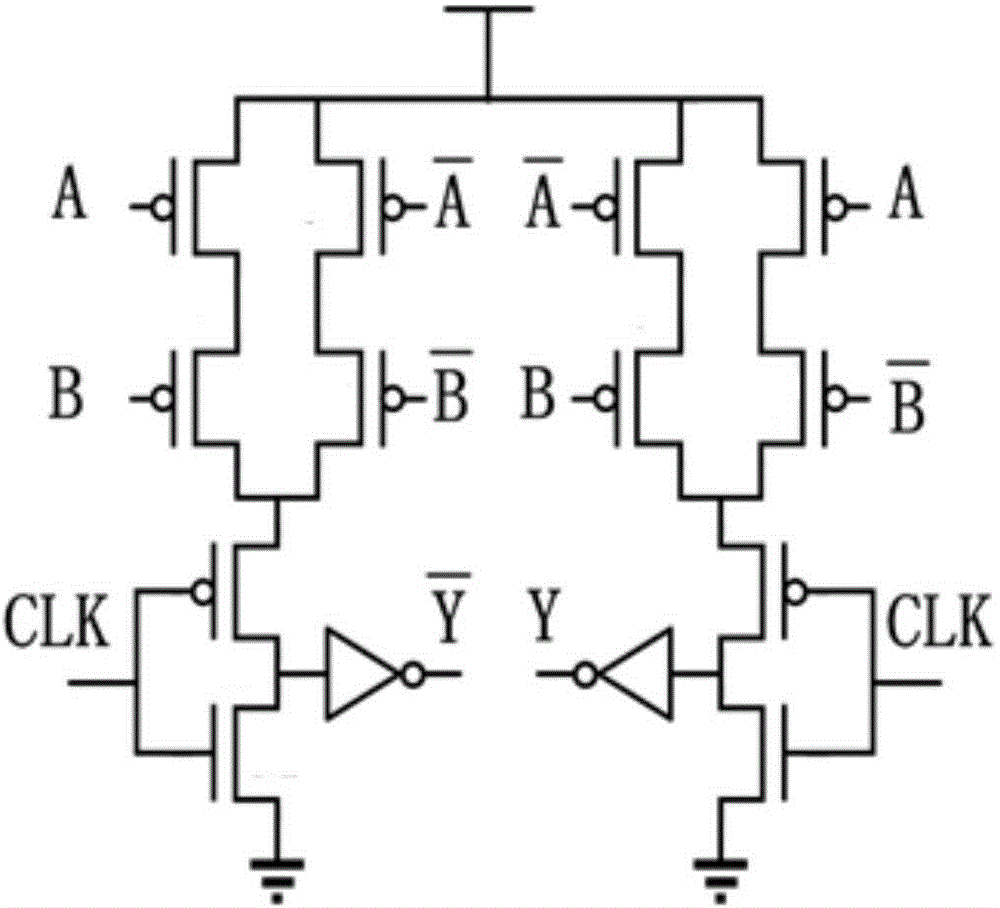

[0051] The present invention provides a delay-based dual-rail precharge logic NAND gate circuit, which is characterized in that it includes PMOS transistors P1, P2, P3, P4, P5, P6, NMOS transistors N1, N2, N3, the first inverting device F1; the second inverter F2, such as figure 2 shown.

[0052] The source of the PMOS transistor P1 is connected to the power supply, the gate is connected to the clock signal, and the drain is connected to the source of the PMOS transistor P2; the drain of the PMOS transistor P2 is connected to the source of the PMOS transistor P3, so The drain of the PMOS transistor P3 is connected to the drain of the NMOS transistor N1 and the input terminal of the first inverter F1; the g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More