Semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve problems such as peeling off of multi-layer pseudo-plug layers and multi-layer pseudo-metal layers, reduction of insulation isolation performance of interlayer dielectric layers, instability of oscillation circuits, etc., to achieve The texture is dense, the insulation performance is good, and the effect of ensuring the insulation performance is ensured

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

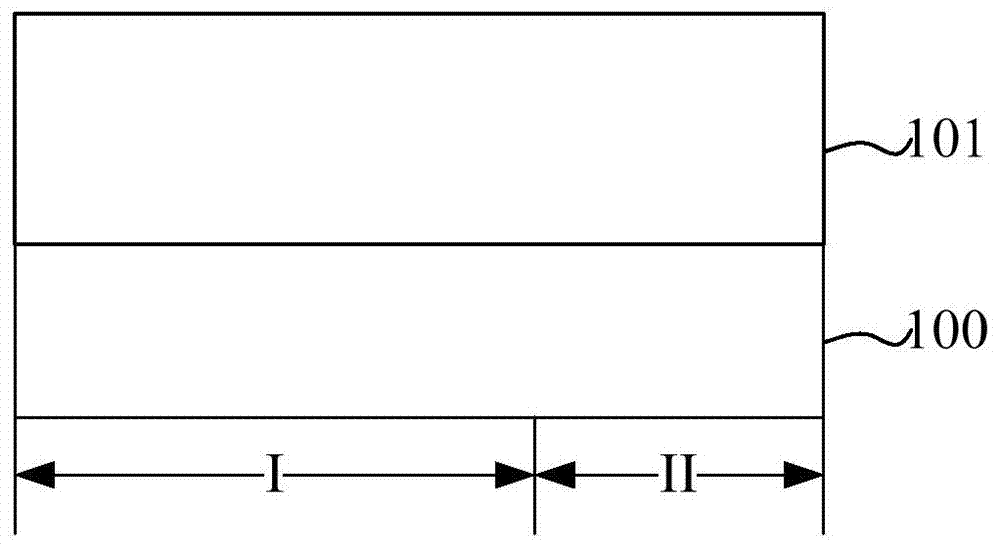

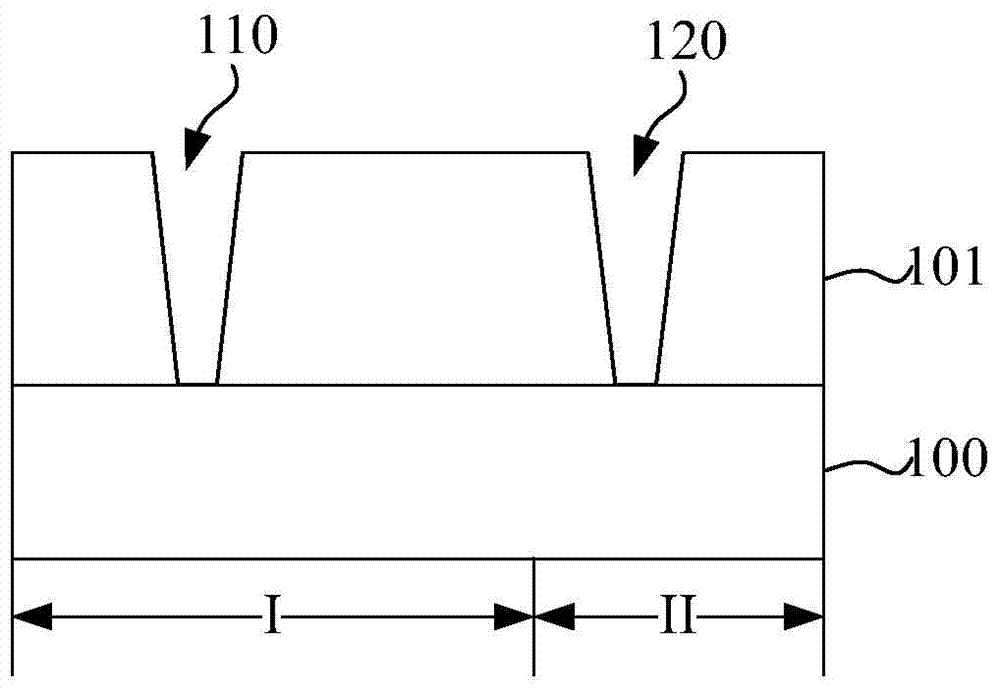

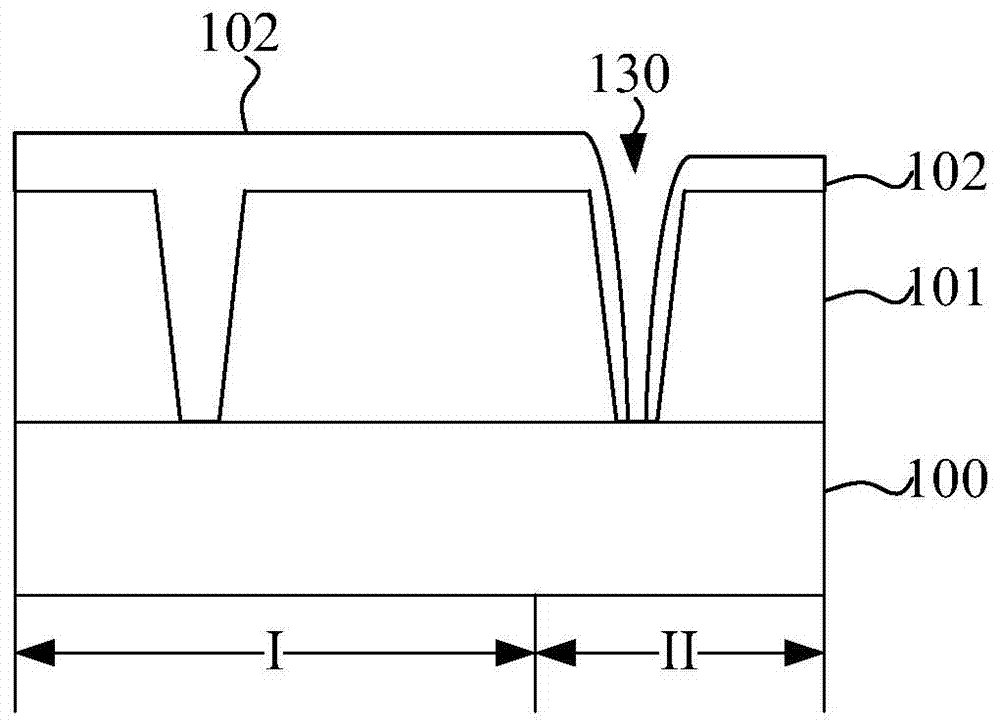

[0047] Aiming at the problems existing in the prior art, the inventor conducted an analysis and found that: after the device structure is formed in the wafer, the first contact hole corresponding to the device region and the first contact hole on the edge of the wafer are formed in the first dielectric layer on the wafer. The second contact hole, followed by chemical vapor deposition of tungsten metal, tungsten will fill in the first contact hole and the second contact hole, and cover the first dielectric layer.

[0048] On the one hand, during the process of depositing tungsten, the wafer will be placed on the base, and the edge of the wafer will be covered by the shielding part on the base but the shielding part will not be in contact with the wafer. Tungsten diffuses in the reaction chamber in gaseous phase, but the second contact hole is covered, and tungsten enters the second contact hole through the gap between the shielding part and the second contact hole, so that the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com