Anti-radiation multibit-flip partitioned-matrix-code strengthening method for storers

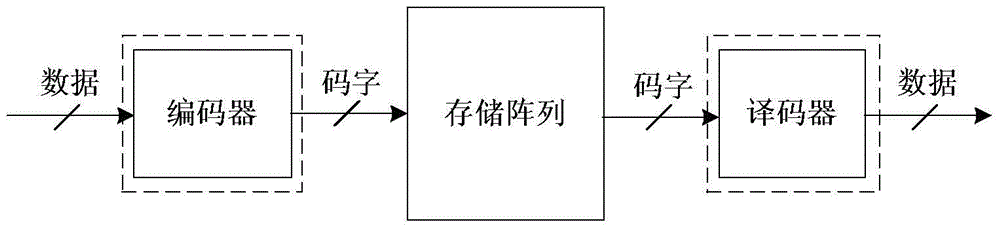

A technology of multi-bit flipping and block matrix, which is applied to the application of error detection coding of multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc., which can solve the problem of high hardware performance overhead , high cost, poor reliability and other issues, to achieve the effect of small area and power consumption overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

[0018] Specific implementation mode 1. Combination figure 2 Describe this specific implementation mode, the storage anti-multi-bit flip blocking matrix code reinforcement method described in this specific implementation mode is realized through the following steps:

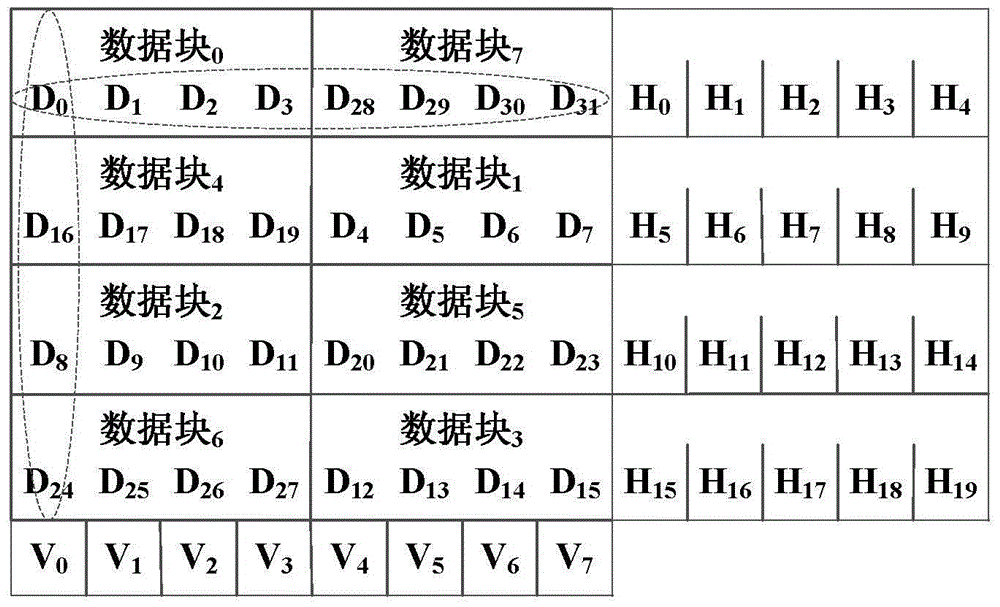

[0019] Step 1. Divide a k-bit wide word data D into multiple m-bit wide data blocks, and number these data blocks and arrange them into k 1 ×k 2 The data matrix of k=k 1 ×k 2 ×m, and adjacent k 2 data blocks are not in the same row, not in the same column;

[0020] Step two, for k 1 ×k 2 For each row of the data matrix, the decimal addition calculation is performed in units of data blocks to obtain the horizontal redundancy bit H; for k 1 ×k 2 For each column of the data matrix, perform binary XOR calculation in units of data blocks to obtain vertical redundant bits V, and obtain codewords C={D, H, V} through the encoder;

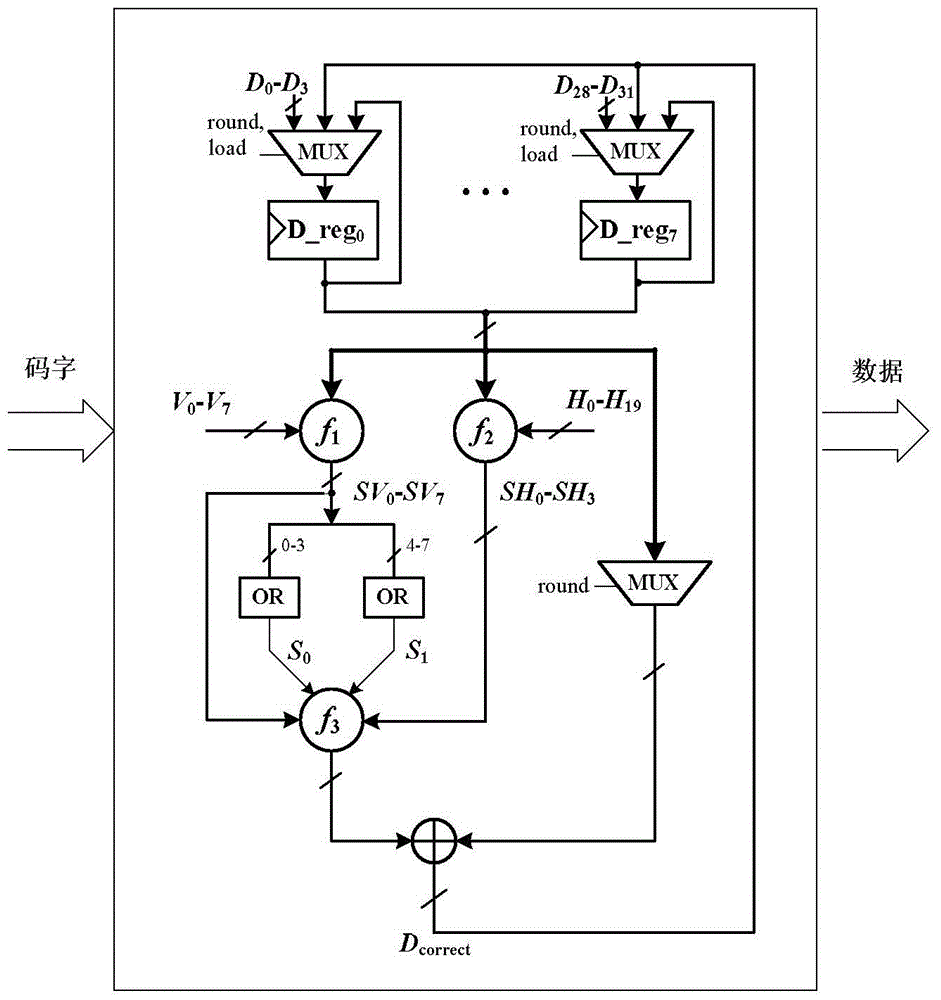

[0021] Step 3, the decoder reads the code word C, and recalculates the data matri...

specific Embodiment approach 2

[0028] Embodiment 2. The difference between this embodiment and the memory anti-multi-bit flip block matrix code reinforcement method described in Embodiment 1 is that in the step 6, it is judged that the continuous k 2 The consistency process of the horizontal data block syndrome SH, the vertical data bit syndrome SV and the vertical data block syndrome S of a data block is:

[0029] When the horizontal data block syndrome SH, the vertical data bit syndrome SV and the vertical data block syndrome S of the data block are 1 at the same time, the correctness signal of the output data block is 1, otherwise, the correctness signal of the output data block is 0.

[0030] Below, combine figure 2 Taking 32-bit bytes as an example to specifically illustrate the method proposed by the present invention:

[0031] Encoding part:

[0032] A 32-bit wide word data D 0 -D 31 Divide into 8 4-bit wide data blocks in order, and arrange these data blocks into a 4×2 matrix form, such as f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More