Semiconductor device

A semiconductor and conductor layer technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of increased cost, difficulty in adopting, and larger wiring and winding.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

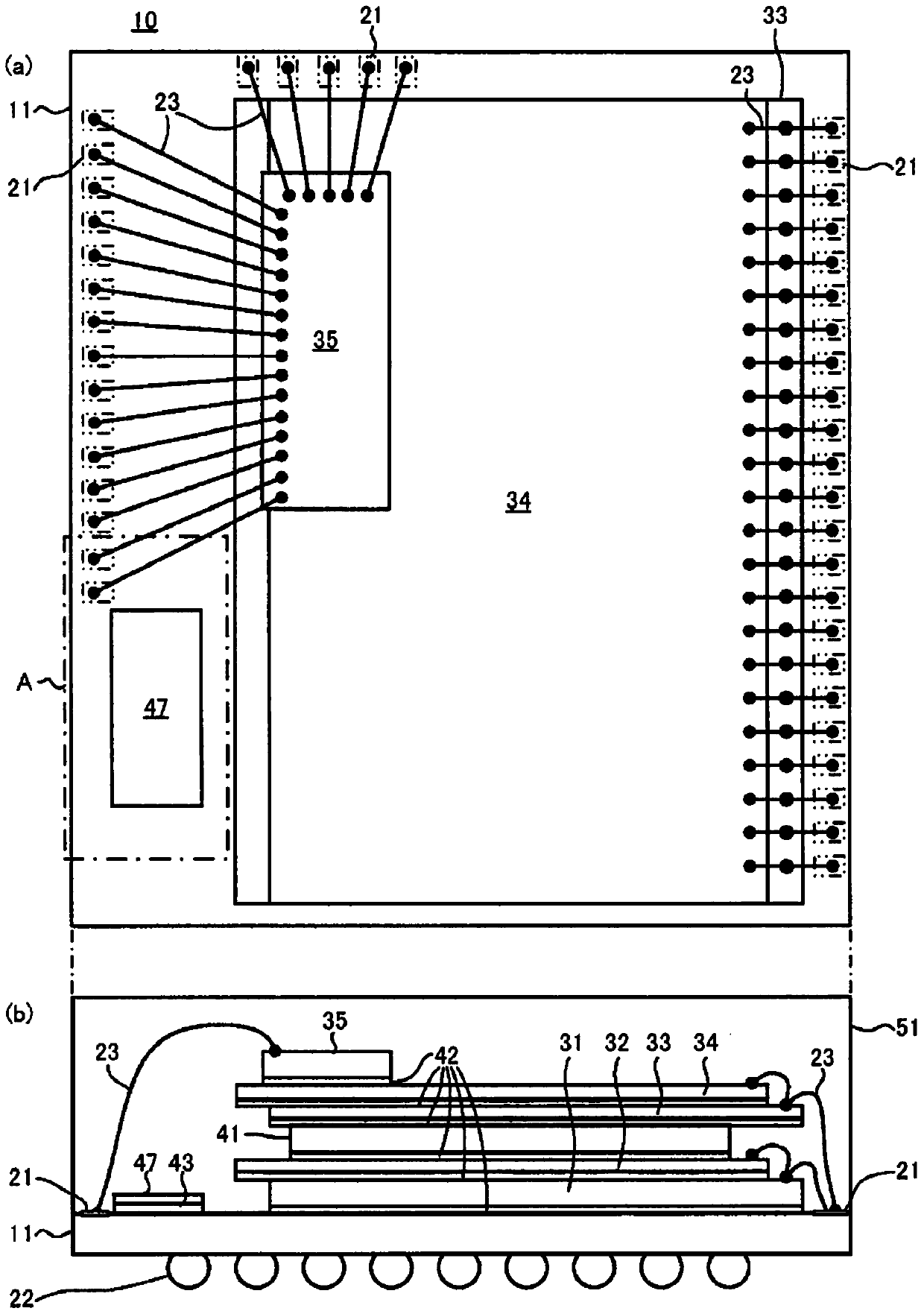

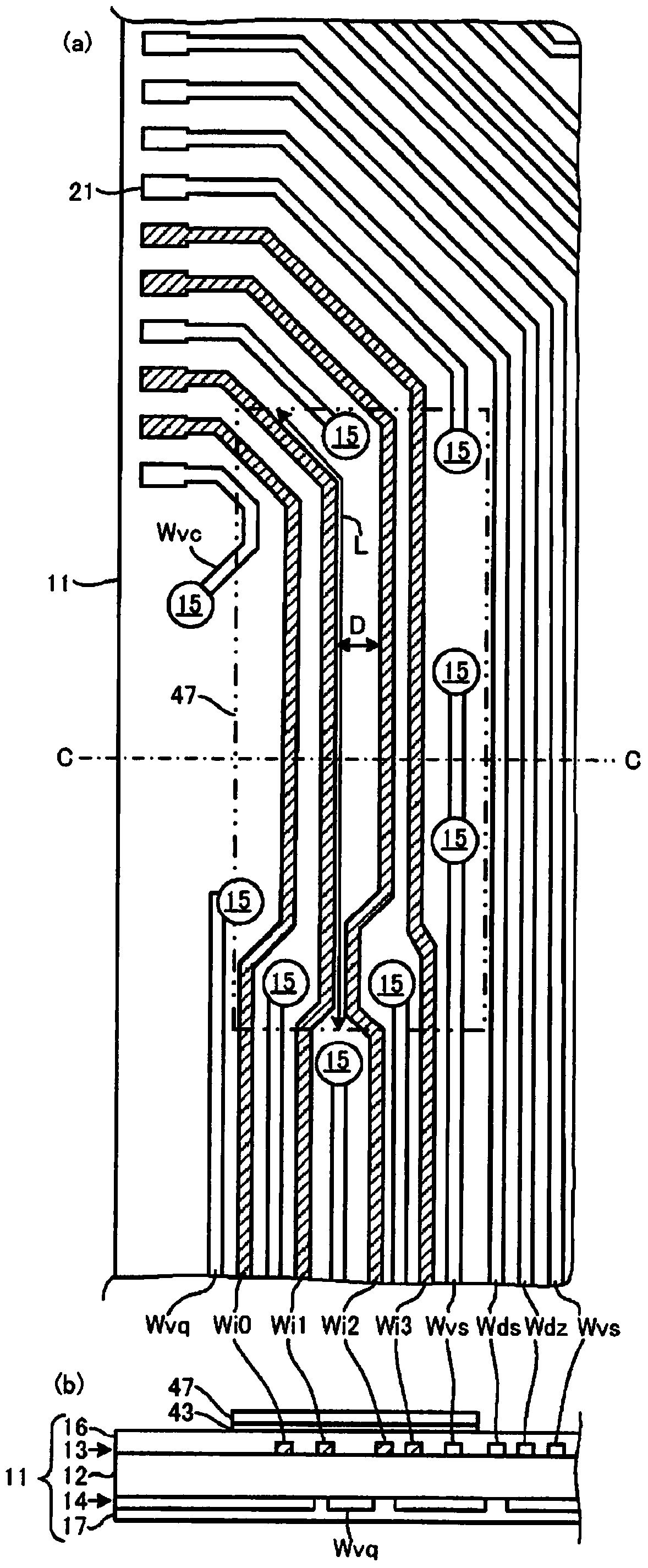

[0030] figure 1 (a) and (b) are respectively a plan view and a cross-sectional view of the semiconductor device 10 according to the first embodiment. figure 2 (a) and (b) are respectively figure 1 The enlarged top view and cross-sectional view of area A. figure 2 (b) means along figure 2 Section of line C-C of (a).

[0031] Furthermore, for ease of understanding, the figure 1 The description of wiring W is omitted in the figure 2 The description of the connection member 23 is omitted here. Moreover, hatching is attached|subjected to wiring Wi0-Wi3.

[0032] Such as figure 1 , figure 2 As shown, the semiconductor device 10 has a substrate 11 (core layer 12, wiring layers 13, 14, via holes 15, resist layers 16, 17), connection terminals 21, external terminals 22, connection members 23, memory chips 31-34 , a controller chip 35 , a spacer 41 , adhesive layers 42 , 43 , a conductor layer 47 , and a molding resin layer 51 .

[0033] The semiconductor device 10 is a s...

no. 2 Embodiment approach

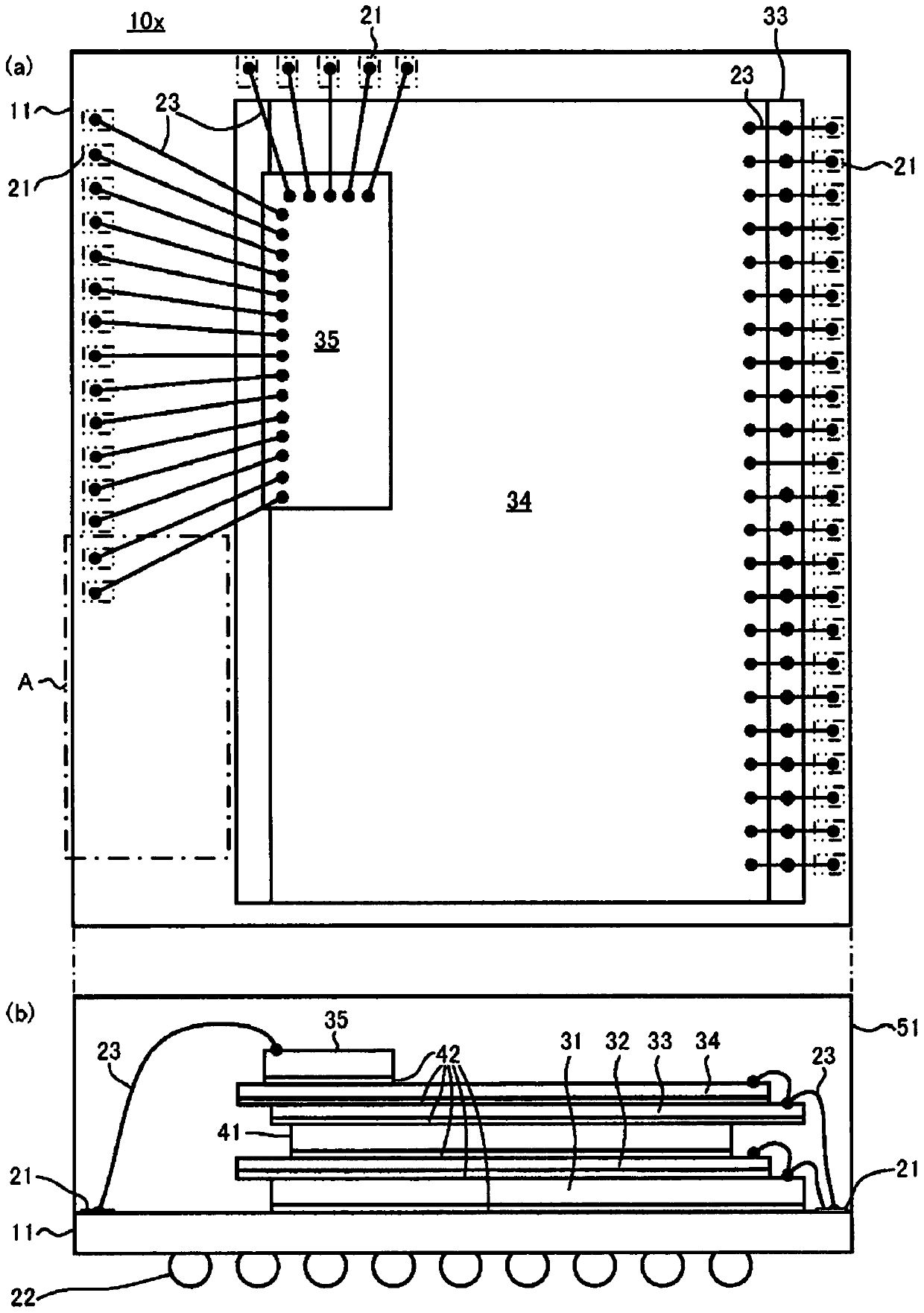

[0084] Figure 5 (a) and (b) are respectively a plan view and a cross-sectional view of a semiconductor device 10a according to the second embodiment. Figure 6 (a) and (b) are respectively Figure 5 The enlarged top view and cross-sectional view of area A. Figure 6 (b) means along Figure 6 Section of line C-C of (a).

[0085] In this embodiment, the dummy chip 61 is arranged on the wiring layer 13 .

[0086] The dummy chip 61 has a silicon substrate 62 and a conductor layer 47 . In the present embodiment, the dummy chip 61 is mounted so that the conductor layer 47 faces the surface of the substrate 11 facing downward. The silicon substrate 62 in this embodiment functions as a semiconductor substrate arranged on the conductive layer 47 .

[0087] The conductor layer 47 has conductivity and paramagnetism, and the same material and thickness as the conductor layer 47 can be selected.

[0088] Also in this embodiment, as in the first embodiment, the conductive layer 47 r...

no. 3 Embodiment approach

[0090] Figure 7 (a) and (b) are respectively a plan view and a cross-sectional view of a semiconductor device 10b according to the third embodiment. Figure 8 (a) and (b) are respectively Figure 7 The enlarged top view and cross-sectional view of area A. Figure 8 (b) means along Figure 8 Section of line C-C of (a).

[0091] In the present embodiment, the dummy chip 61 is mounted face-up so that the conductive layer 47 side faces the opposite side of the substrate 11 . The silicon substrate 62 in this embodiment functions as a semiconductor substrate disposed between the conductive layer and the plurality of data signal lines.

[0092] Also in this embodiment, as in the first and second embodiments, the conductive layer 47 reduces the magnetic flux around the wirings Wi0 to Wi3, thereby reducing signal crosstalk.

[0093] As described above, in the above-described embodiment, by covering the region where the wirings Wi0 to Wi3 are adjacently arranged with the conductor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More