Super-junction semiconductor device and manufacture method thereof

A super-junction semiconductor and manufacturing method technology, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve the problems of surface MOS structure shrinkage, on-resistance increase, and large process difficulty, so as to reduce process difficulty and manufacture cost, alleviate the dv/dt is too large, increase the effect of the current flow path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The present invention will be further described below in conjunction with specific drawings and embodiments.

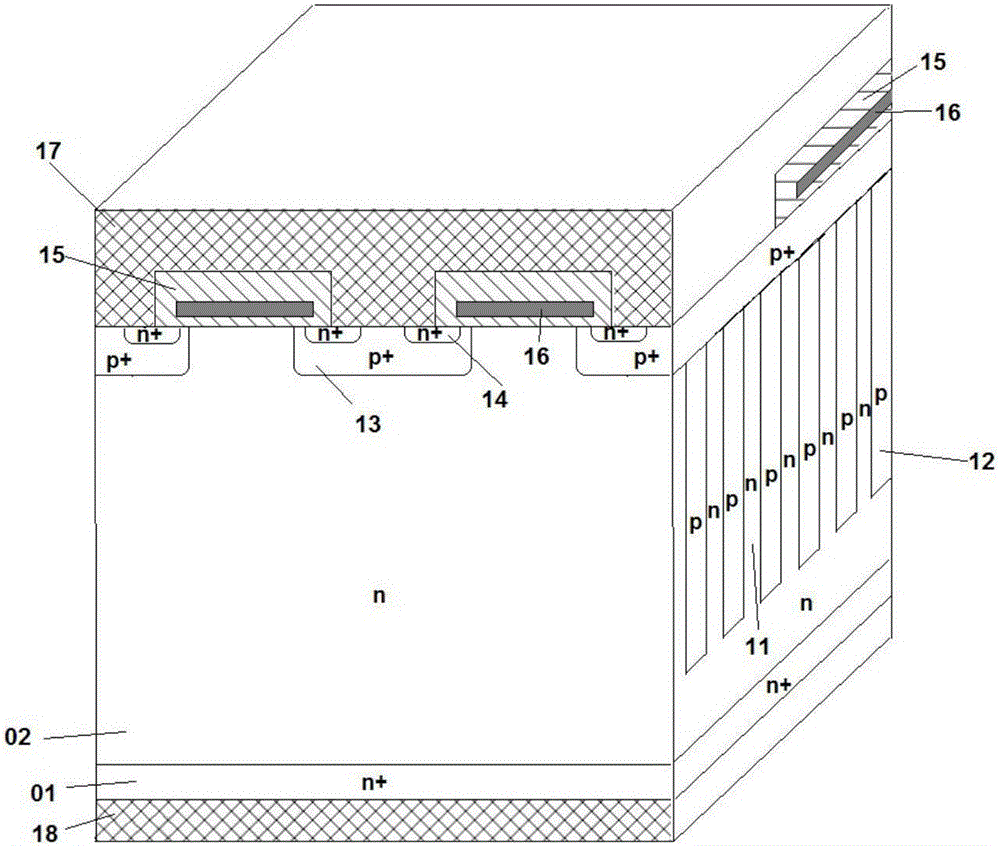

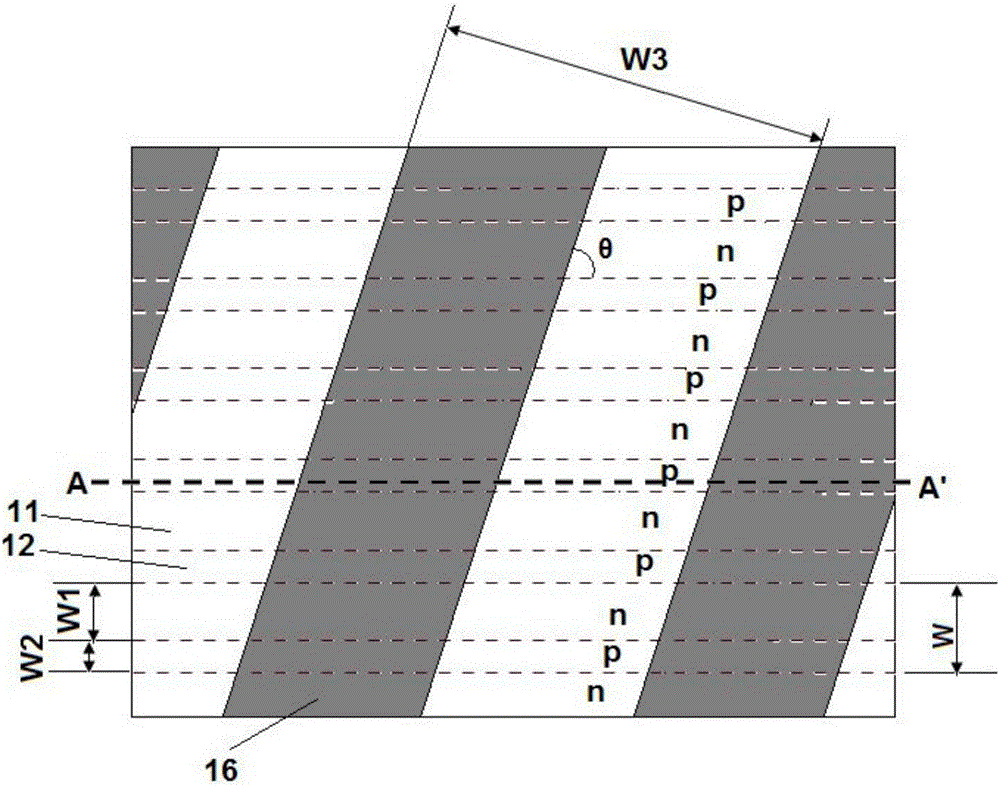

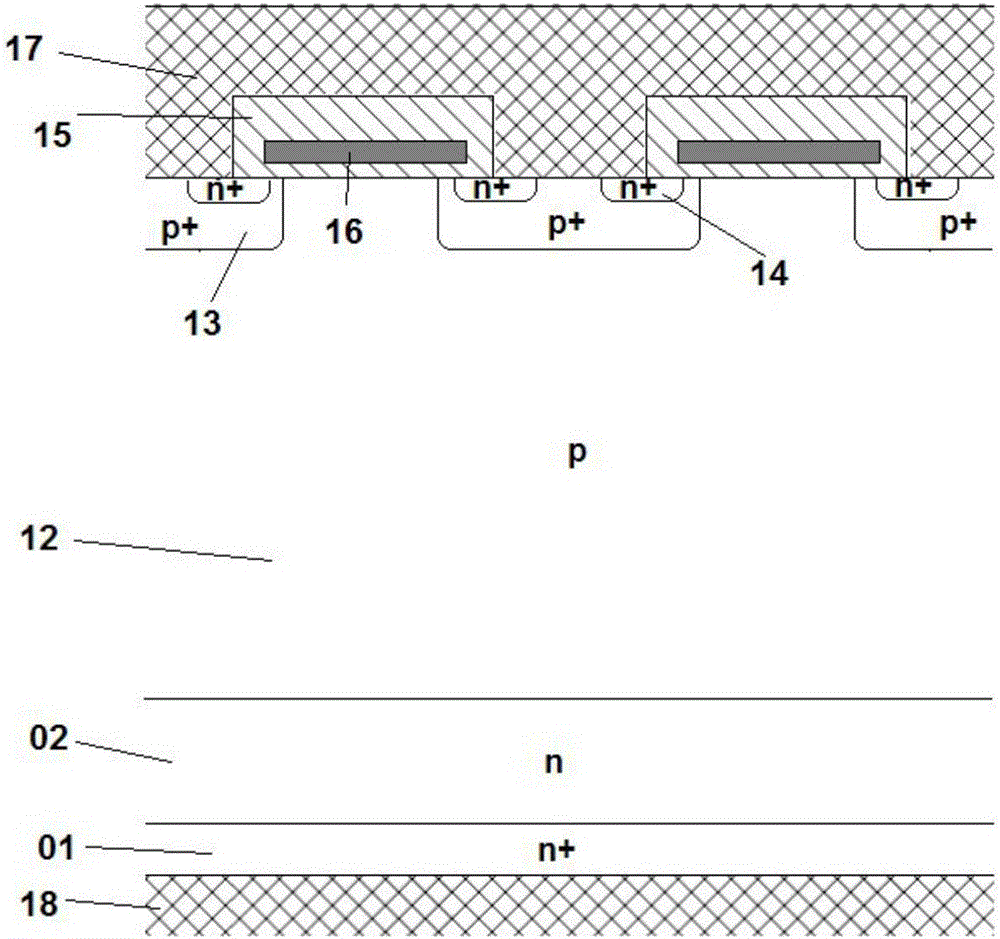

[0048] Such as figure 1 , figure 2 with image 3 As shown: taking an N-type planar superjunction vertical metal oxide field effect transistor as an example, the present invention includes a semiconductor substrate, and the semiconductor substrate includes an N-type substrate 01 and an N-type drift adjacent to the N-type substrate 01 Zone 02, the upper surface of the N-type drift zone 02 forms the first main surface of the semiconductor substrate, and the lower surface of the N-type substrate 01 forms the second main surface of the semiconductor substrate; A super junction structure formed by alternate arrangement of P columns 12, N columns 11 and P columns 12 in the super junction structure extend from the first main surface along the first main surface to the second main surface in the N-type drift region 02 Several device cells are set on the first main ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More