Silicon carbide trench gate power metal-oxide-semiconductor field effect transistors (MOSFETs) device and manufacturing method thereof

A silicon carbide trench and silicon carbide technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of unacceptable device threshold voltage and on-resistance, low effective electron mobility on the surface of the inversion layer, and electronic Effects of effective mobility and other issues, to achieve the effect of improving effective mobility, improving anti-latch-up ability, and avoiding high threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

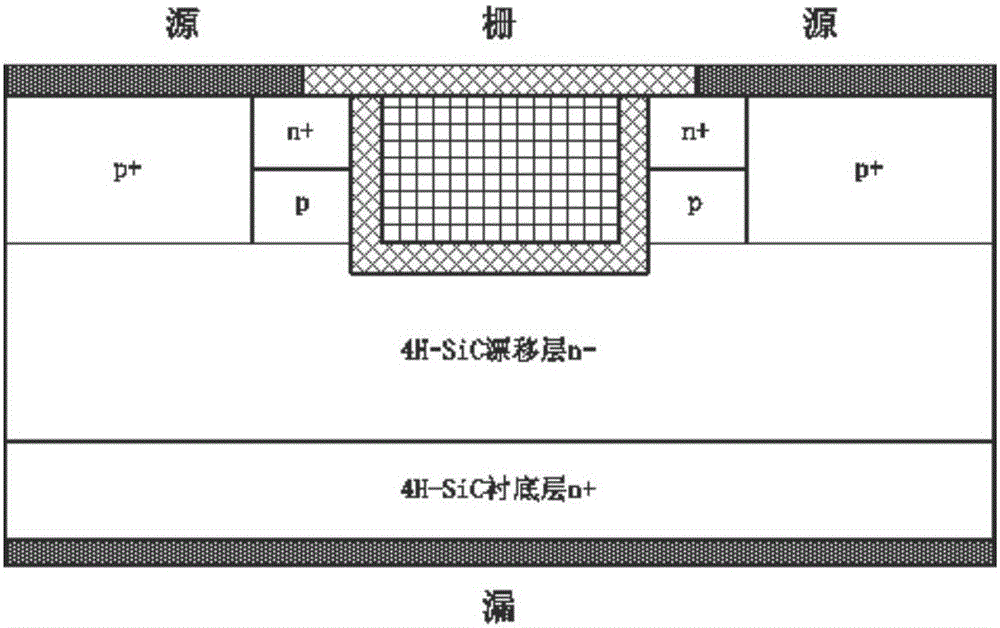

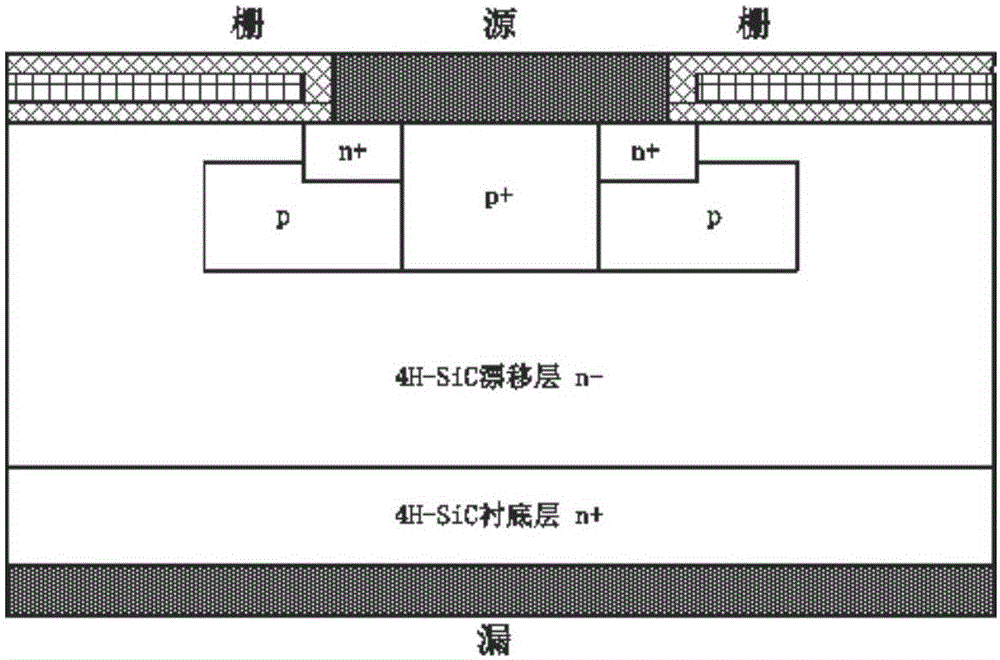

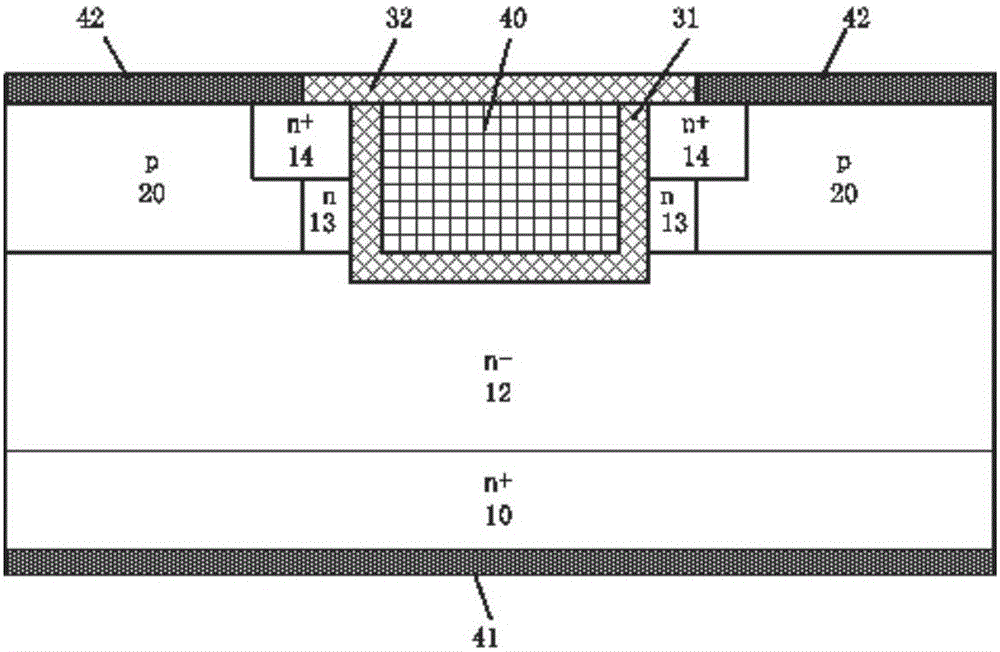

[0081] The device fabrication of the embodiment of the present invention can refer to Figure 4-12 description, as in Figure 4 On the n-type silicon carbide substrate 10 shown and the n-type silicon carbide drift layer 12 thereon, an ion implantation mask is formed and patterned, and p-type doped impurity aluminum is implanted into the n-type layer 12 to form a Figure 5 P-wells 20 are shown with a certain spacing.

[0082] Such as Figure 6 As shown, an n+ silicon carbide source region 14 is formed on the p well 20 and the n-type silicon carbide drift layer 12 by fabricating a masking film and patterning it and implanting nitrogen ions.

[0083] Such as Figure 7 As shown, continue to implant low dose nitrogen doped impurities to provide an n-type doped region for forming an n-type channel 13 between the p-type silicon carbide regions 20 .

[0084] Such as Figure 8 As shown, a masking film is formed and patterned in the region corresponding to the n+ silicon carbide so...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More