A Fractional Frequency Division Circuit for Spurious Suppression

A fractional frequency division and circuit technology, which is applied in the field of signal sources, can solve the problems of phase noise deterioration, low precision of fractional frequency, and high cost, so as to improve the level of phase noise and spurs, suppress spurs and phase noises, and reduce costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

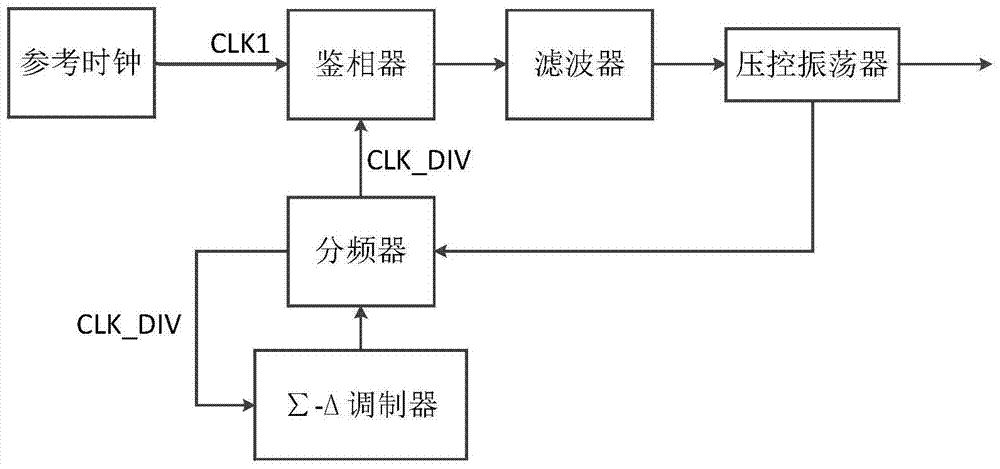

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

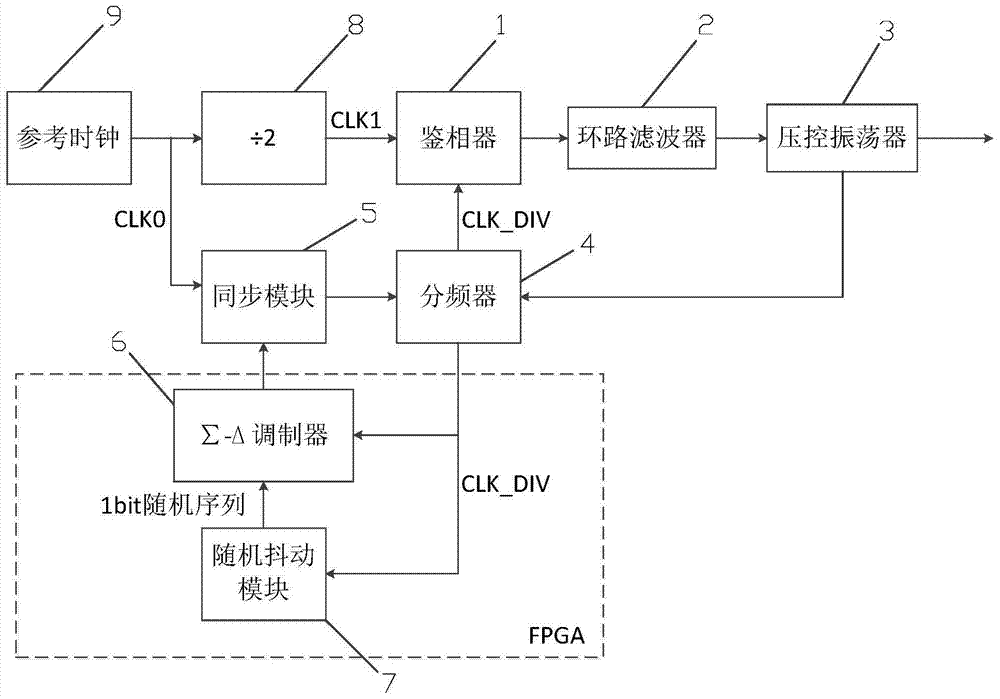

[0023] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

[0024] A fractional frequency division circuit for spurious suppression, including a phase detector 1, a loop filter 2, a voltage-controlled oscillator 3, a frequency divider 4, a synchronization module 5, a Σ-Δ modulator 6, and a random dithering module 7 and a divide-by-two frequency divider of 8.

[0025] Among them, the phase detector 1, the loop filter 2, the voltage-controlled oscillator 3, the frequency divider 4, the synchronization module 5 and the two-frequency divider 8 are all analog circuit devices; the Σ-Δ modulator 6 and the random dithering Module 7 is a digital circuit device, implemented in FPGA.

[0026] The divide-by-two frequency divider 8, the phase detector 1, the loop filter 2 and the voltage-controlled oscillator 3 are connected in sequence.

[0027] One output signal of the voltage-controlled oscillator 3 is directly ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More