Hybrid interconnection structure for network-on-chip, network node encoding method and hybrid routing algorithm thereof

A network node, network-on-chip technology, applied in data exchange networks, forward error control, digital transmission systems, etc. Throughput, increase the average transmission delay, reduce the effect of the average distance of the path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

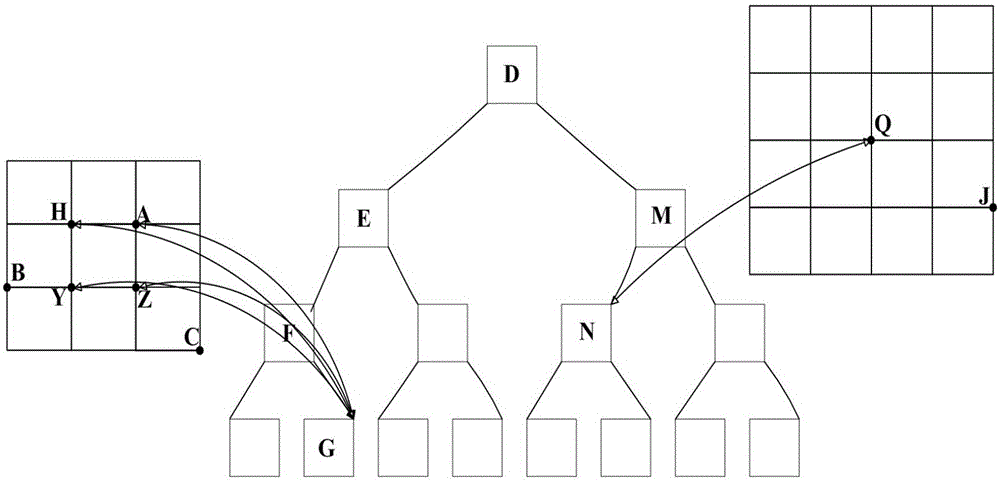

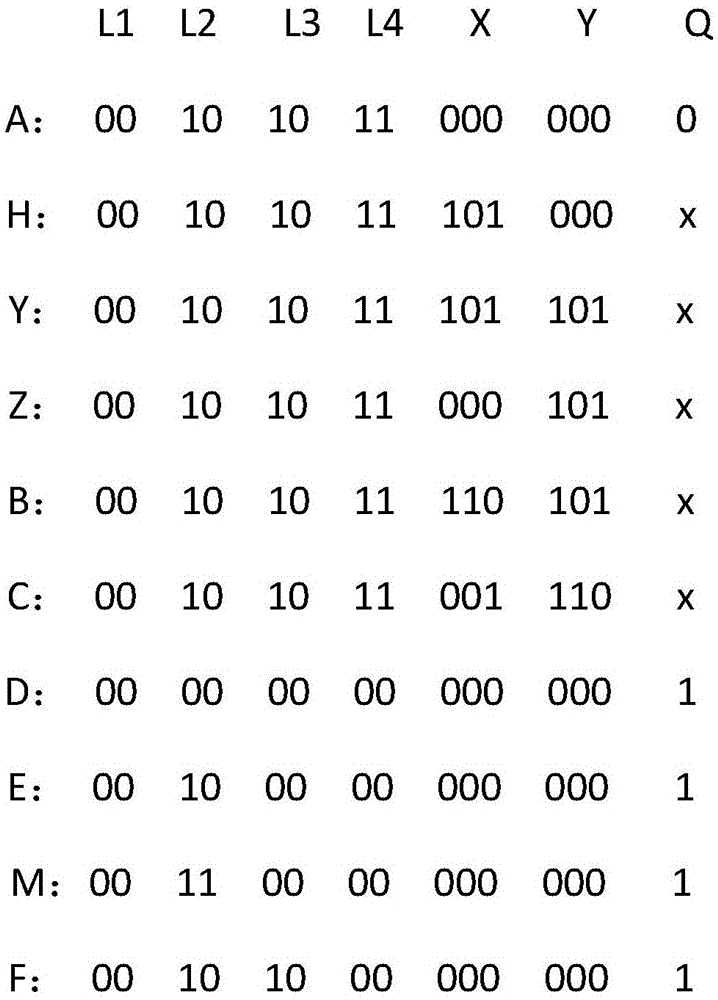

[0065] When network node B communicates with network node C, network node B is the source node, network node C is the target node, and it is judged that network node B and network node C are network nodes on a two-dimensional mesh structure, and are the same two-dimensional mesh For the network nodes on the network, the XY routing algorithm is executed. The XY coordinates of the network node B are (110, 101), and the XY coordinates of the network node C point are (001, 110). According to the calculation method of the offset, Xoffset can be obtained. =011, Yoffset=101, converted to decimal Xoffset is +3, Yoffset is -1. Therefore, take three steps in the positive direction of the X axis, and then take one step in the negative direction of the Y axis, that is, from the network node B to the network node C.

Embodiment 2

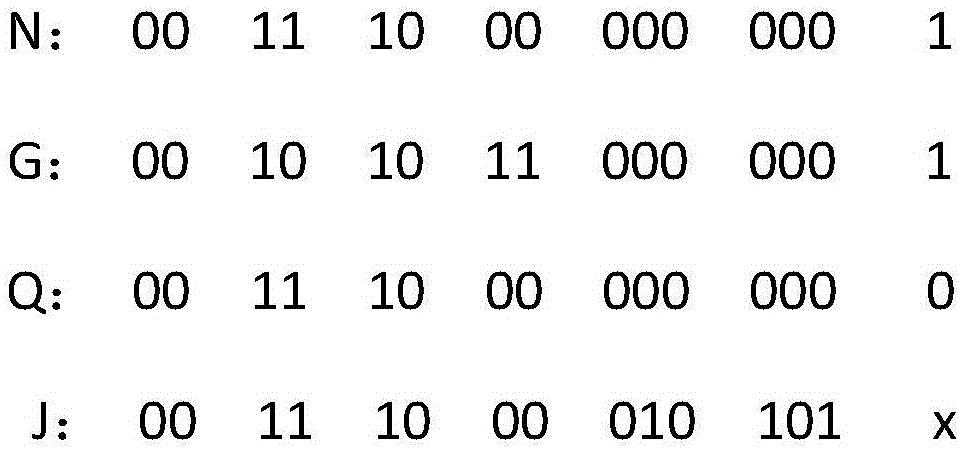

[0067] The network node G communicates with the network node N, the network node G is the source node, the network node N is the target node, and it is judged that the network node G and the network node N are all nodes on the binary tree structure of the global network, then the binary tree routing algorithm is directly executed. The process As follows, the network node G point binary tree code is 00_10_10_11, the network node N point binary tree code is 00_11_10_00, it is found that the first unequal bit segment from left to right is L2, and then the source node G is found not to be the first time from right to left The bit segment of 00 is L, and m=i-j+1=4-2+1=3 is calculated, that is, it needs to search up the parent node 3 times to reach the first forked node D. Then take the network node D as the starting point, and start from the L2 bit of the target node N to the right according to the figure 2 To judge, the L2 bit of the target node N is 11, route to the right child ...

Embodiment 3

[0069] The network node B communicates with the network node J, the network node B is the source node, and the network node J is the target node. According to the node position determination method, it can be known that the network node B and the network node J are located on different two-dimensional mesh networks, then the network node is executed first. In the routing algorithm from B to network node G on the binary tree structure, network node B first routes to network node Y. Referring to Embodiment 1, it can be known that the network node Y can be reached by walking in the positive direction of X once. Then the network node Y is directly routed to the network node G, and then the route from the network node G to the network node N is performed, referring to the second embodiment. After routing from network node G to network node N, perform direct routing from network node N to corresponding network node Q, and then perform routing from network node Q to network node J. Re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More