Manufacturing method of ring-fence non-junction nanowire transistor

A nanowire and transistor technology, applied in the micro-nano field, can solve the problems of complex transistor fabrication process and process incompatibility, and achieve the effect of improving current driving capability and suppressing mobility degradation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0026] The preparation method of the gate-enclosed junction-free nanowire transistor provided by the present invention adopts MOCVD to epitaxially grow doped nanowire arrays on III-V materials, and transfers the nanowires by thermally peeling tape and fixing the panel, on the silicon substrate Fabricate a junctionless nanowire transistor with a gate-enclosed structure on the bottom.

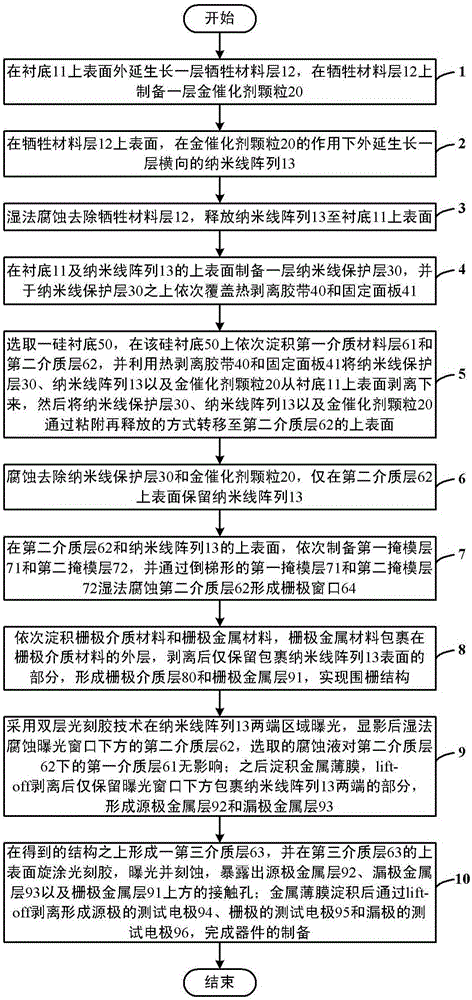

[0027] see Figure 1 to Figure 11 As shown, the present invention provides a method for preparing a gate-enclosed junctionless nanowire transistor, the method comprising:

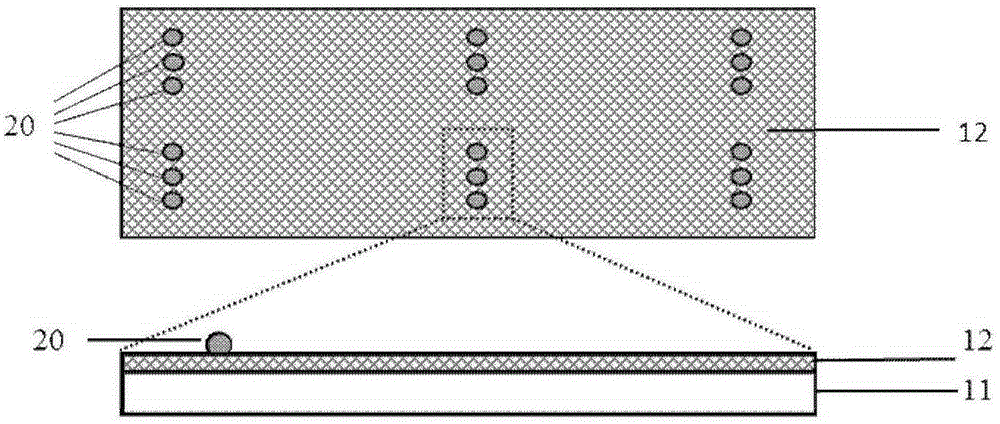

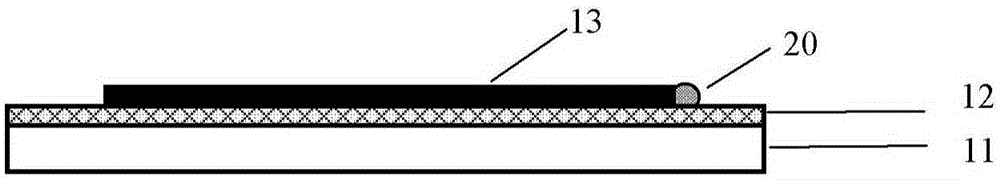

[0028] Step 1: First, epitaxially grow a layer of sacrificial material layer 12 on the upper surface of the substrate 11, and then, on the sacrificial material layer 12,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More