Method and system for optimizing analogue integrated circuit

A technology of integrated circuits and optimization methods, which is applied in the fields of electrical digital data processing, instruments, calculations, etc., and can solve problems such as circuit yield decline and manufacturing process precision difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

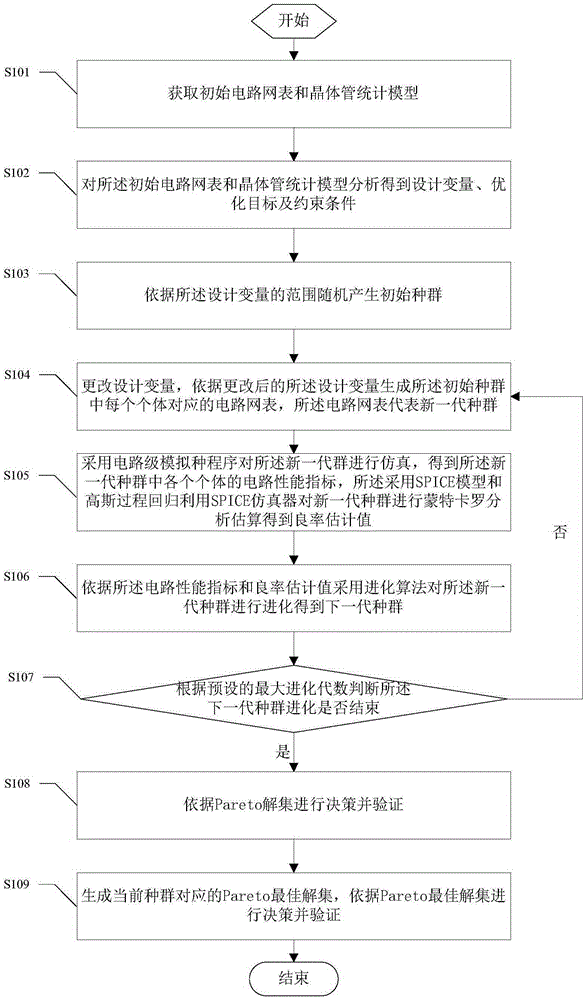

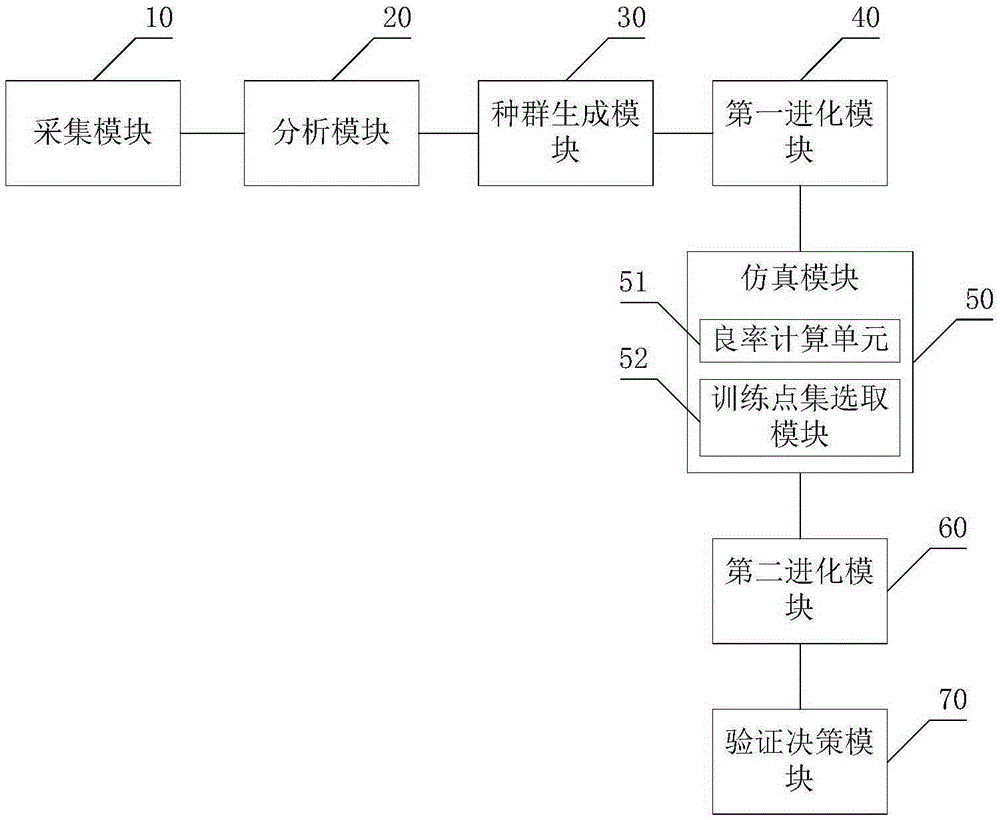

[0045] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0046] In the traditional rapid design and optimization methods of analog integrated circuits, it is still difficult to use the yield rate as an optimization constraint or optimization goal in the optimization process. The main reason is that the accurate estimation of the circuit yield rate is obtained by Monte Carlo analysis of the SPICE model (mainly the BSIM model of CMOS transistors) provided by the chip foundry with process statistics information. Monte Carlo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More