Pseudo-differential capacitive successive approximation register analog-digital converter

An analog-to-digital converter and successive approximation technology, applied in analog/digital conversion, code conversion, instruments, etc., can solve the problems of inaccurate double relationship and limit the improvement of SARADC accuracy, so as to save chip area, improve accuracy, double-relationship exact effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

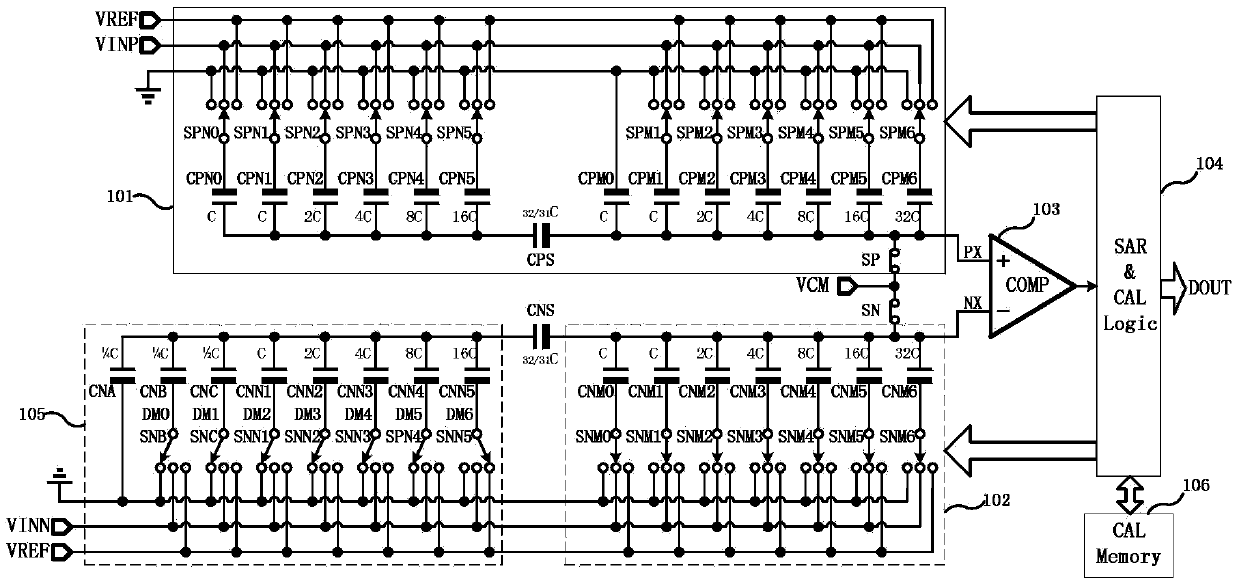

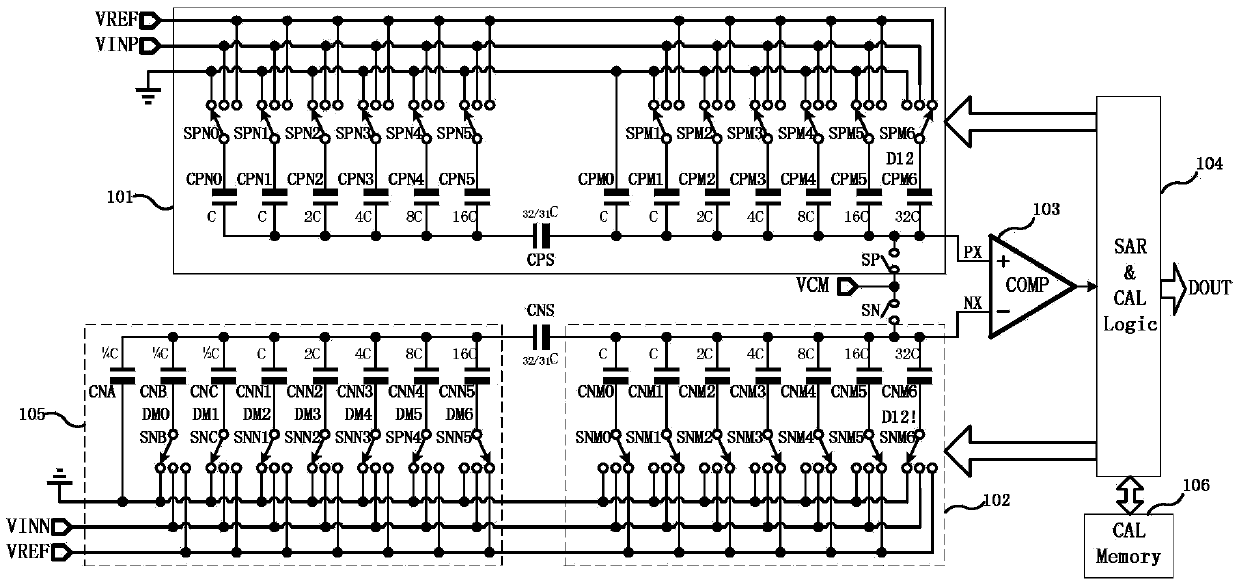

[0033] Such as figure 1 Shown is the circuit diagram of the pseudo-differential capacitive successive approximation analog-to-digital converter of the embodiment of the present invention; the pseudo-differential capacitive successive approximation analog-to-digital converter of the embodiment of the present invention includes a first capacitor array 101, a second capacitor array 102, and a calibration capacitor array 105 , a comparator (COMP) 103 , a control logic circuit (SAR&CALLogic) 104 and a memory (CALMemory) 106 .

[0034]The output terminal PX of the first capacitor array 101 is connected to the first input terminal of the comparator 103 and connected to the common mode level VCM through a switch SP, and the output terminal NX of the second capacitor array 102 is connected to The second input terminal of the comparator 103 is connected to the common mode level VCM through a switch SN, and the first capacitor array 101 and the second capacitor array 102 form a pseudo-di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More