Semiconductor capacitor based on through-silicon via technology and manufacturing method and packaging structure thereof

A technology for semiconductors and capacitors, applied in the field of semiconductor capacitors and their manufacturing based on through-silicon via technology, can solve the problems of large volume, incompatibility of semiconductor processes, and increase in chip cost, so as to increase electrode area, reduce parasitic effects, and improve capacitance. effect of value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The technical solution of the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

[0049] The invention discloses an embodiment of a manufacturing method of a semiconductor capacitor, such as Figure 1-Figure 9 As shown, the following steps are included in sequence:

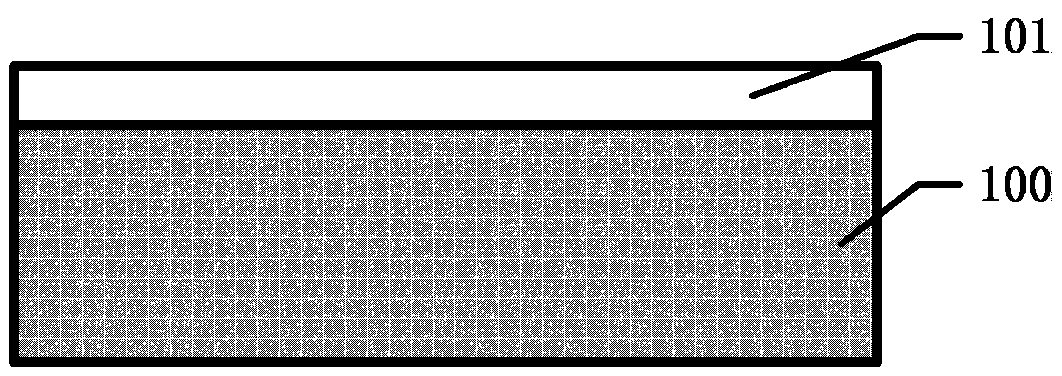

[0050] In the first step, a layer of insulating layer 101 is deposited on the substrate 100, such as figure 1 shown;

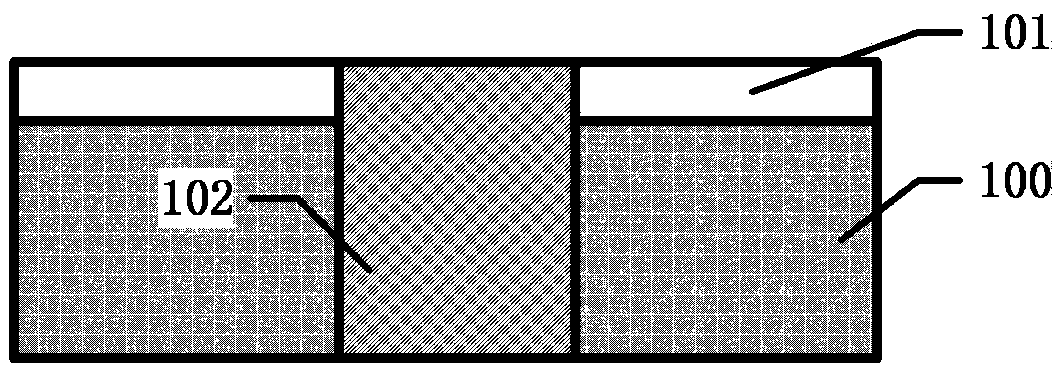

[0051] The second step is to etch a via hole through the substrate 100 and the insulating layer 101, and then fill the bottom electrode metal column 102 in the via hole, such as figure 2 shown;

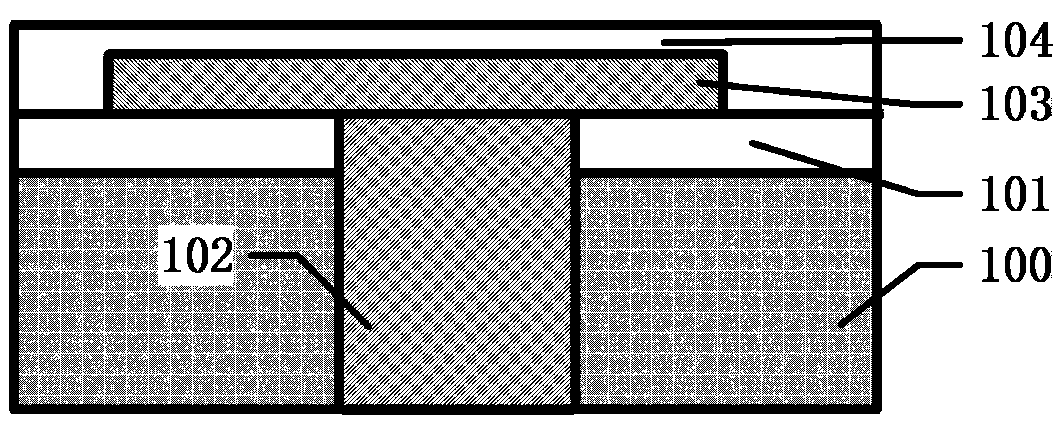

[0052] In the third step, the first metal layer 103 and the first dielectric layer 104 are successively deposited on the surface of the insulating layer 101, such as image 3 shown;

[0053] The fourth step is to form the second metal layer 105 and the second dielectric layer 106 based on the successive deposit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More