Formation method of semiconductor structure

A semiconductor and amorphous silicon technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of fin field effect transistor stability to be improved, and achieve the effect of preventing injection damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background, the manufacturing process stability of the fin field effect transistor in the prior art still needs to be improved. For example, in the manufacturing process of the fin field effect transistor, the problems of fin damage and isolation layer loss will affect The electrical performance of the formed FinFET will be affected.

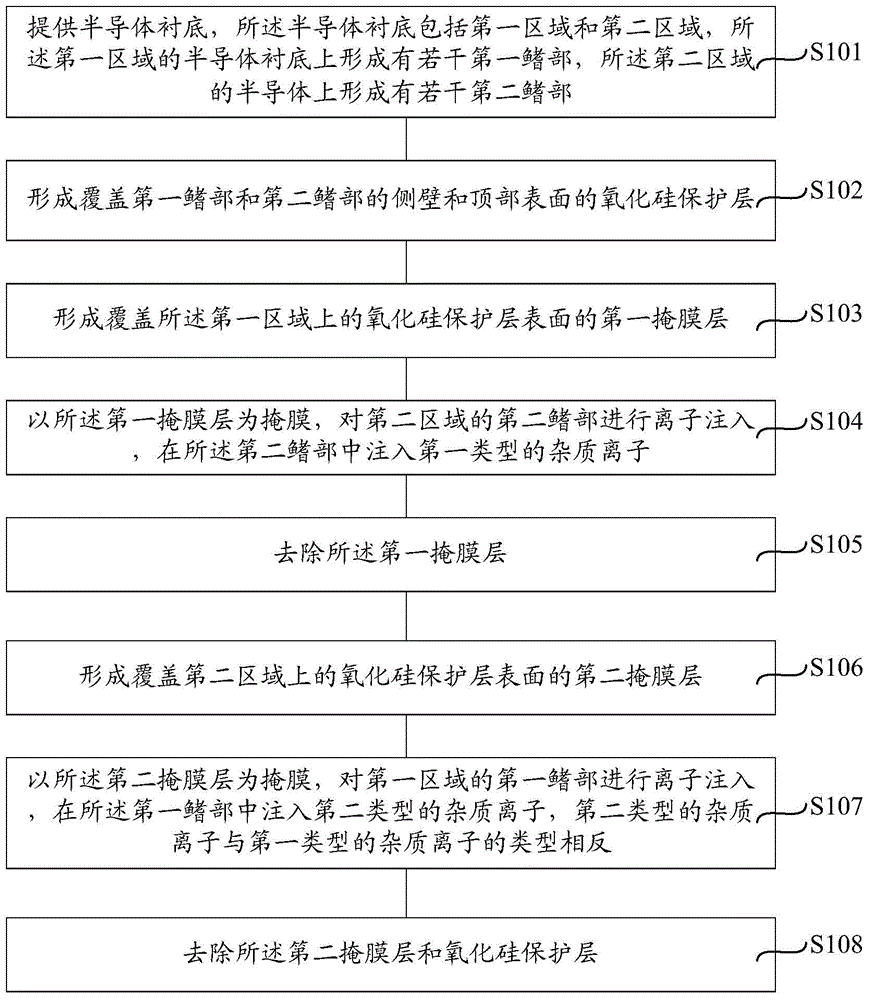

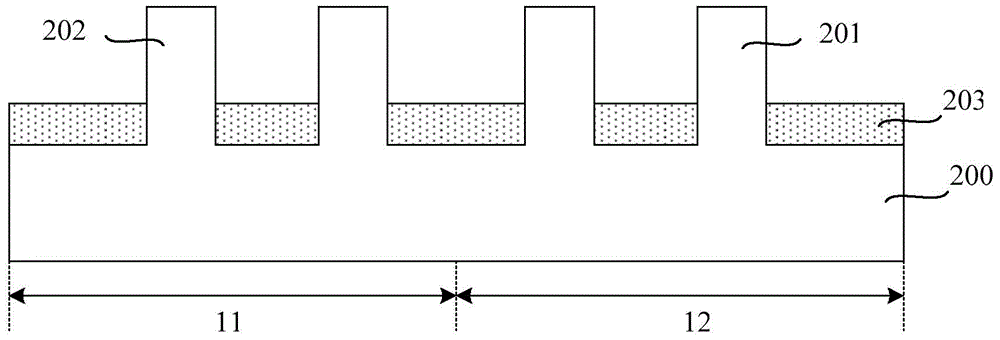

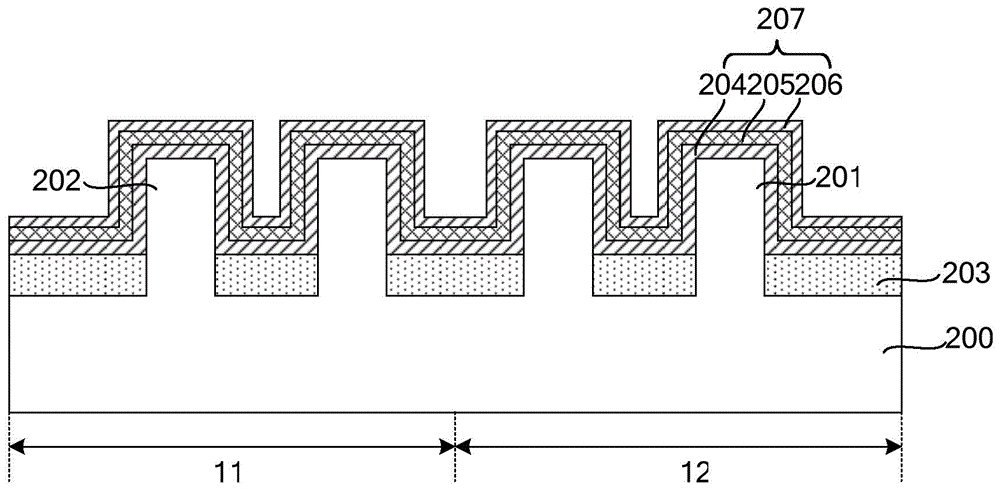

[0033] For the formation process of the fin field effect transistor in the prior art, please refer to figure 1 , comprising, step S101, providing a semiconductor substrate, the semiconductor substrate includes a first region and a second region, a plurality of first fins are formed on the semiconductor substrate in the first region, and a semiconductor substrate in the second region A plurality of second fins are formed on the substrate; step S102, forming a silicon oxide protection layer covering the sidewalls and top surfaces of the first fins and the second fins; step S103, forming an oxide layer covering the first ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More