A kind of manufacturing method of finfet device

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as negative impact on device performance, improve performance and yield, avoid implant damage, and avoid ion implantation shadow effects Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] In order to improve the performance of FinFET devices, the present invention proposes a manufacturing method of FinFET devices, such as image 3 As shown, it includes the following main steps:

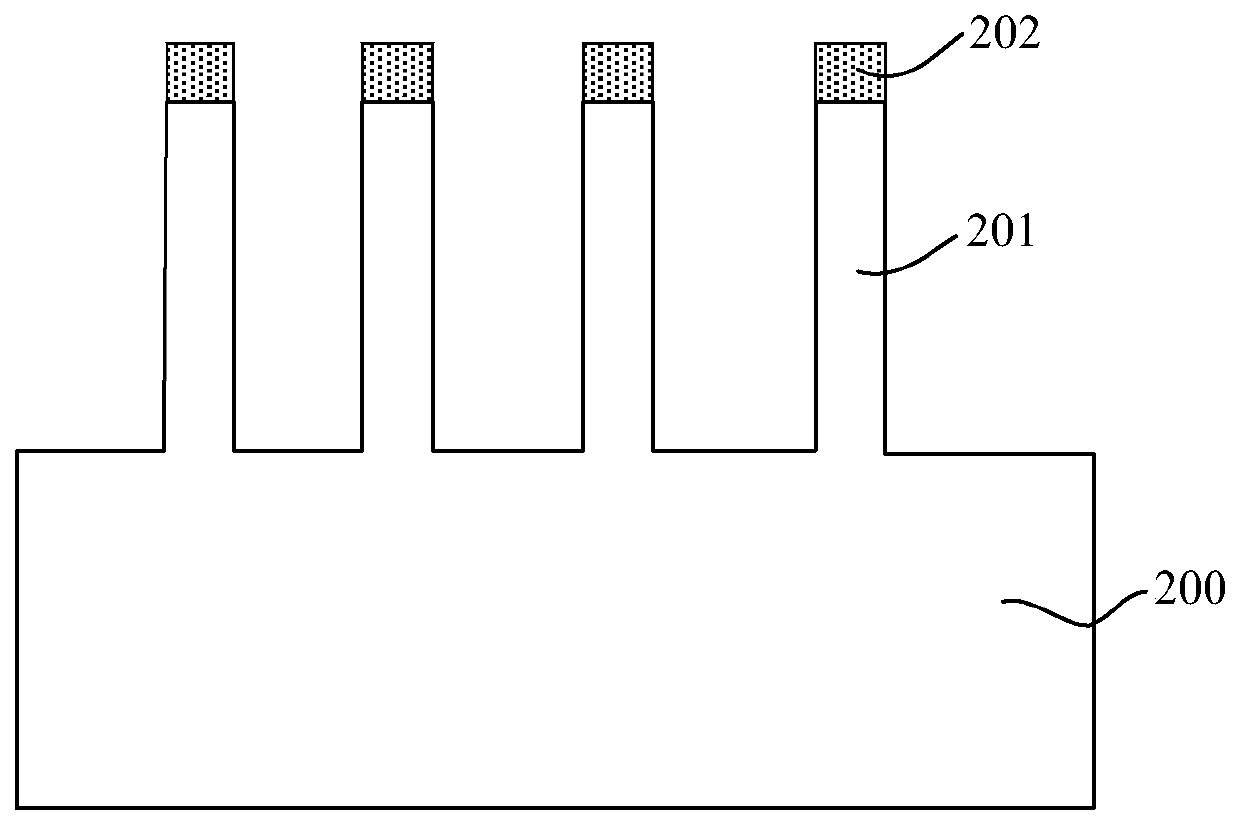

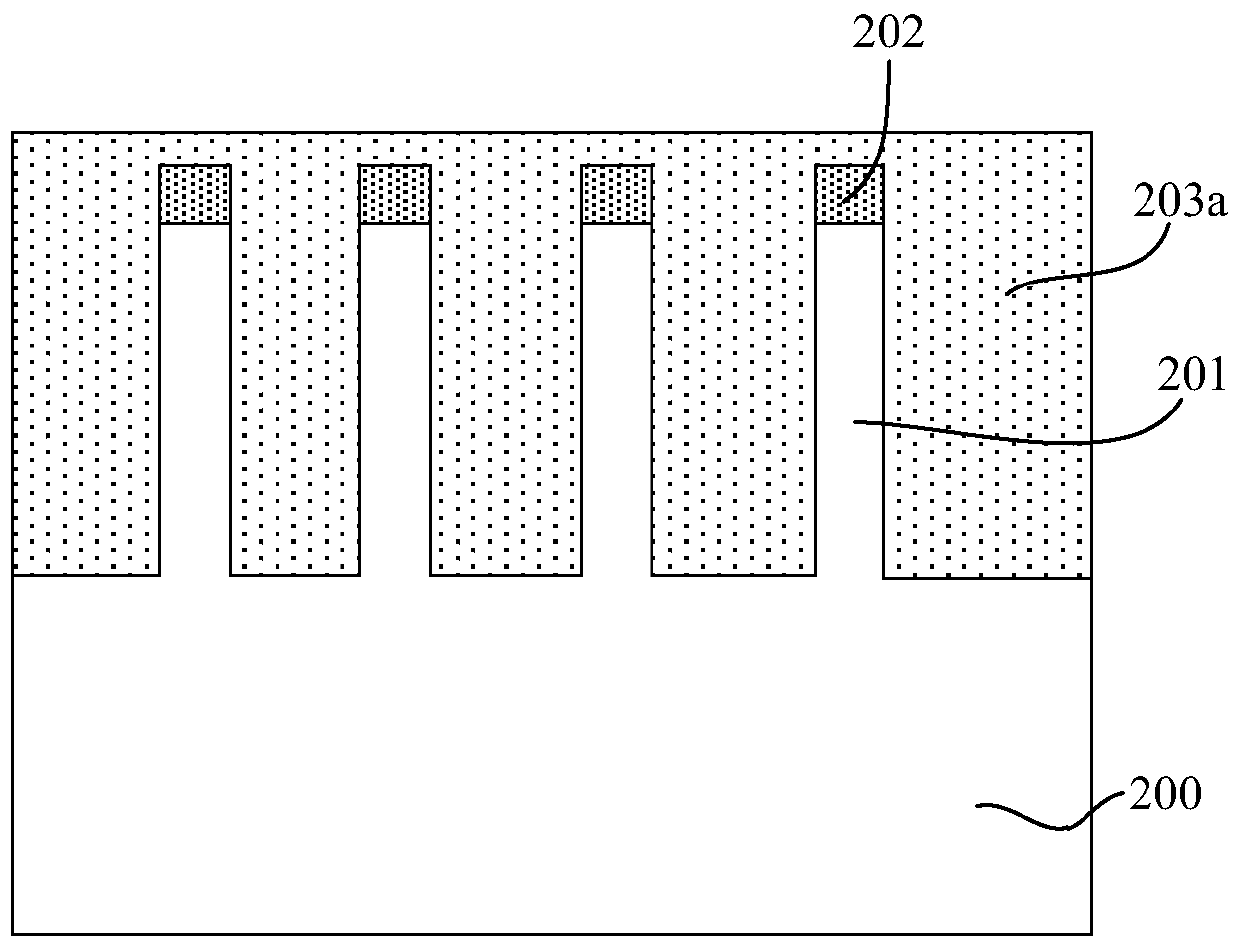

[0042] In step S301, a semiconductor substrate is provided, a plurality of fins are formed on the semiconductor substrate, a hard mask layer is formed on the top of the fins, and the semiconductor substrate between the fins An isolation structure is formed on the bottom, wherein the top surface of the isolation structure is lower than the top surface of the fin;

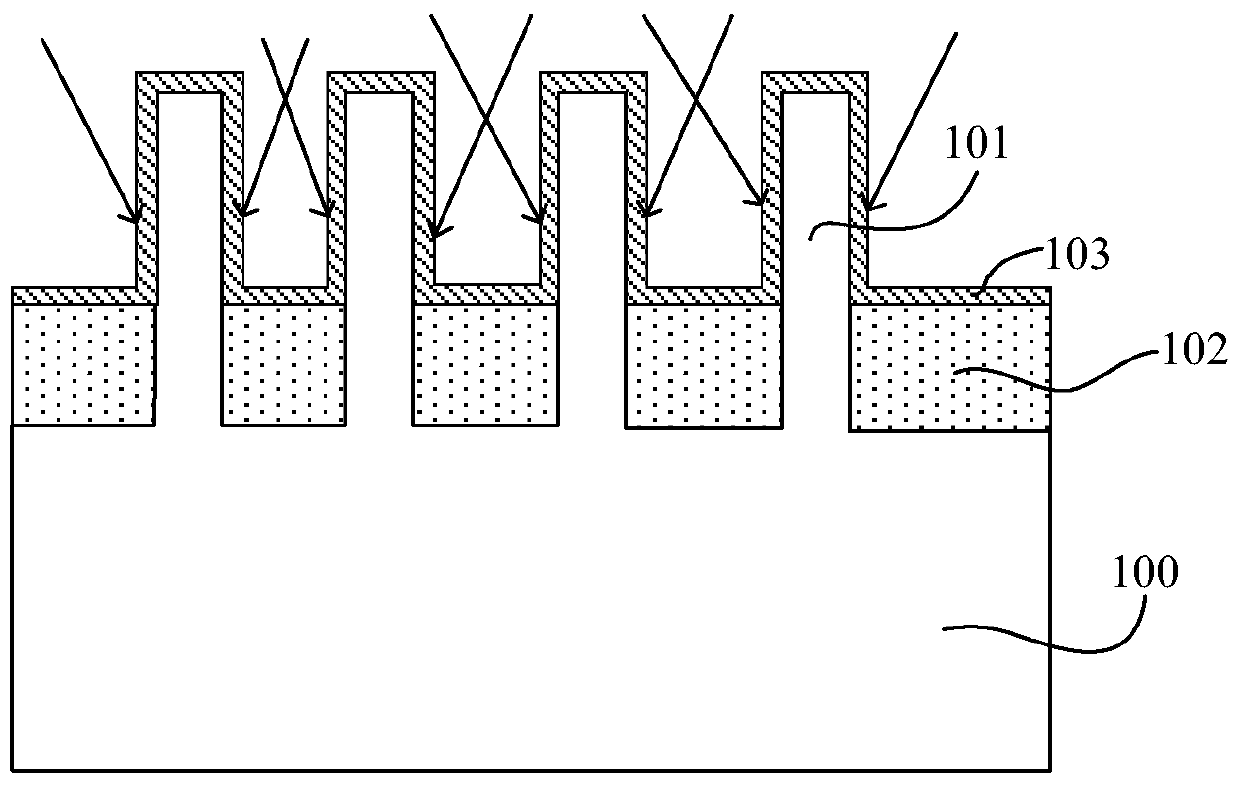

[0043] In step S302, a first threshold voltage ion implantation is performed to laterally diffuse dopant impurities into the bottom of the fin, and the implantation direction of the first threshold voltage ion implantation is perpendicular to the surface of the semiconductor substrate;

[0044] In step S303, performing a first thermal annealing treatment, so that the dopant impurity implanted into the bottom of the fin ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More