Patents

Literature

49results about How to "Short etching time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

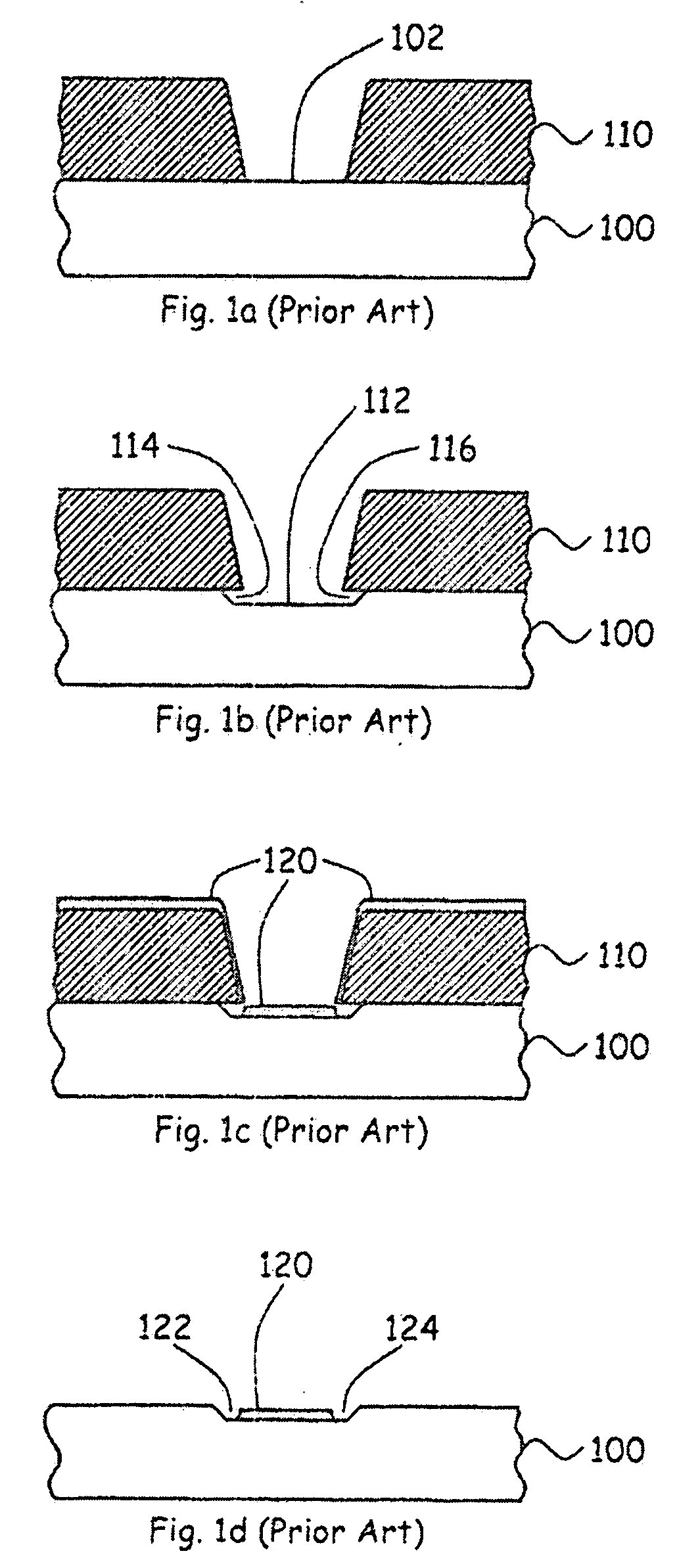

Methods of Minimizing Etch Undercut and Providing Clean Metal Liftoff

ActiveUS20090111061A1Inhibition effectAdequate step coverageSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusResistOxygen

A method of minimizing etch undercut and providing clean metal liftoff in subsequent metal deposition is provided. In one embodiment a bilayer resist mask is employed and used for etching of underlying substrate material and subsequent metal liftoff. In one embodiment, the top layer resist such as positive photoresist which is sensitive to selected range of energy, such as near UV or violet light, is first patterned by standard photolithography techniques and resist development in a first developer to expose portion of a bottom resist layer which is sensitive to a different selected range of energy, such as deep UV light. The exposed portion of the bottom layer resist is then removed by anisotropic etching such as oxygen reactive ion etching using the top layer resist as the etch mask to expose portion of the underlying substrate. This minimizes the undercut in the bottom resist around the top photoresist opening. The resultant patterned bilayer resist stack is then used as the etch mask for the subsequent etching of the exposed portion of the underlying substrate material. Because there is no undercut in the bottom resist layer, the etch undercut in the substrate material is also minimized relative to the edges of the top photoresist opening.

Owner:TRIQUINT SEMICONDUCTOR

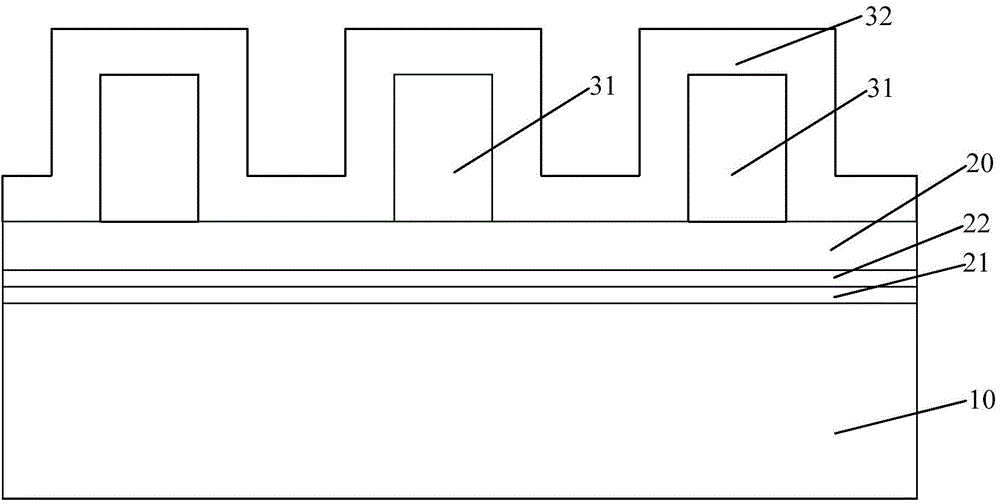

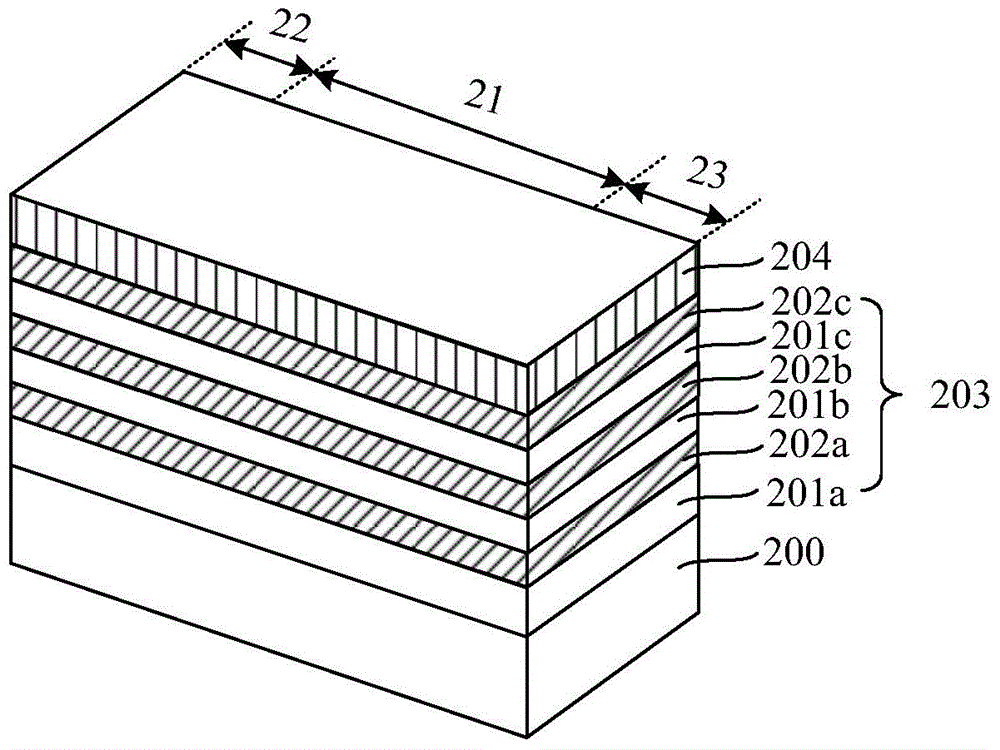

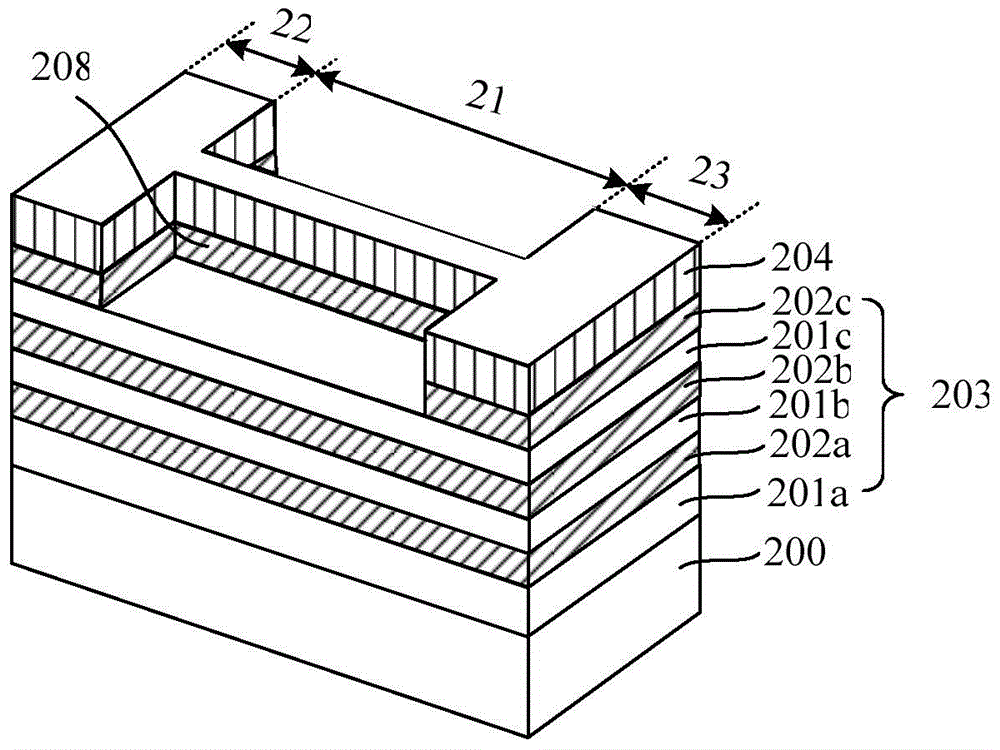

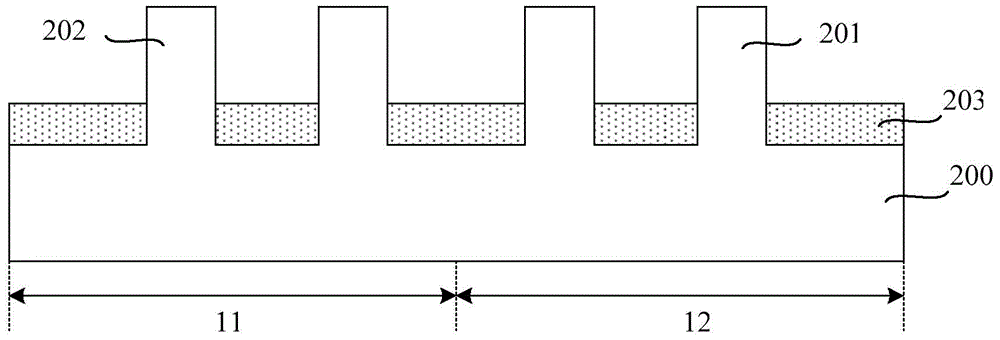

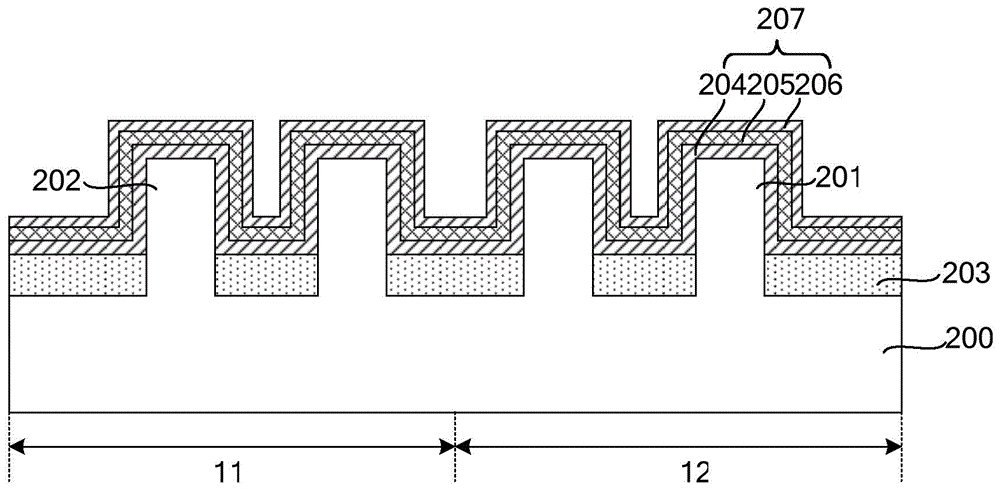

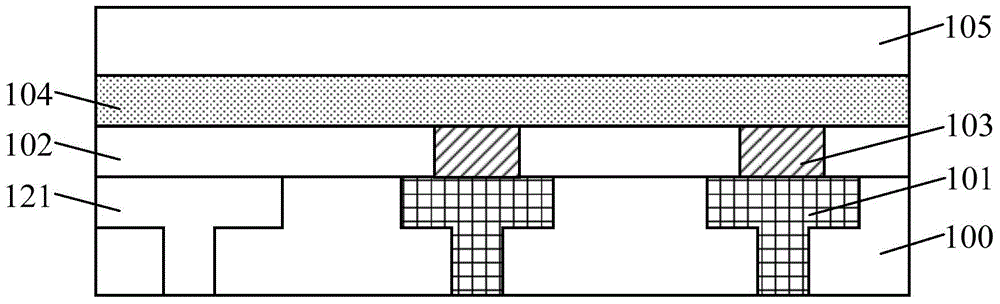

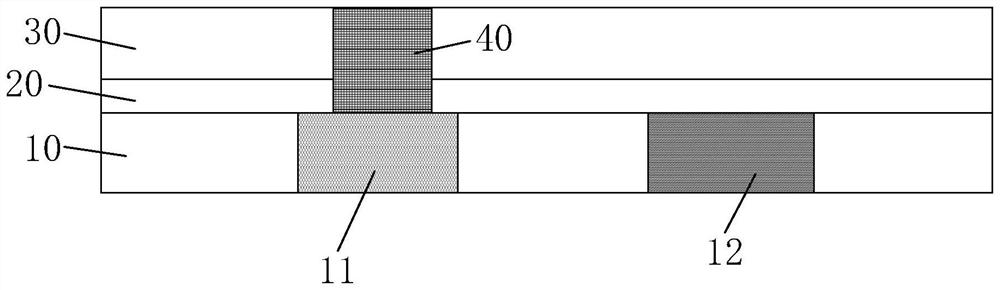

Semiconductor structure and forming method thereof

ActiveCN106206307ASmall sizeConsistent widthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The invention provides a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the steps that a semiconductor substrate is provided; a mask layer and a sacrificial material layer located on the surface of the mask layer are sequentially formed on the surface of the semiconductor substrate; the sacrificial material layer is etched to form a plurality of discrete sacrificial layers; side walls are formed on the side wall surfaces of the sacrificial layers; the sacrificial layers are removed; and supplement side walls are formed on the side wall surfaces of the side walls. By the method, improvement of the performance of the formed semiconductor structure is facilitated.

Owner:SEMICON MFG INT (SHANGHAI) CORP

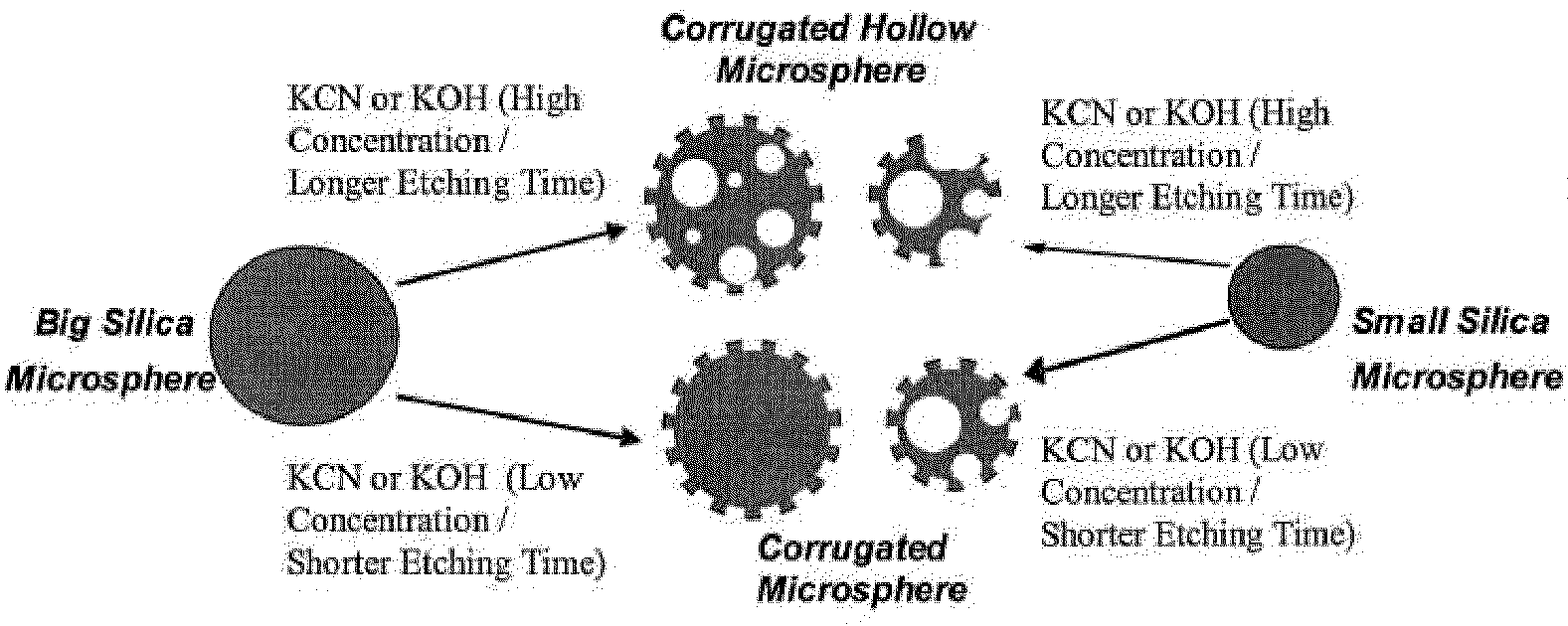

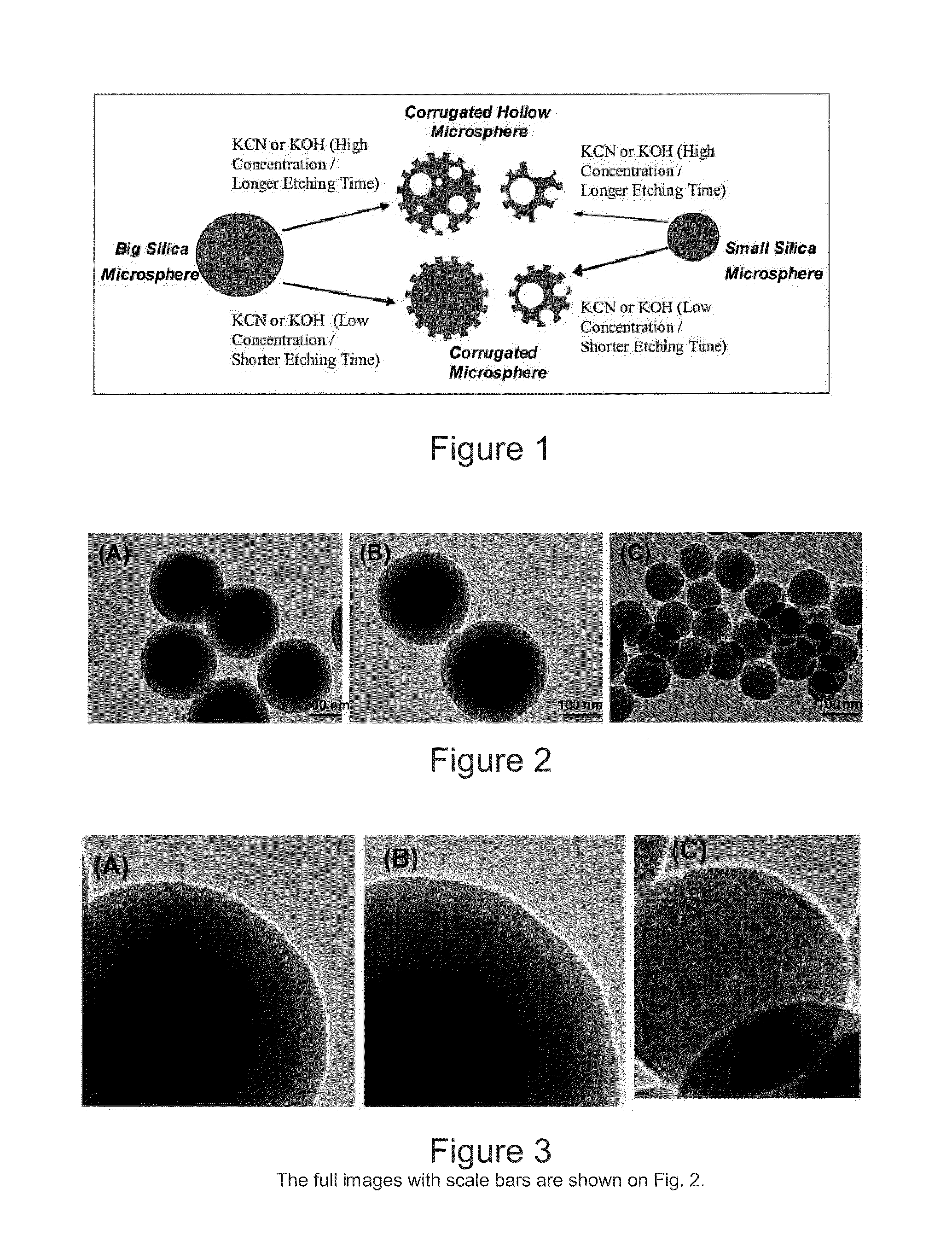

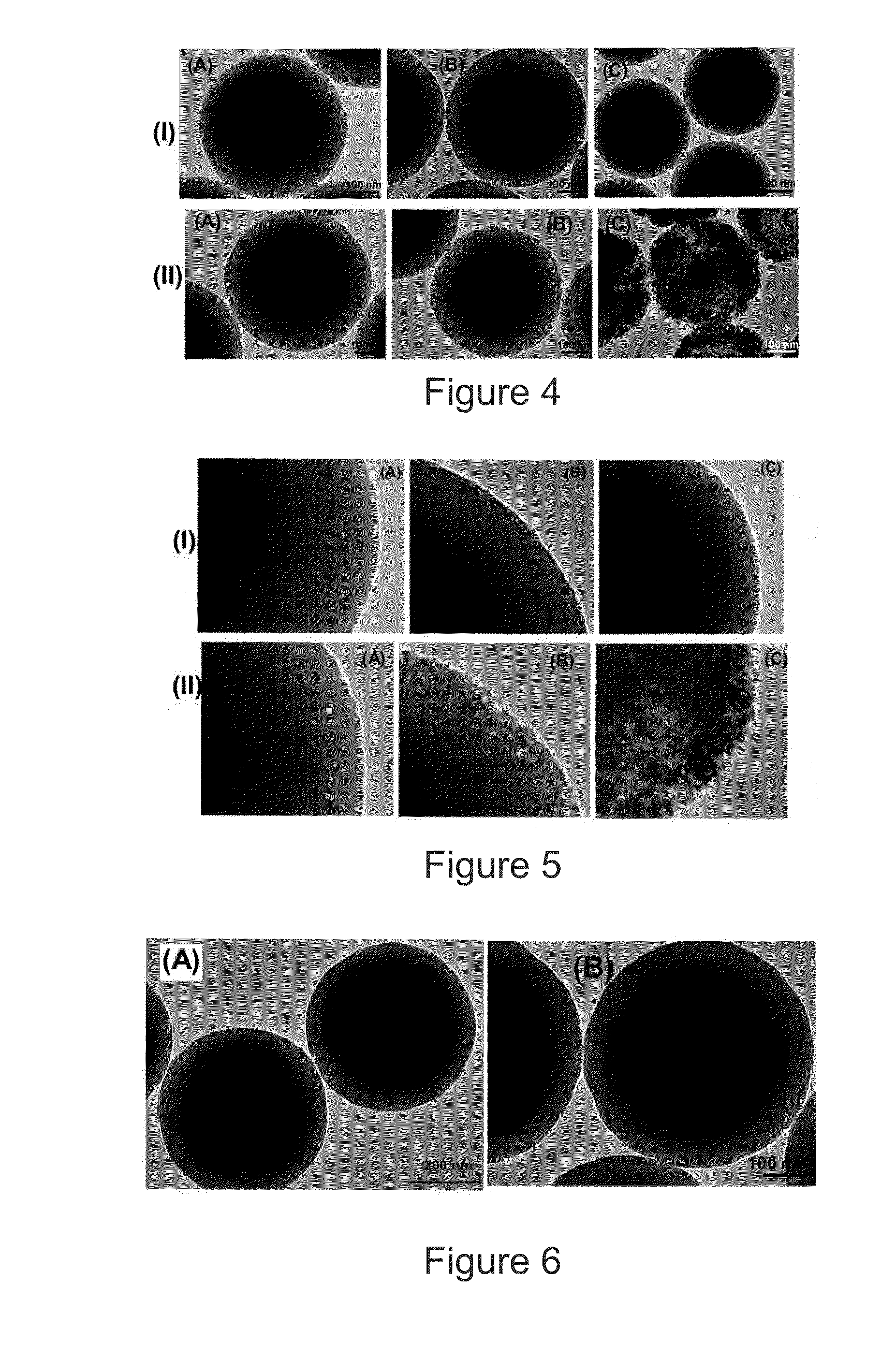

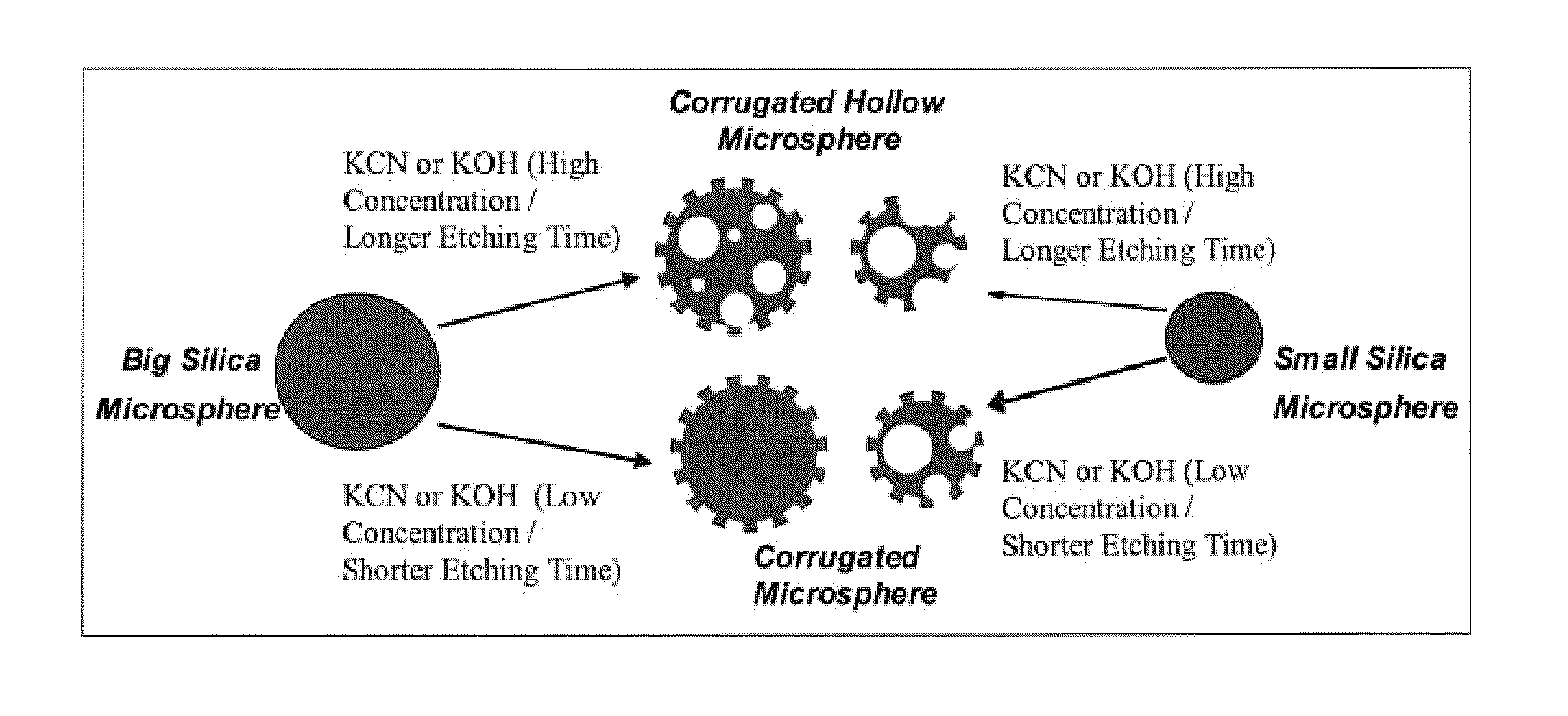

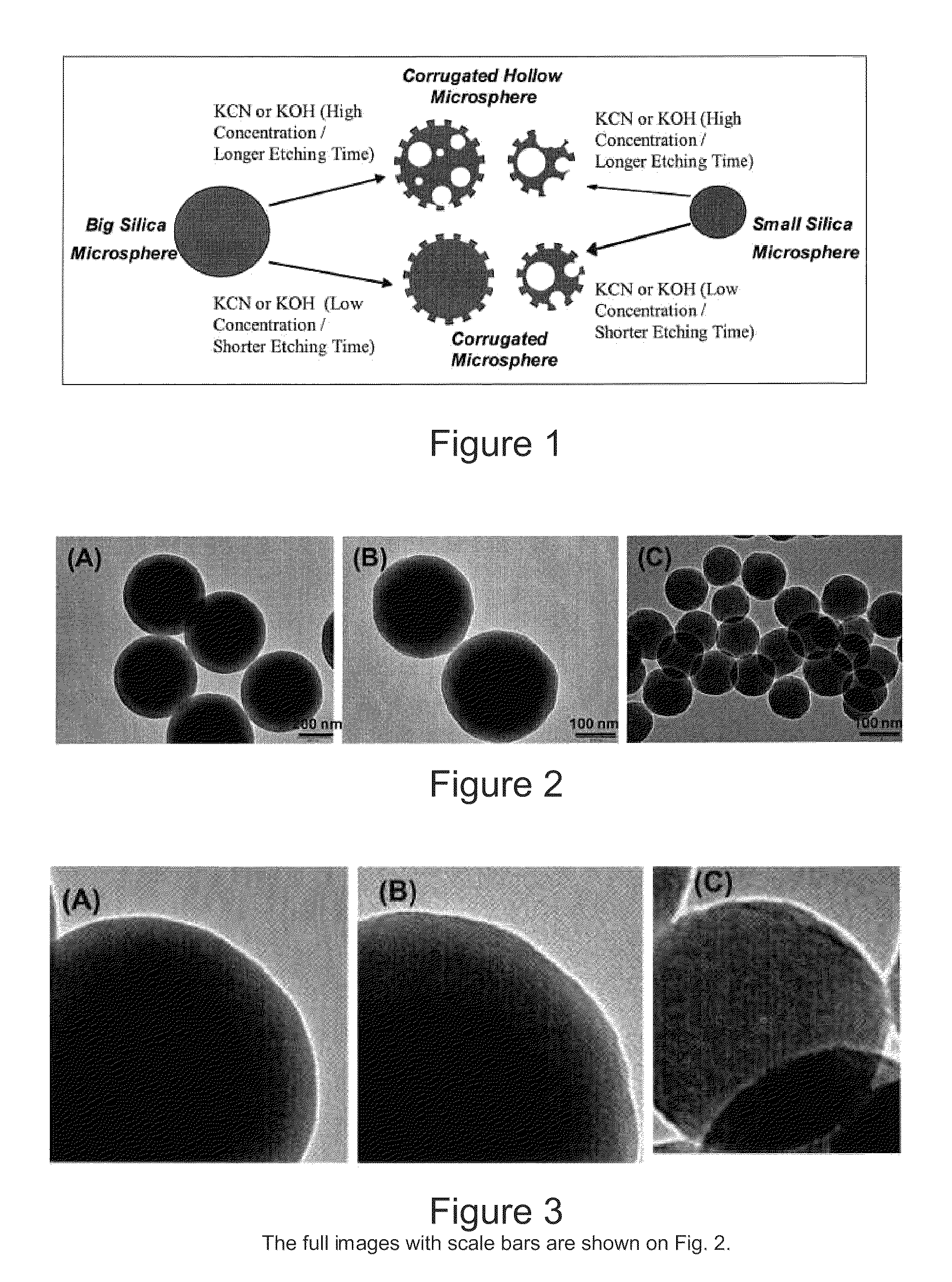

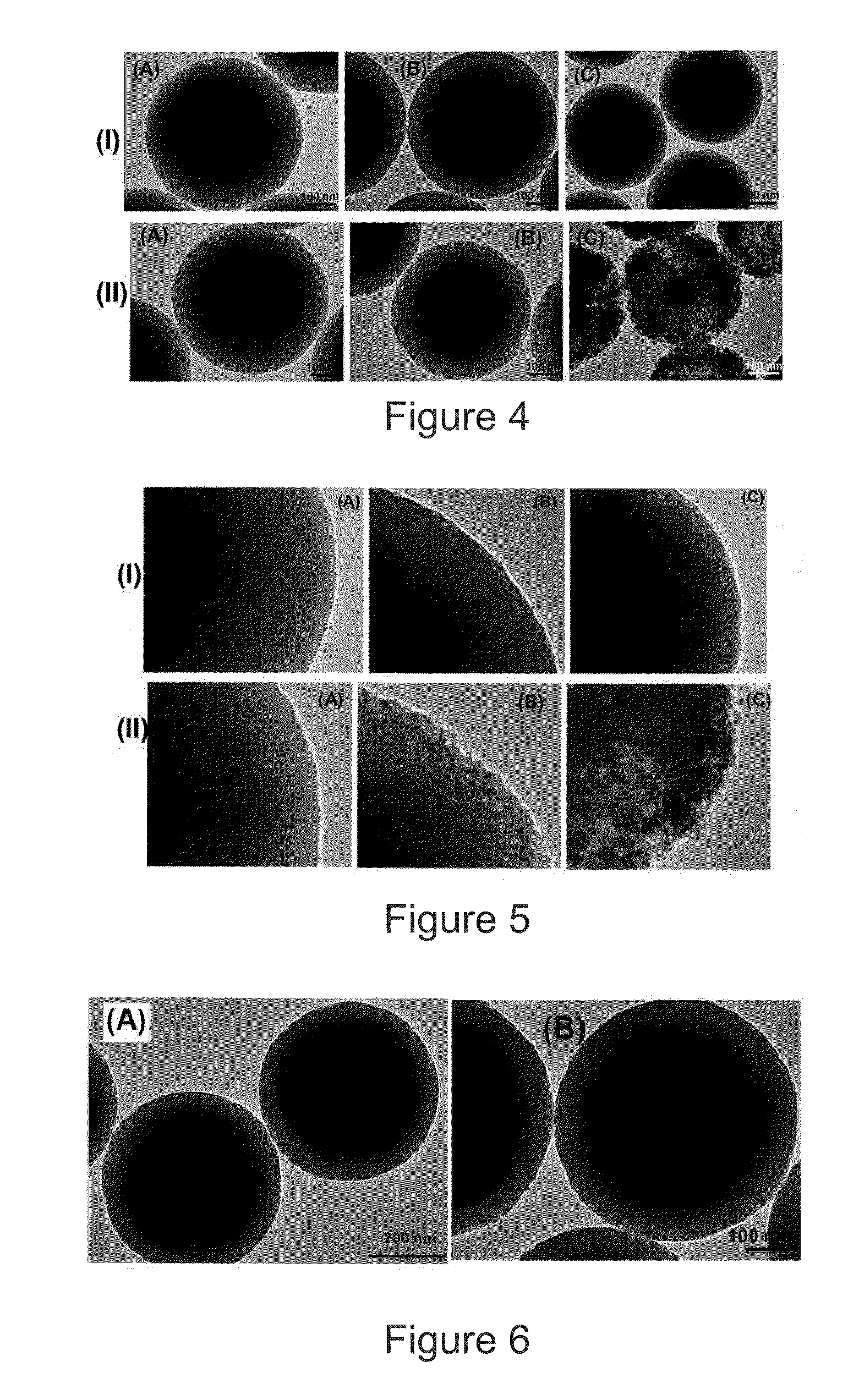

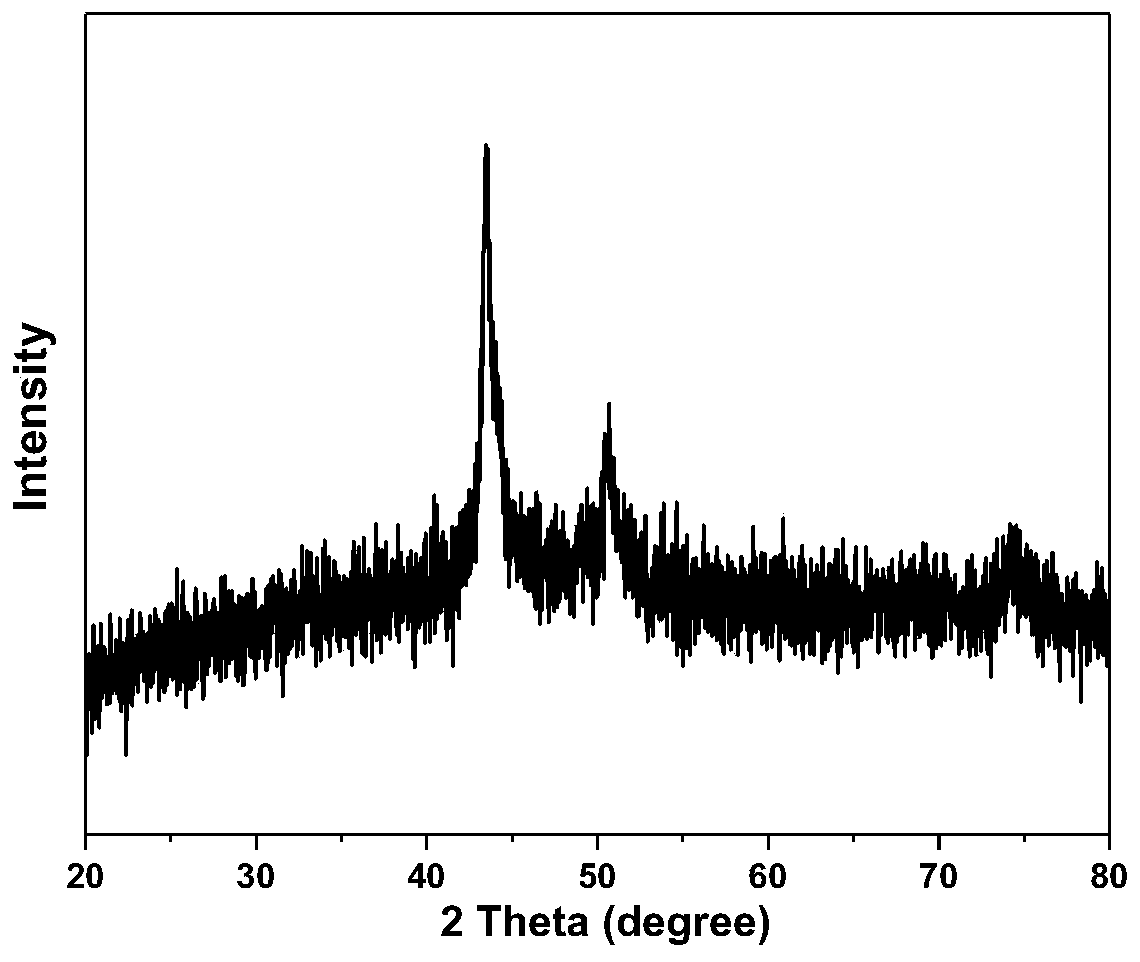

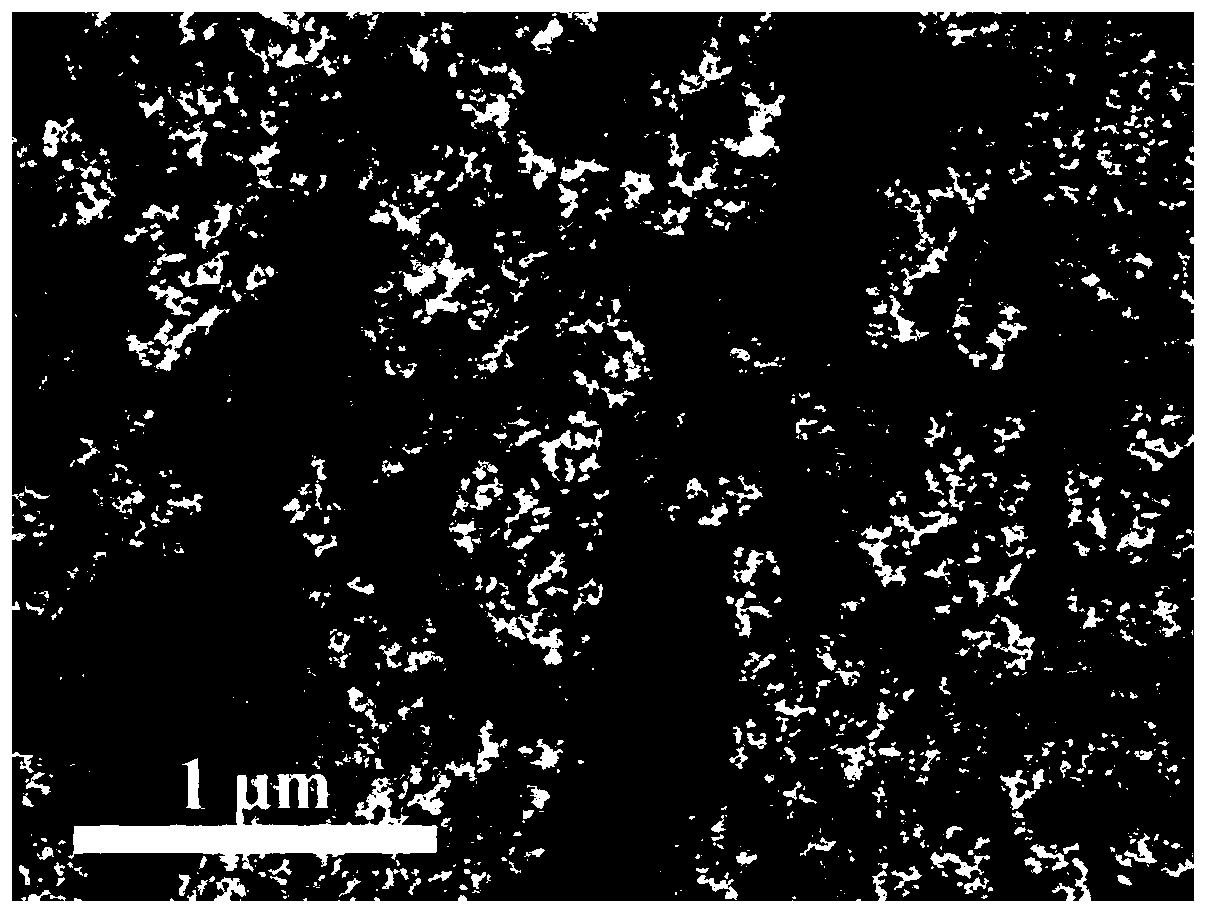

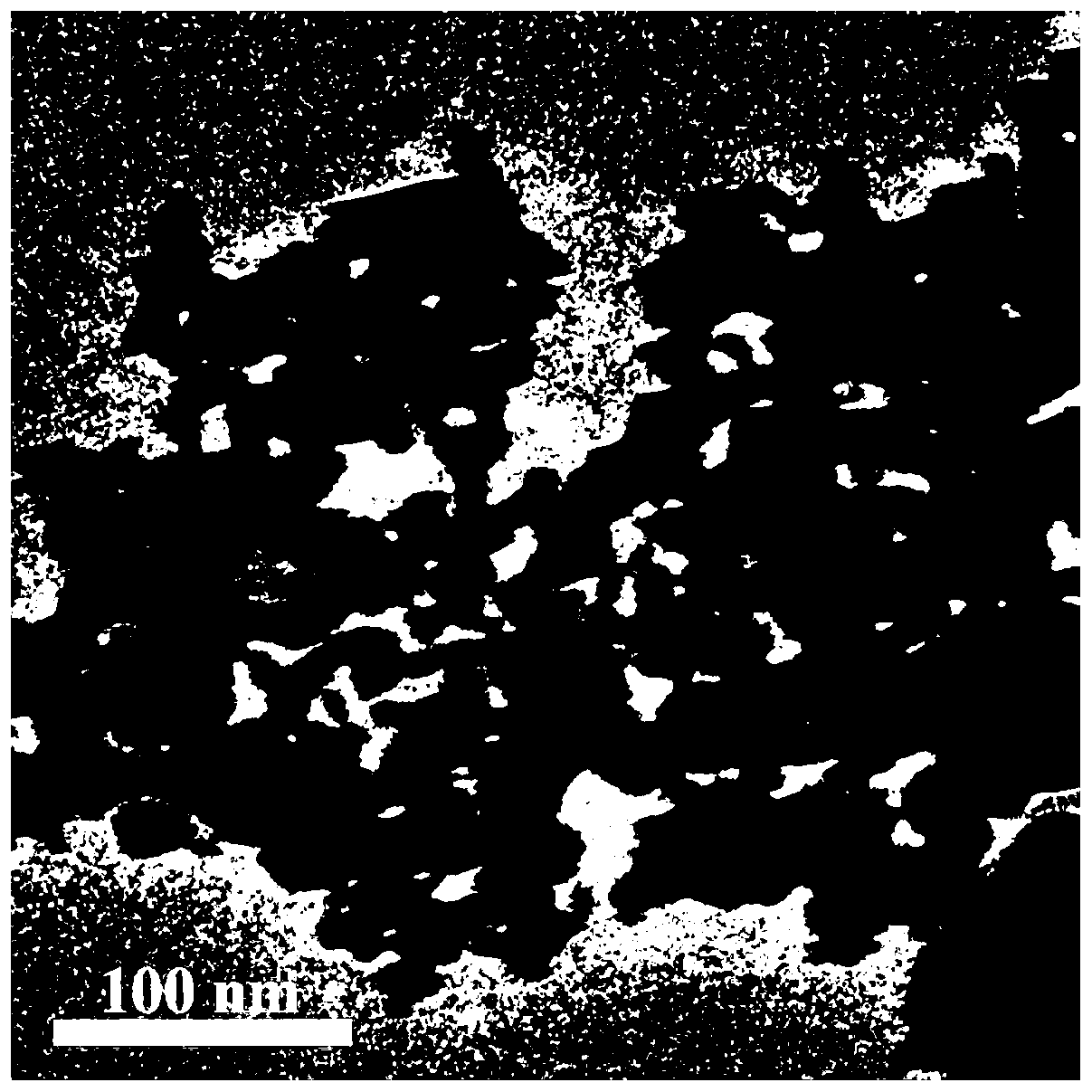

Corrugated and Nanoporous Microstructures and Nanostructures, and Methods for Synthesizing the Same

ActiveUS20100093013A1Increase adsorption capacityShort etch timePhysical/chemical process catalystsDecorative surface effectsPotassium cyanideNanometre

A method of synthesizing corrugated and nanoporous microspheres including the steps of synthesizing substantially smooth spherical microspheres, and controlled wet-etching of the substantially smooth spherical microspheres with a basic solution having a pH above 10.00 is provided. The microspheres can include, for example, silica microspheres or titania microspheres of various sized diameters of between 50 nm and 600 nm. The basic solution can include an aqueous potassium cyanide solution or an aqueous potassium hydroxide solution. Methods of using the corrugated and nanoporous microspheres described herein are also provided.

Owner:SYRACUSE UNIVERSITY

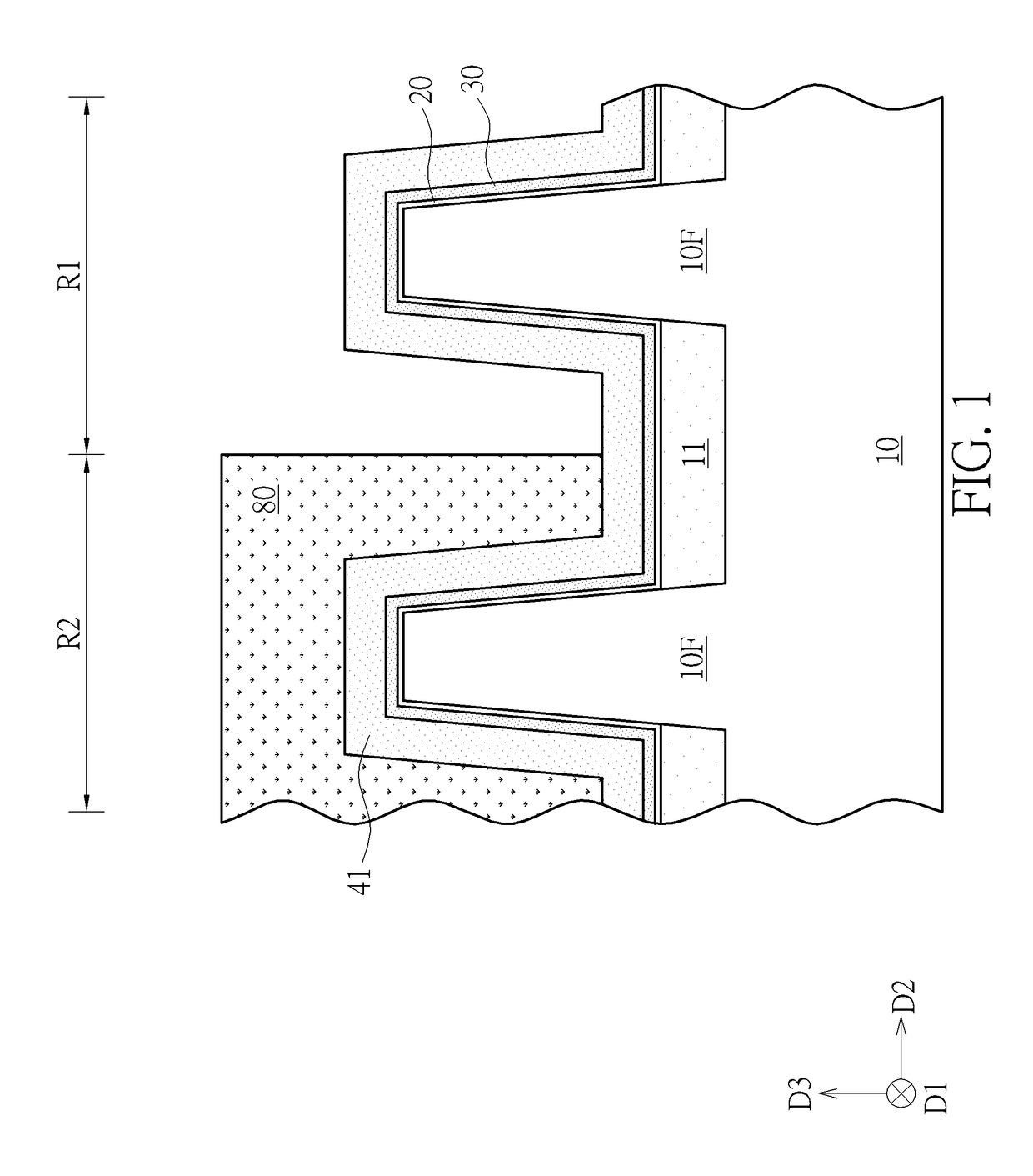

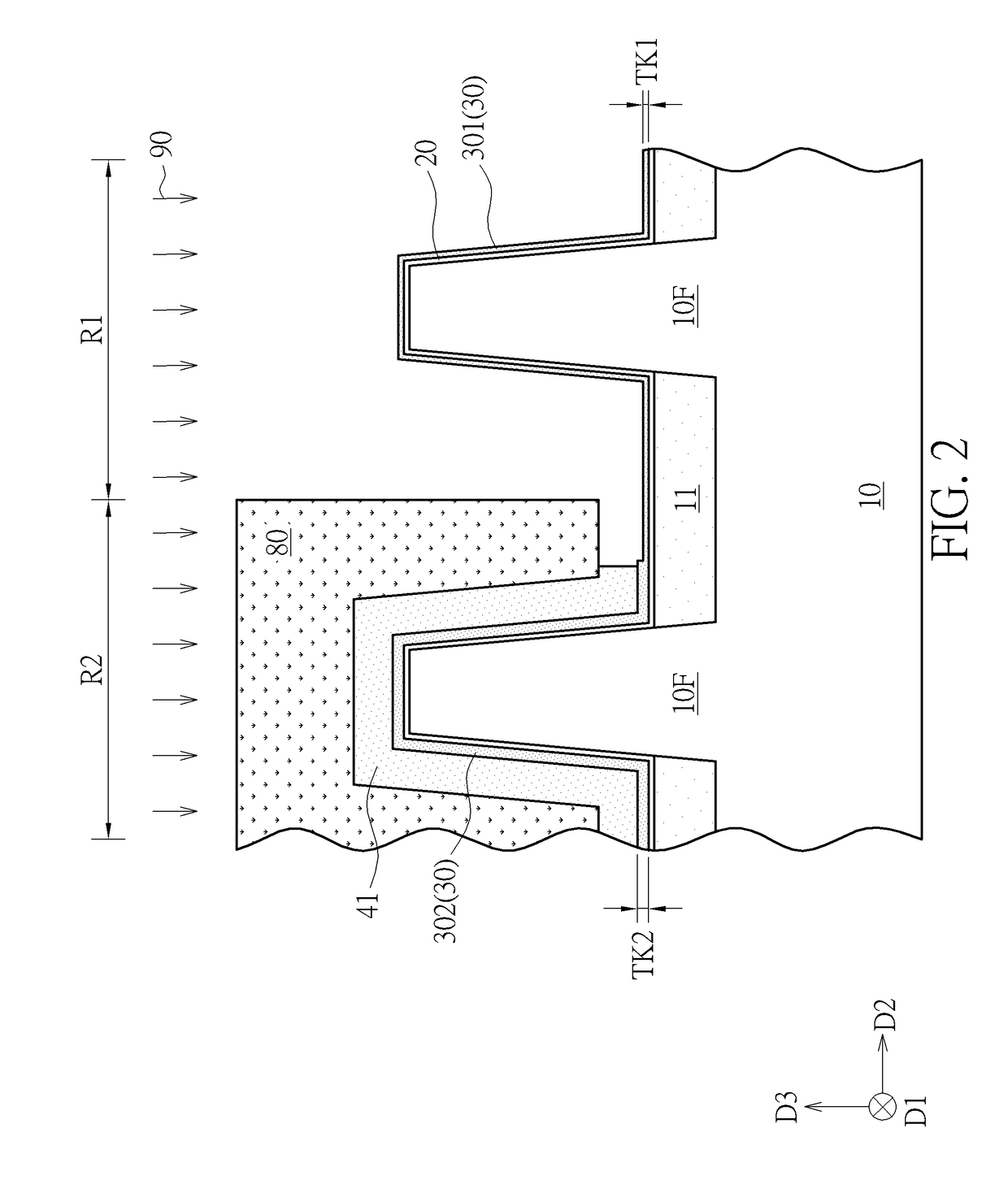

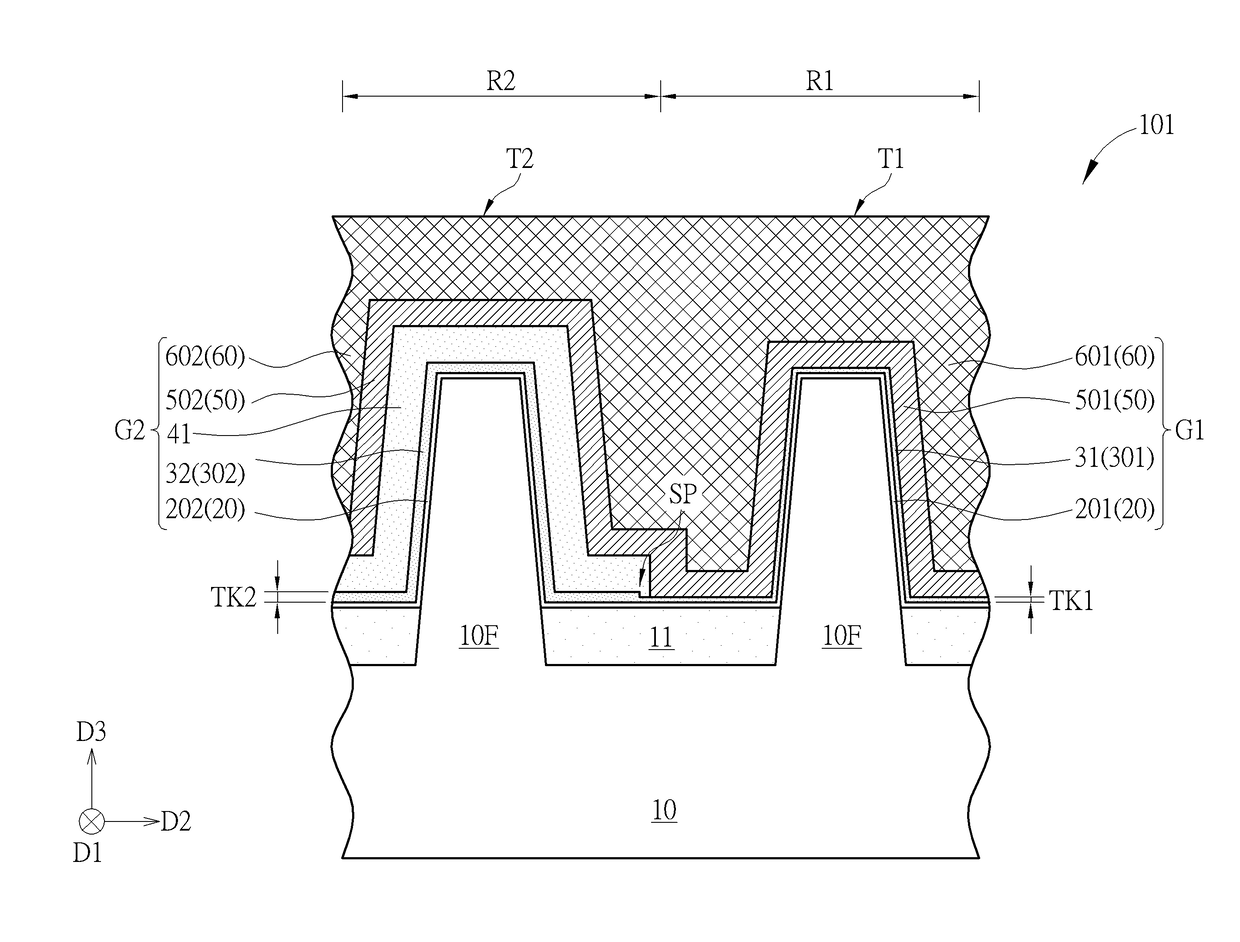

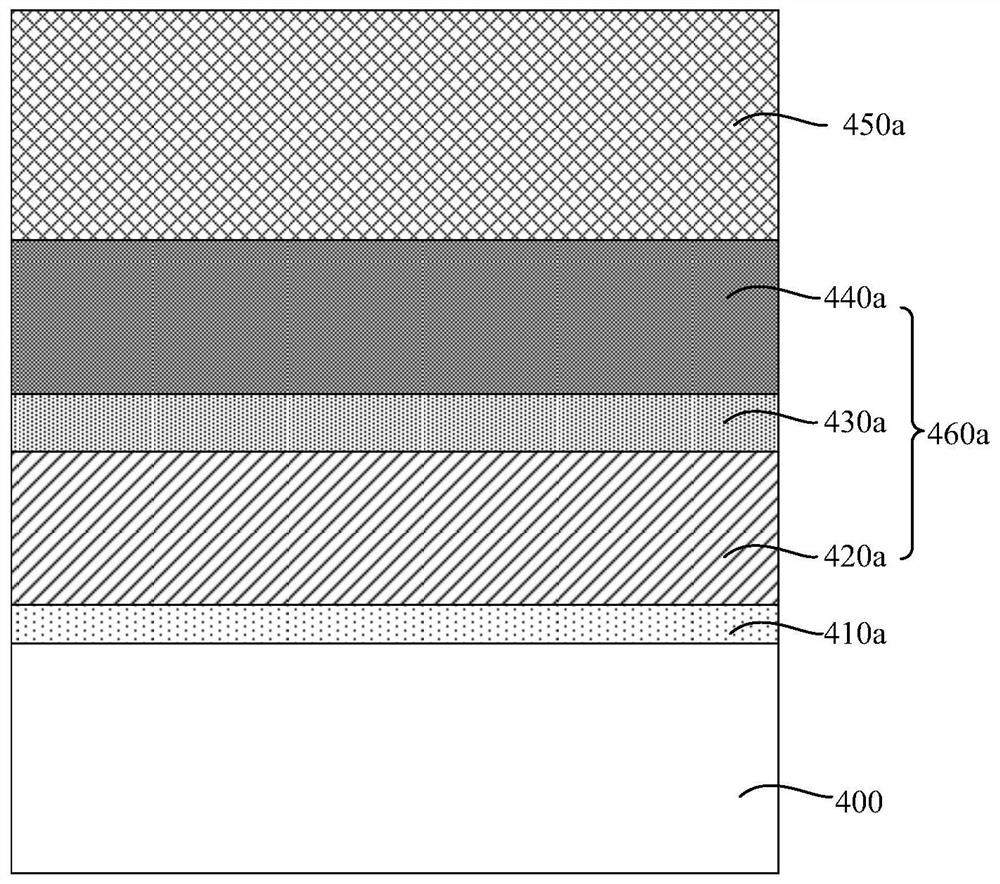

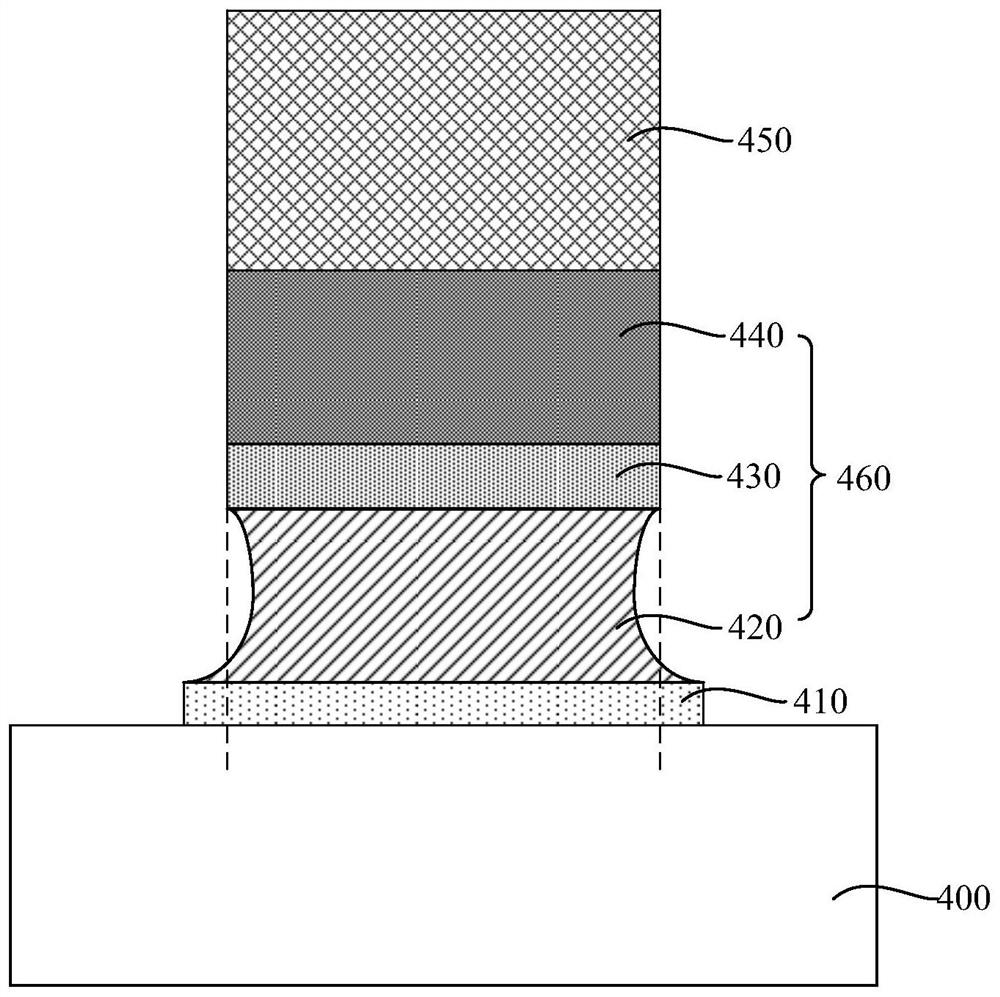

Semiconductor device including barrier layer and manufacturing method thereof

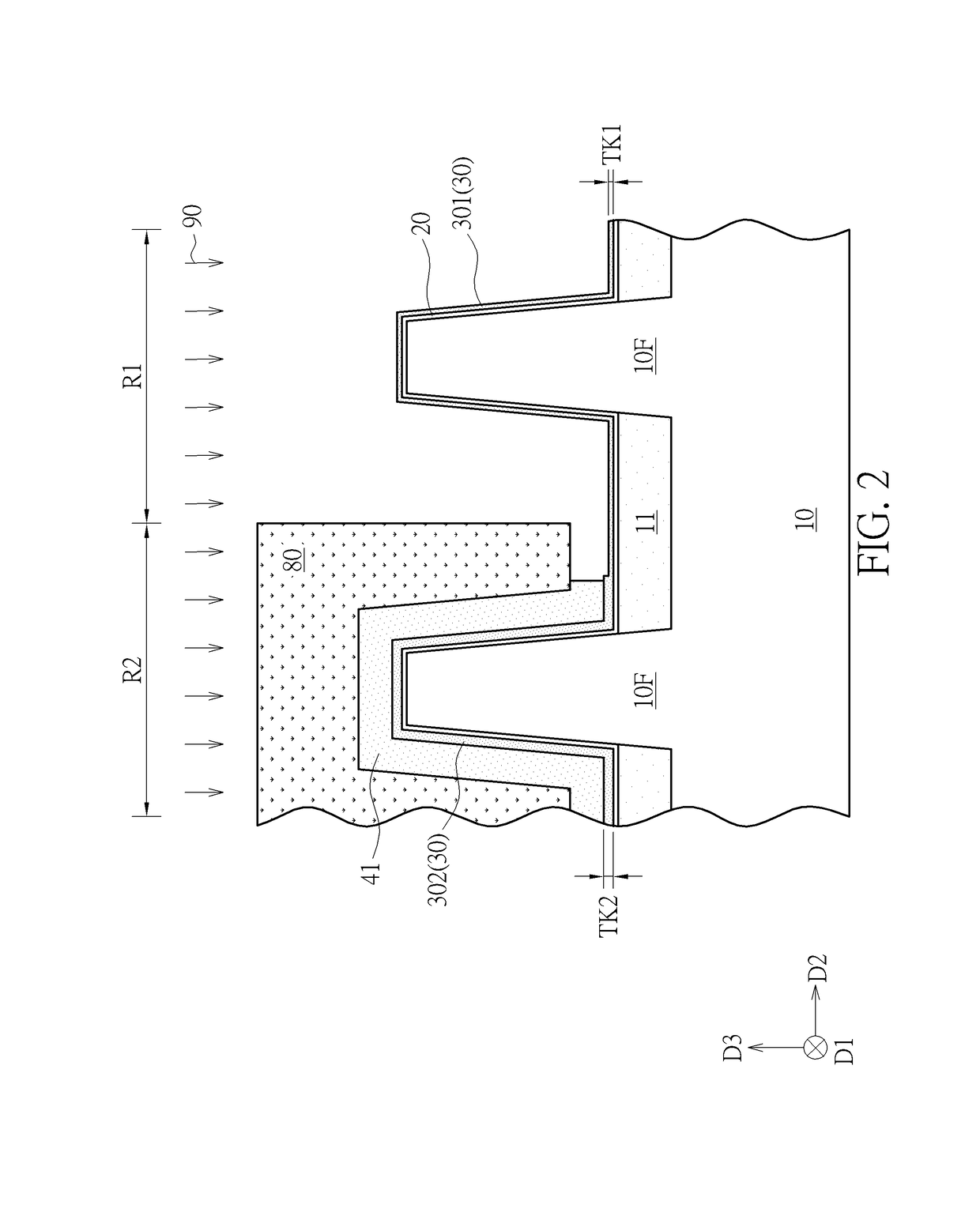

ActiveUS20180138178A1Electrical performance of the semiconductor deviceUnified performanceTransistorSolid-state devicesWork functionElectrical performance

A manufacturing method of a semiconductor device includes the following steps. A barrier layer is formed in a first region and a second region of a semiconductor substrate. The barrier layer formed in the first region is thinned before a step of forming a first work function layer on the barrier layer. The first work function layer formed on the first region is then removed. The process of thinning the barrier layer in the first region and the process of removing the first work function layer in the first region are performed separately for ensuring the coverage of the first work function layer in the second region. The electrical performance of the semiconductor device and the uniformity of the electrical performance of the semiconductor device may be improved accordingly.

Owner:MARLIN SEMICON LTD

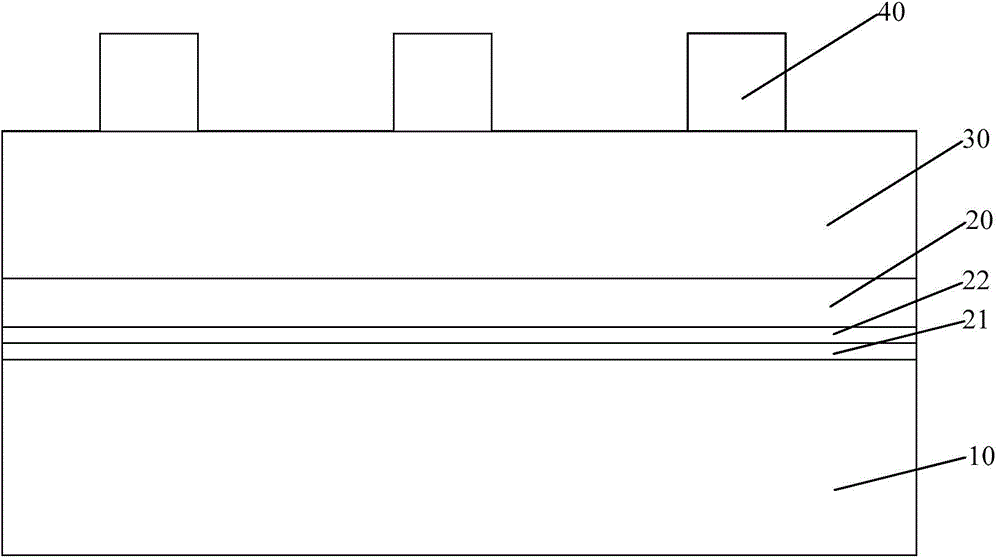

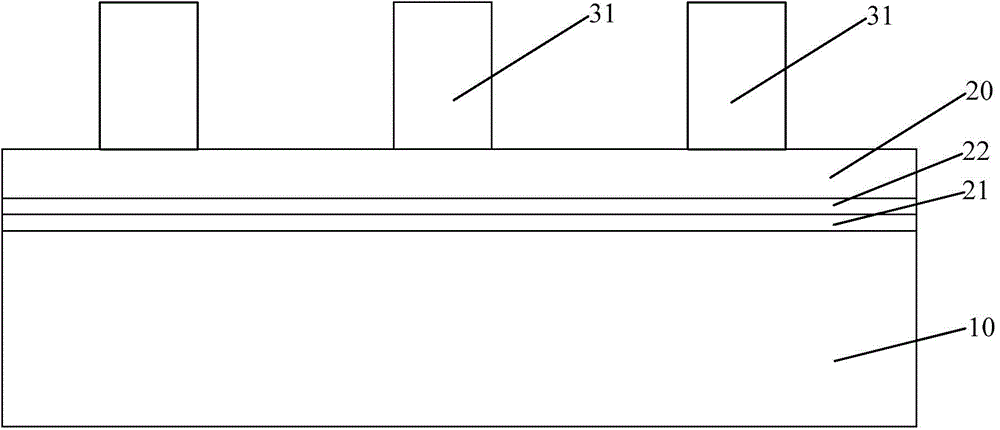

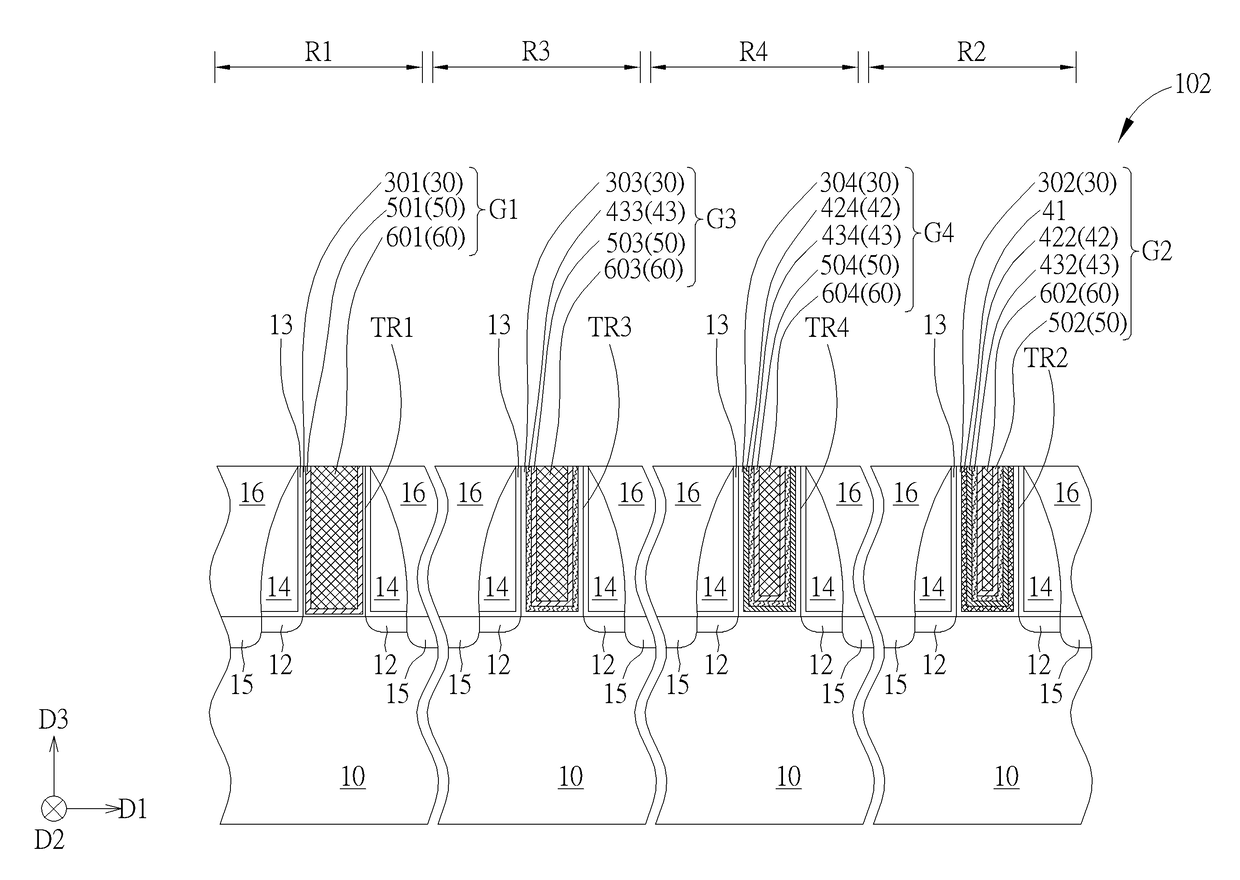

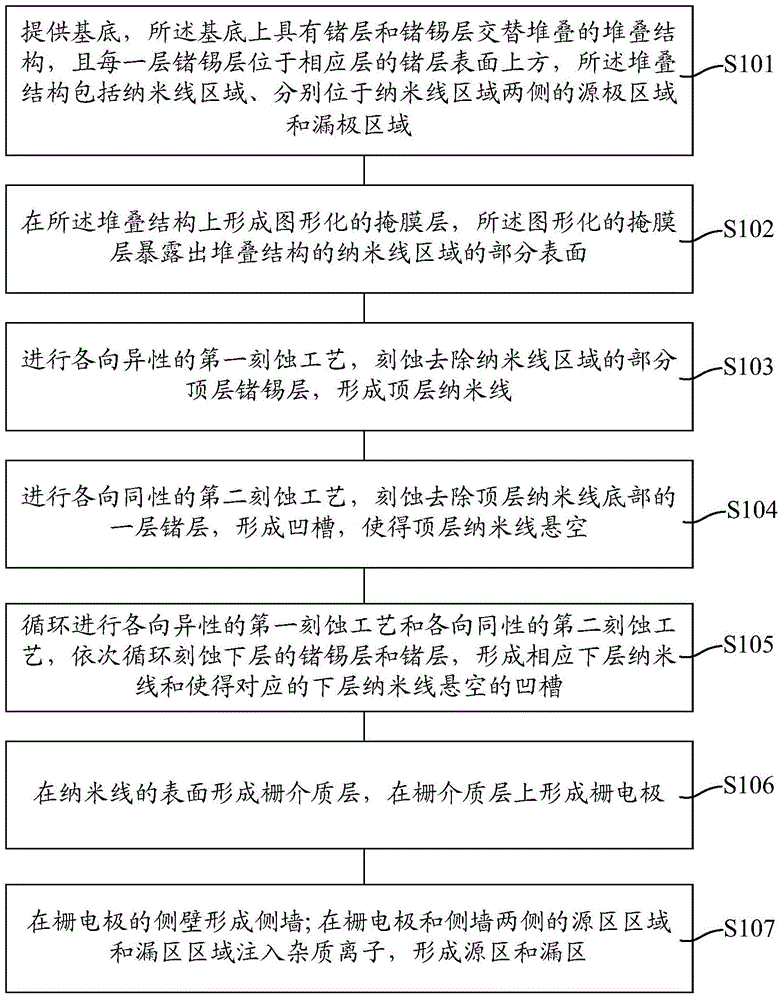

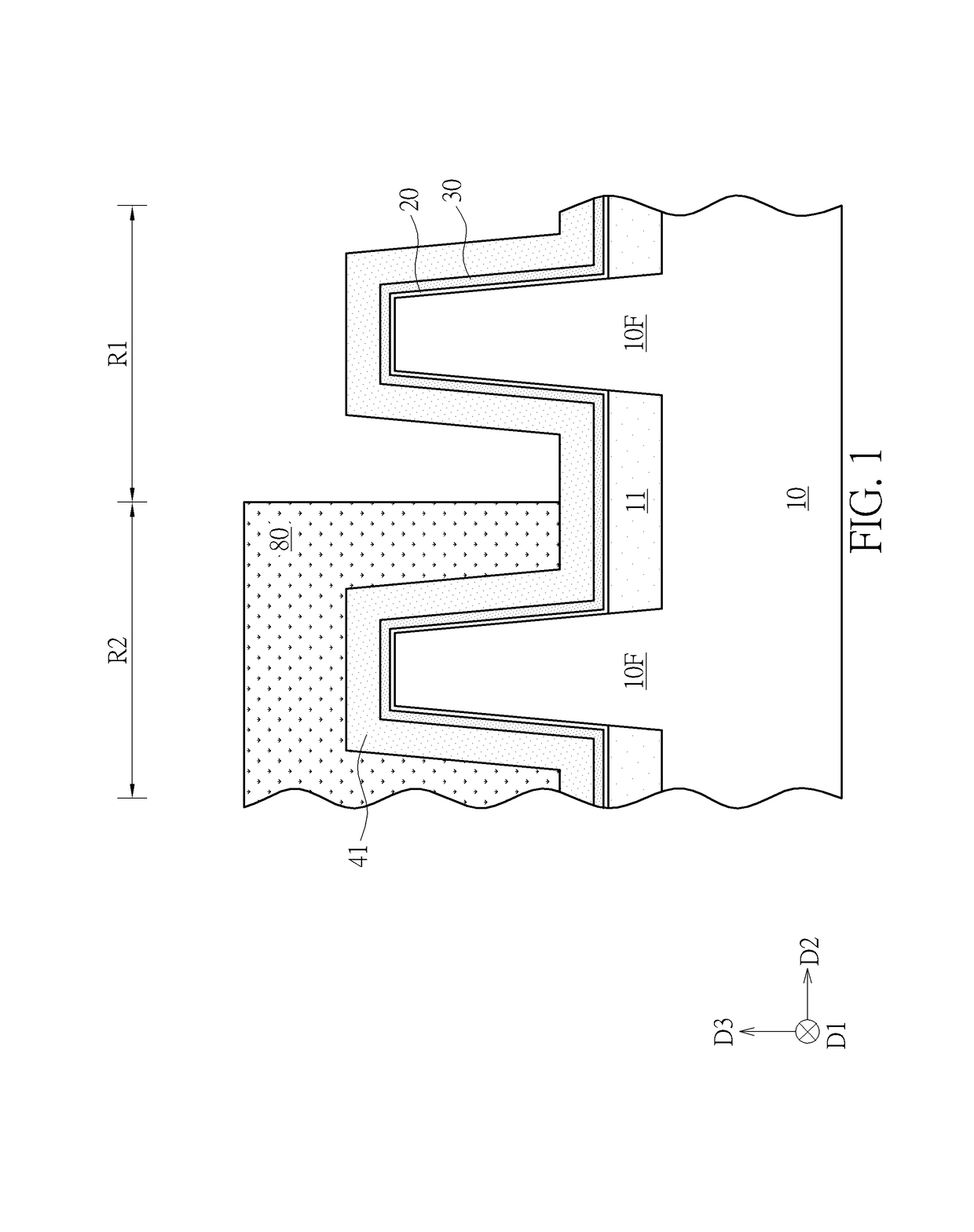

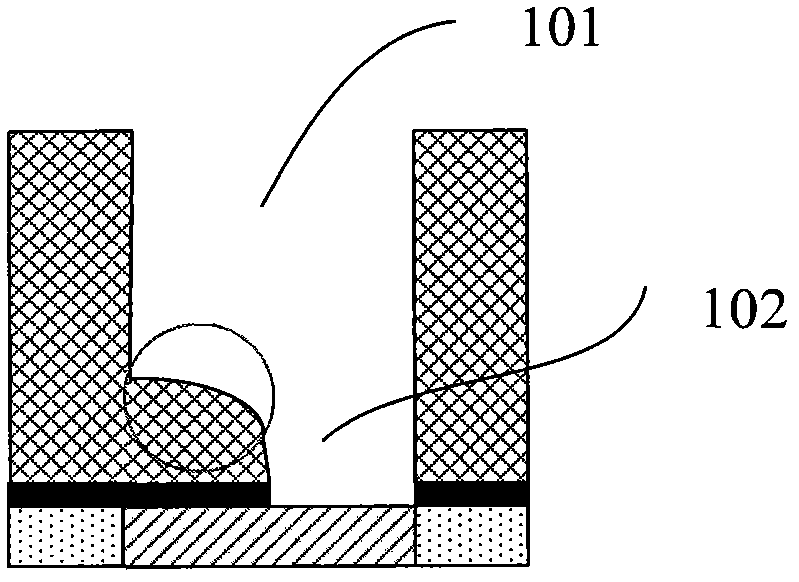

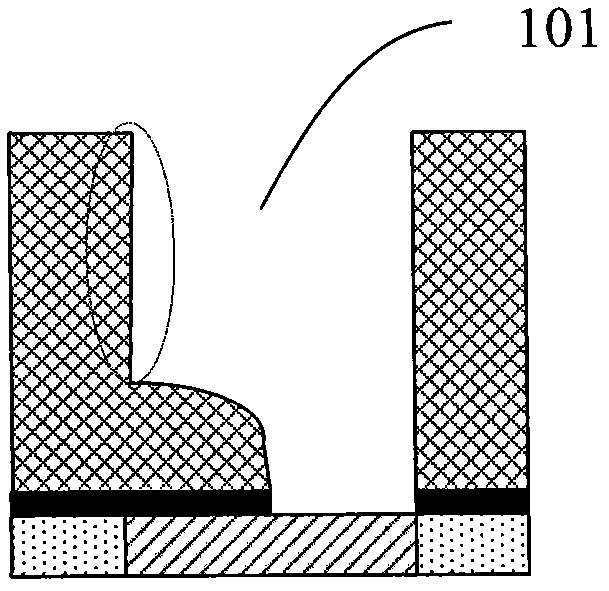

Formation method of nanowire field effect transistor

ActiveCN106158633AImprove performanceDischarge in timeTransistorSemiconductor/solid-state device manufacturingNanowireMicrowave

The invention provides a formation method of a nanowire field effect transistor. The formation method comprises the steps that a substrate is provided, a stack structure formed by germanium layers and germanium tin layers through alternate stacking is formed on the substrate, and the stack structure comprises a nanowire region and a source electrode region and a drain electrode region which are respectively arranged at the two sides of the nanowire region; a patterned mask layer is formed on the stack structure, and a part of surface of the nanowire region of the stack structure is exposed out of the patterned mask layer; the dry etching process is performed, and a part of the top germanium tin layer of the nanowire region is removed through etching so that top nanowires are formed; the microwave etching process is performed, a layer of the germanium layer of the bottom part of the top nanowires is removed through etching so that a groove is formed and the top nanowires are enabled to be suspended; and the anisotropic first etching process and the anisotropic second etching process are cyclically performed, and the lower germanium tin layers and the germanium layers are etched in turn so that the corresponding lower nanowires are formed and the grooves enabling the corresponding lower nanowires to be suspended are formed. According to the method, all layers of the nanowires are maintained to be consistent in size.

Owner:SEMICON MFG INT (SHANGHAI) CORP

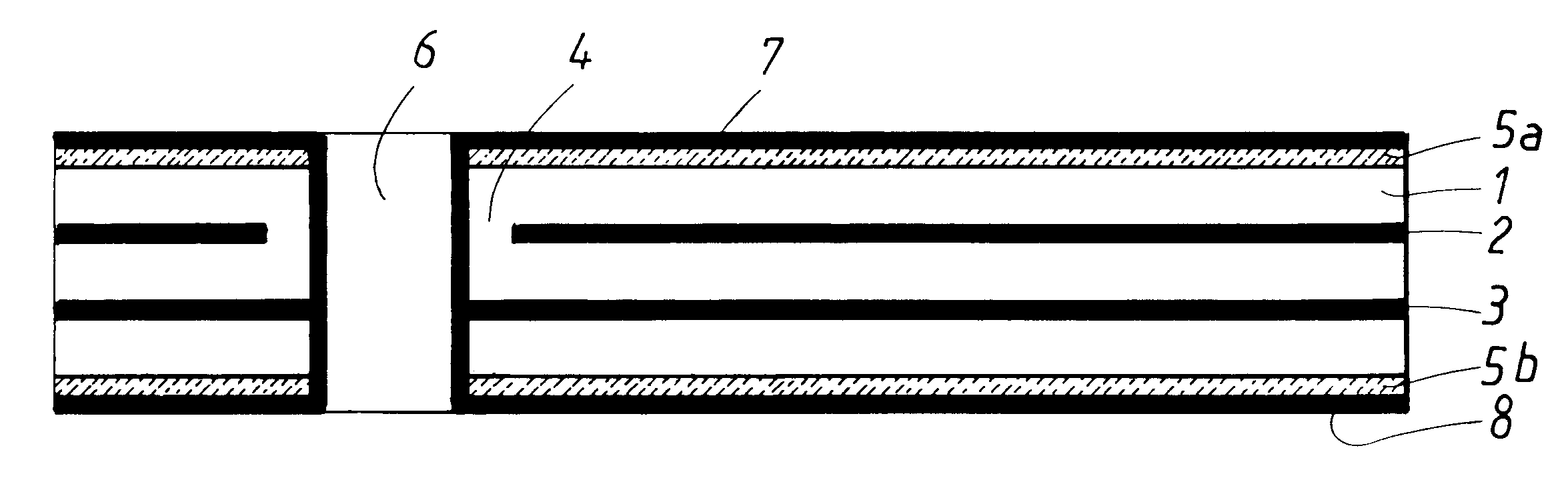

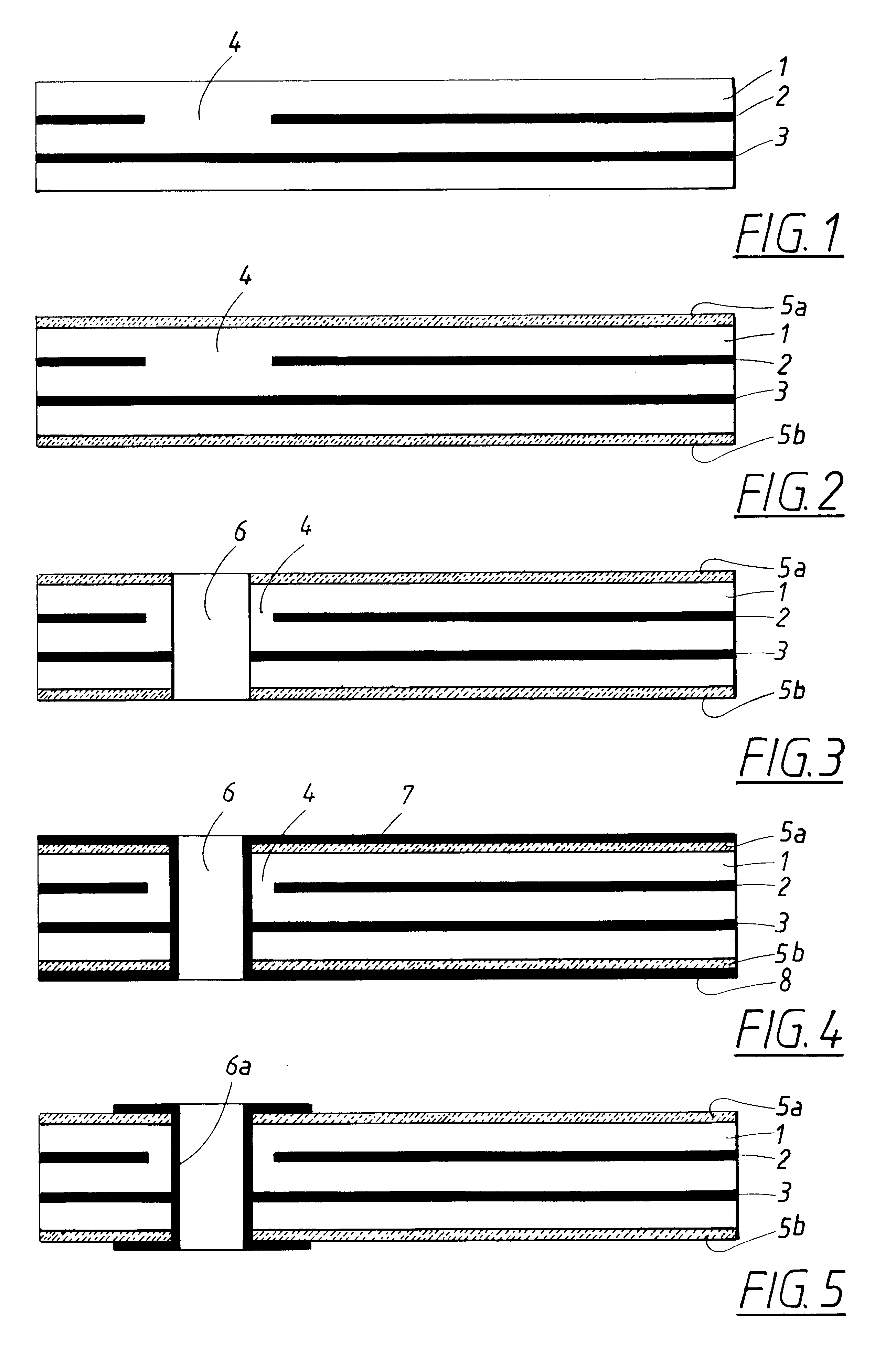

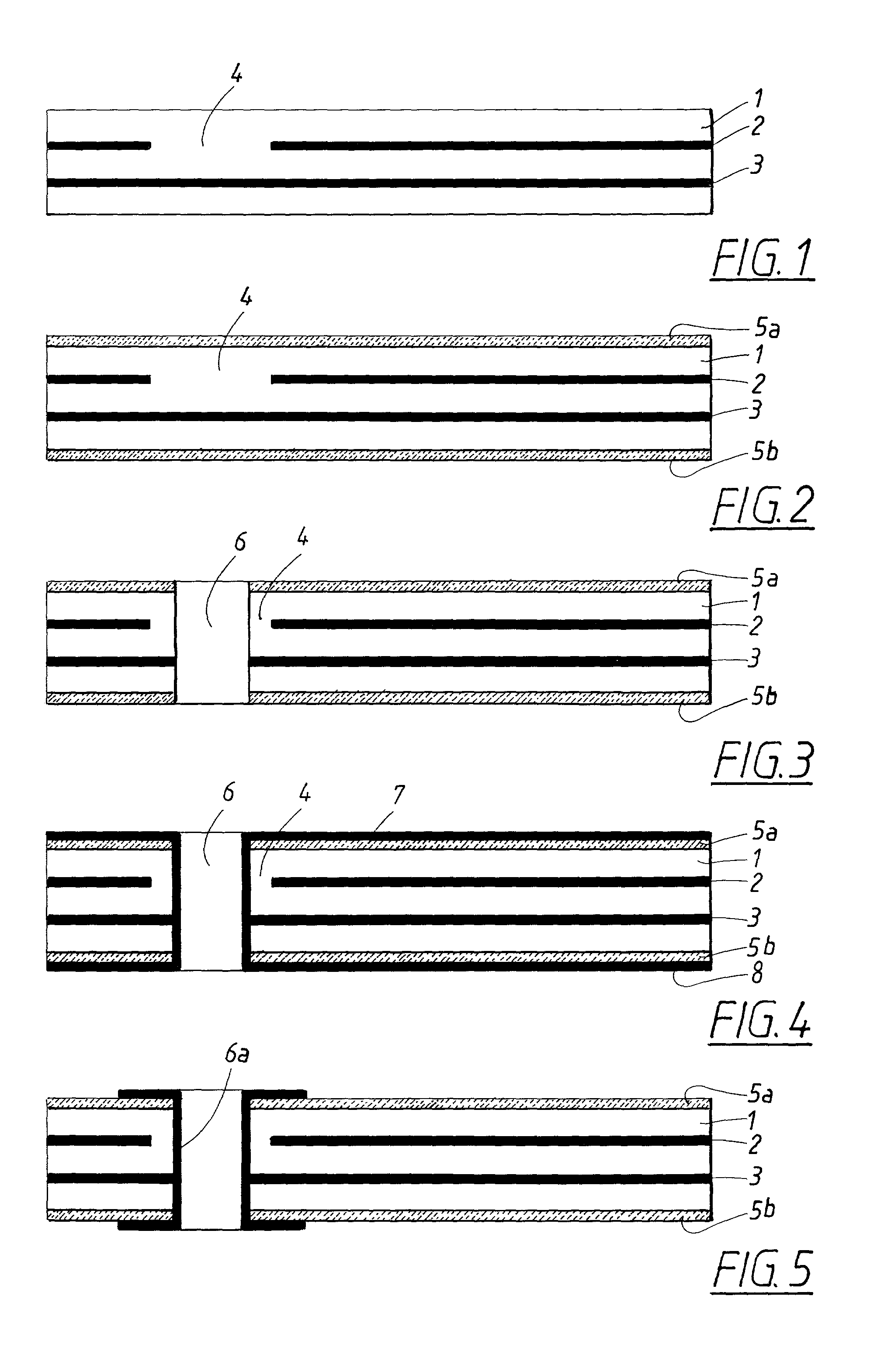

PCB and method for making PCB with thin copper layer

InactiveUS6395378B2Maintain good propertiesImprove adhesionDecorative surface effectsRecord information storageEpoxySurface layer

The invention concerns a PC board with laminates for electrical circuits, the PC board comprising at least one carrier (1) and at least one copper surface layer (7), intended to, after the removal of selected parts, e.g. by etching, function as conductors on the PC board. The new thing is that the carrier at least at some parts has a surface roughness of up to mainly the same size as the thickness of the copper layer and that at least at the above named rough parts is arranged a surface levelling layer (5a,b) between the carrier (1) and the copper layer (7). Further, the invention concerns a method for producing PC board laminate for electrical circuits as above, the laminate comprising a copper layer and a carrier that has a surface roughness of mainly the same size as the thickness of the copper layer. The new thing here is that a layer (5a,b) of liquid epoxy is applied on the one or those surface parts of the carrier which in the end are to carry a copper layer, that the epoxy layer is dried and hardened, and that copper layers (7) are plated on the epoxy layers (5a,b).

Owner:TELEFON AB LM ERICSSON (PUBL)

Method for rapidly determining phase content of double-phase stainless steel by using metallographic dyeing and software

InactiveCN105510105AClear boundariesEasy to identifyPreparing sample for investigationMaterial analysis by optical meansTemperature controlDouble phase

The invention discloses a method for rapidly determining phase content of a double-phase stainless steel by using metallographic dyeing and software. The method comprises the following steps: rough grinding, fine grinding, polishing, etching, and observation under a metallographic microscope. The method is characterized in that an etching agent comprises 10-30g of potassium ferricyanide, 10-30g of sodium hydroxide and 40-100 ml of water in proportion; etching temperature of a sample is controlled at 40-90 DEG C, an etching step is carried out for 2-10 minutes, the sample can be taken out when the sample presents orange color; structure observation can be carried out by the metallographic microscope configured with a camera, an image is collected by an acquisition system; a color identification graph for a quantitative analysis of ferrite can be obtained by using metallographic examination analysis software, and finally, ferrite phase area percentage can be measured. According to the method, phase structures in the double-phase stainless steel present different colors, edge is clear and is easily identified; qualitative and quantitative analysis can be carried out on each phase structure, accuracy of quantification result is high; etching time is short, contrast ratio is large, and operation is simple.

Owner:SHANDONG TAISHAN STEEL GROUP

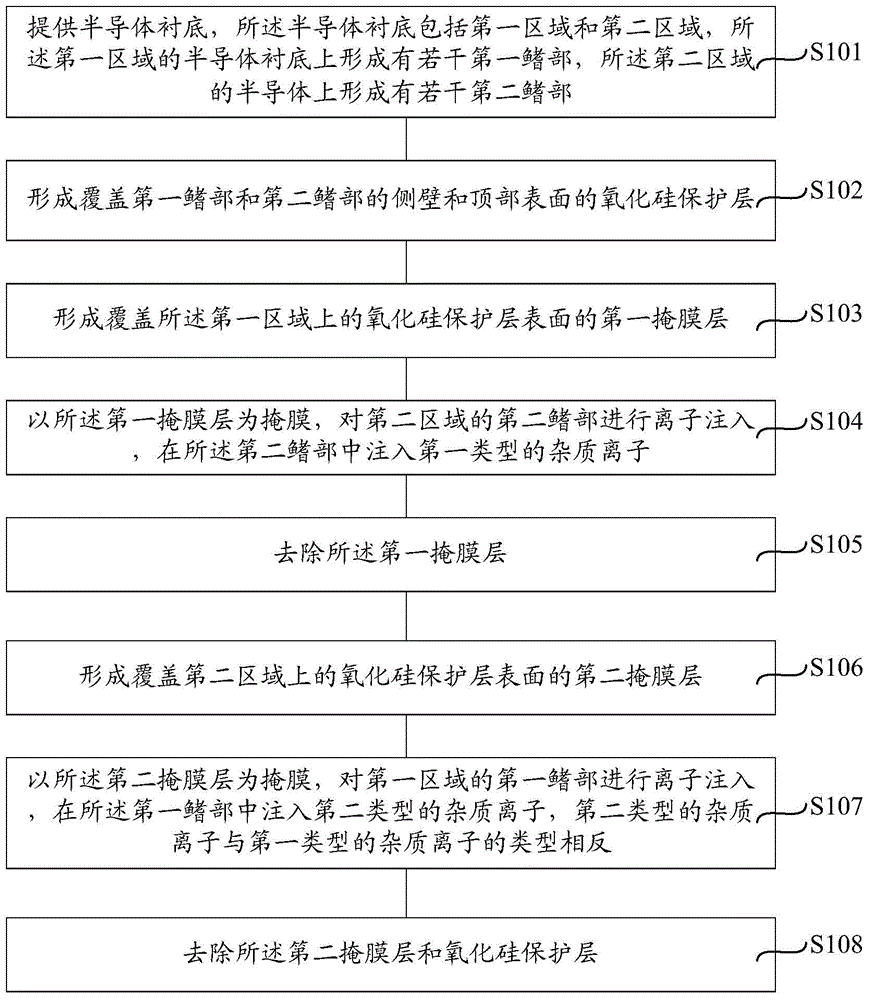

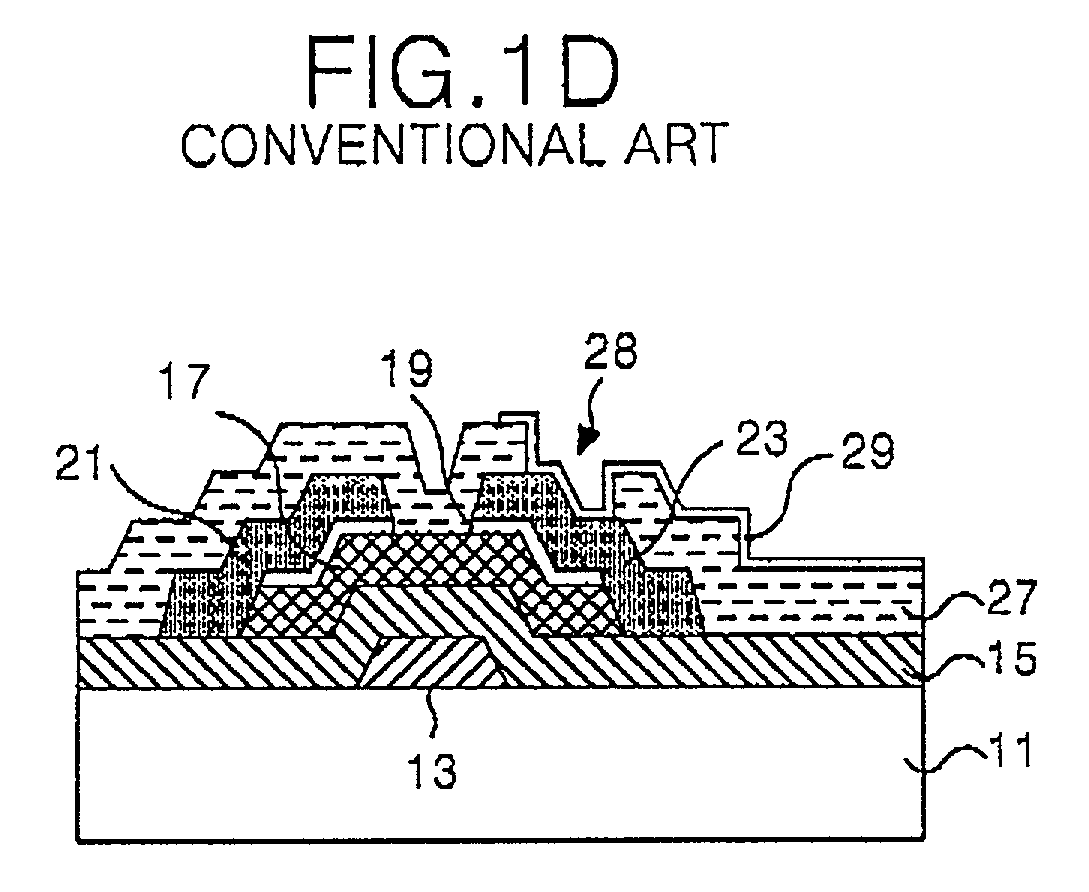

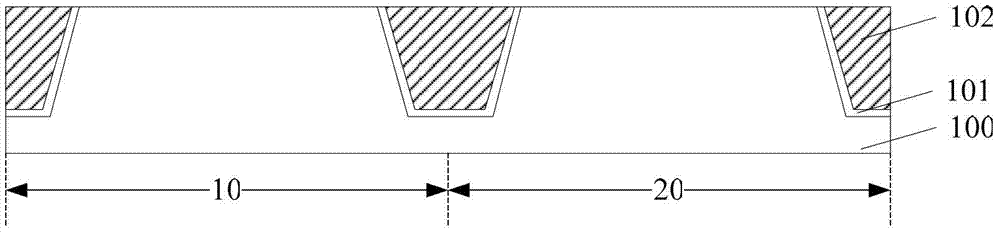

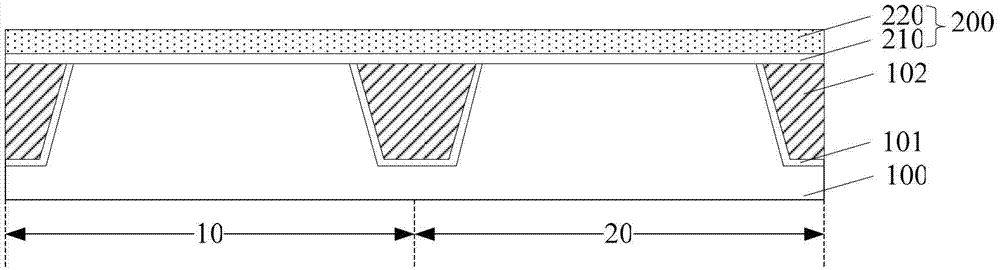

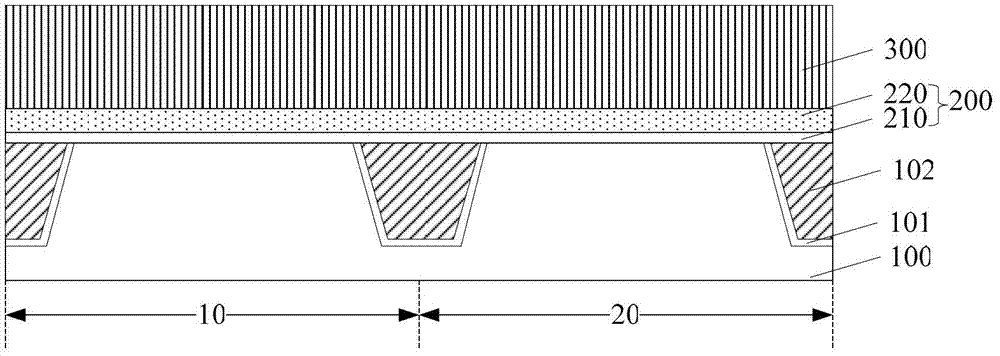

Forming method of transistor

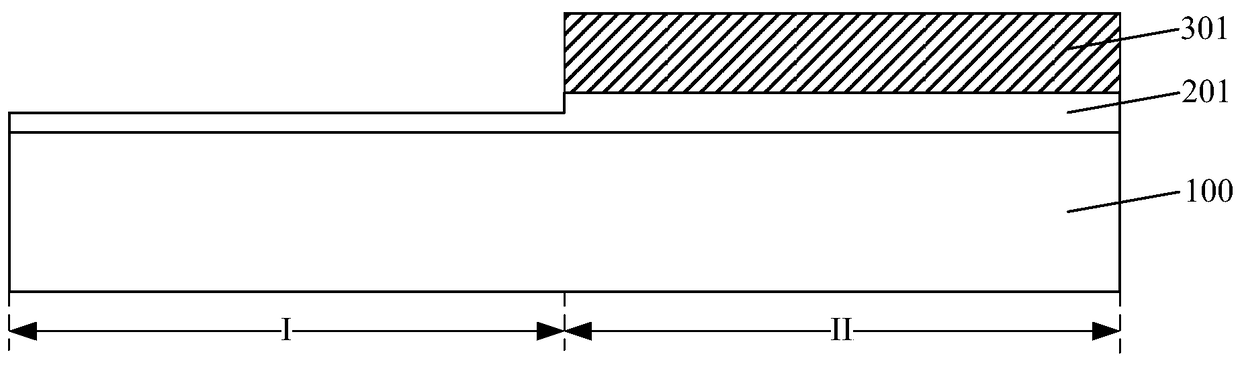

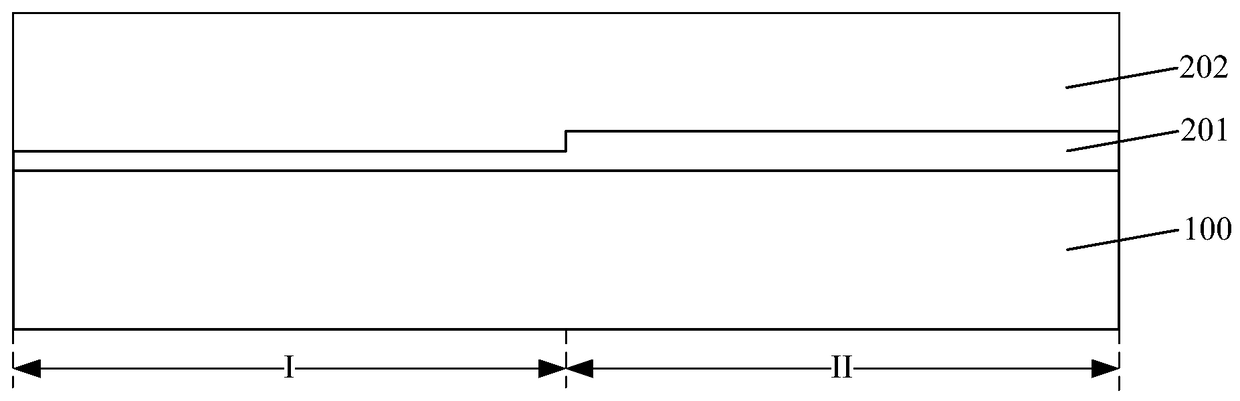

ActiveCN104253047AThe process steps are simpleShort etching timeSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention relates to a forming method of a transistor. The forming method of the transistor includes the following steps that: a semiconductor substrate is provided, wherein the semiconductor substrate includes a first region and a second region; a dummy gate dielectric material layer is formed on the surface of the semiconductor substrate, wherein the dummy gate dielectric material layer includes a first insulating material layer and a second insulating material layer; a dummy gate and a second gate are formed; the dummy gate dielectric material layer is etched with the dummy gate and the second gate adopted as a mask, so that a dummy gate dielectric layer and a second gate dielectric layer are formed; first source / drain areas are formed in the first region, and second source / drain areas are formed in the second region; a dielectric layer is formed on the surface of the semiconductor substrate, and the surface of the dielectric layer is flush with the surface of the dummy gate; and the second insulating material layer in the dummy gate dielectric material layer is removed through adopting a dry etching process, and the first insulating material layer in the dummy gate dielectric material layer is removed through adopting a wet etching process, and therefore, a groove can be formed; and a first gate structure is formed in the groove. With the forming method of the transistor adopted, steps can be decreased, and the performance of the transistor can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device including barrier layer and manufacturing method thereof

ActiveUS9972623B1Electrical performance of the semiconductor deviceUnified performanceTransistorSolid-state devicesWork functionElectrical performance

A manufacturing method of a semiconductor device includes the following steps. A barrier layer is formed in a first region and a second region of a semiconductor substrate. The barrier layer formed in the first region is thinned before a step of forming a first work function layer on the barrier layer. The first work function layer formed on the first region is then removed. The process of thinning the barrier layer in the first region and the process of removing the first work function layer in the first region are performed separately for ensuring the coverage of the first work function layer in the second region. The electrical performance of the semiconductor device and the uniformity of the electrical performance of the semiconductor device may be improved accordingly.

Owner:MARLIN SEMICON LTD

Manufacturing method of ultra-precision circuit

ActiveCN111050484AAvoid the line thinning problem when the side erosion arrivesAvoid line thinningConductive material chemical/electrolytical removalMultilayer circuit manufactureEtchingLayer thickness

The invention discloses a manufacturing method of an ultra-precision circuit. The method comprises the following steps that: S1, an outer-layer circuit is manufactured on an outer-layer copper surfaceof a production board through a negative film process, and it is ensured that the thickness of the outer-layer copper surface is smaller than a circuit copper layer thickness required by design; S2,a film is pasted on the production board through a positive film process, and exposing and developing are performed sequentially, so that an outer-layer circuit pattern is formed, and the outer-layercircuit manufactured in the step S1 is exposed; S3, the copper layer thickness of the outer-layer circuit on the production board is made to be the circuit copper layer thickness required by design through pattern electroplating; and S4, finally, the film is removed. According to the method, the ultra-precise circuit can be manufactured by adopting a mode of combining the negative film process andthe positive film process; and the problem that the ultra-precise circuit cannot be manufactured due to side etching and side electroplating in a conventional circuit process is solved.

Owner:JIANGMEN SUNTAK CIRCUIT TECH

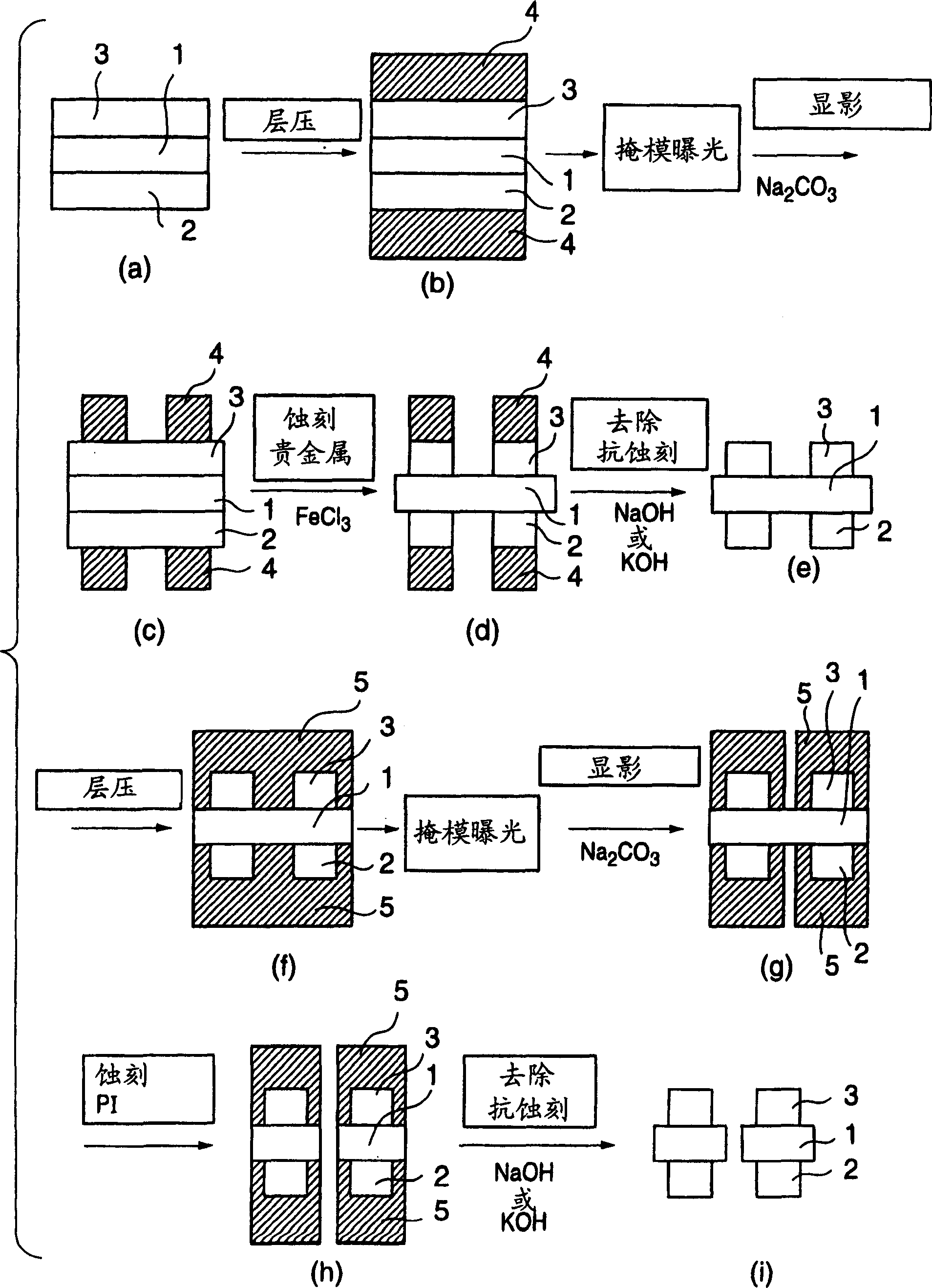

Method for making electronic component using wet corrosion agent

InactiveCN1385756AIncrease the areaShort etching timeDriving/moving recording headsSemiconductor/solid-state device manufacturingEtchingOrganic solvent

The present invention provides a manufacturing method in which a laminate consisting of a conductive inorganic layer-insulating layer-conductive inorganic layer or an insulating layer of a laminate consisting of a conductive inorganic layer-insulating layer is wet-etched. When manufacturing electronic parts, the cost is low, and there is no need to use organic solvents, which are problematic in waste disposal, to manufacture electronic parts. It relates to a manufacturing method of an electronic component, which conducts electrical conductivity by wet etching a laminate composed of a conductive inorganic layer-insulating layer-conductive inorganic layer or a laminate composed of a conductive inorganic layer-insulating layer. The layout of the inorganic layer is followed by the layout of the insulating layer by wet etching. The insulating layer in the laminated body can be wet-etched, and has a single-layer structure or a laminated structure of more than two insulating unit layers, including using a photosensitive adhesive film to perform layout of the insulating layer through the wet-etching.

Owner:DAI NIPPON PRINTING CO LTD

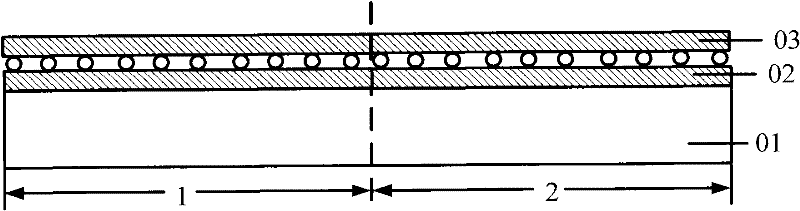

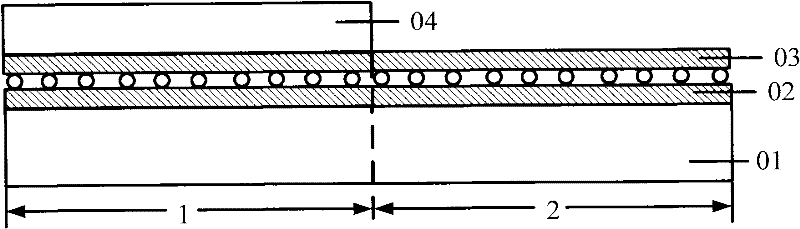

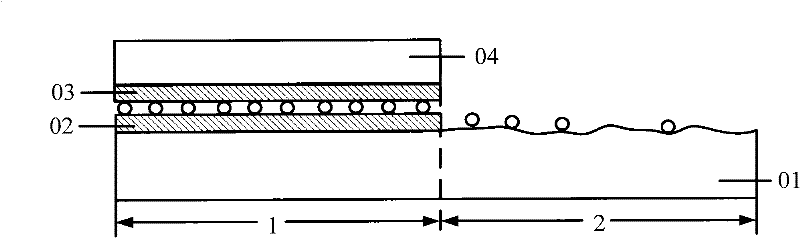

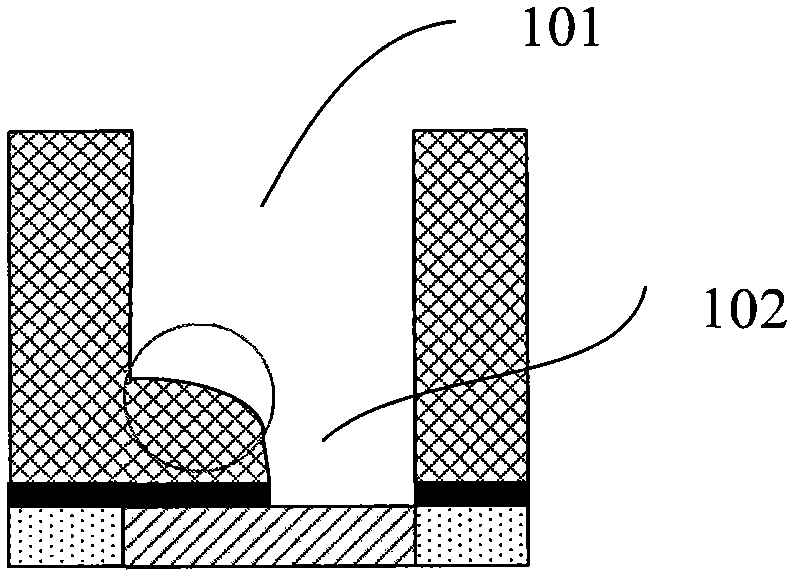

Forming method for memory device

InactiveCN102456629AQuick removalGood removal effectSemiconductor/solid-state device manufacturingIsolation effectEtching rate

The invention provides a forming method for a memory device. The forming method comprises the following steps of: providing a substrate which comprises a memory area and a peripheral area; forming a sacrificial layer on the substrate of the peripheral area; forming a tunneling oxide layer on the substrate of the memory area; sequentially forming nanocrystalline particles and a top oxide layer on the tunneling oxide layer and the sacrificial layer at the same time; and sequentially removing the top oxide layer, the nanocrystalline particles and the sacrificial layer from the peripheral area, wherein the sacrificial layer is loose, porous and easy to remove at relatively higher etching rate, so that the nanocrystalline particles are completely removed within a relatively shorter etching time without damaging an isolation structure between the substrate and an active device, the stability of performance of a circuit in the peripheral area of the memory device is improved, and the problem that isolation effects among the active devices are worsened is solved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

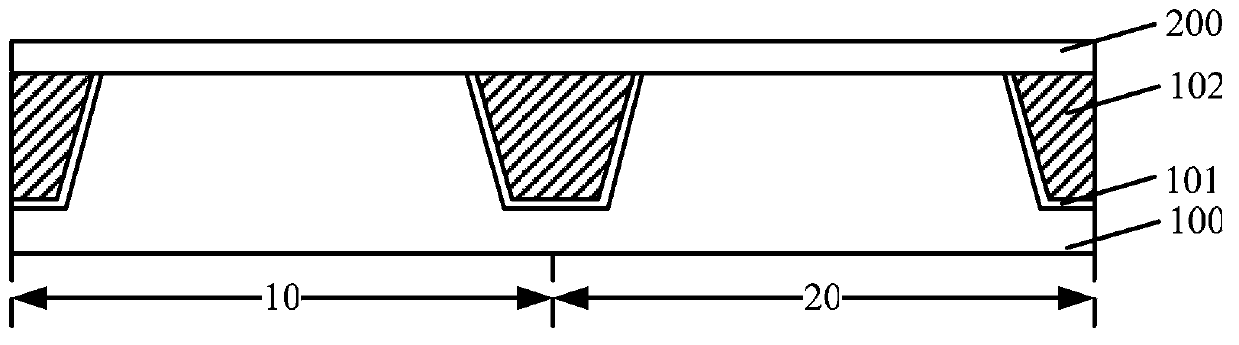

Formation method of transistors

ActiveCN104217935AThe process steps are simpleReduce thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDielectric layer

Disclosed is a formation method of transistors. The formation method includes: providing a semiconductor substrate which comprises a first area and a second area; forming a pseudo gate dielectric material layer on the surface of the semiconductor substrate; forming a pseudo gate on the surface of the pseudo gate dielectric material layer of the first area, and forming a second gate on the surface of the pseudo gate dielectric material layer of the second area; etching the pseudo gate dielectric material layer and forming pseudo gate dielectric layers located under the pseudo gate and a second gate dielectric layer under the second gate; forming a first source / drain region in the first area, and forming a second source / drain region in the second area; forming an interlayer dielectric layer on the surface of the semiconductor substrate; removing the pseudo gate and the pseudo gate dielectric layers to form a groove. The method for removing the pseudo gate dielectric layer includes: adopting dry etching to remove part of the pseudo gate dielectric layers in the thickness direction, and adopting wet etching to remove the rest pseudo gate dielectric layers; forming a first gate structure in the groove. By the formation method, steps can be simplified, and performance of the transistors can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

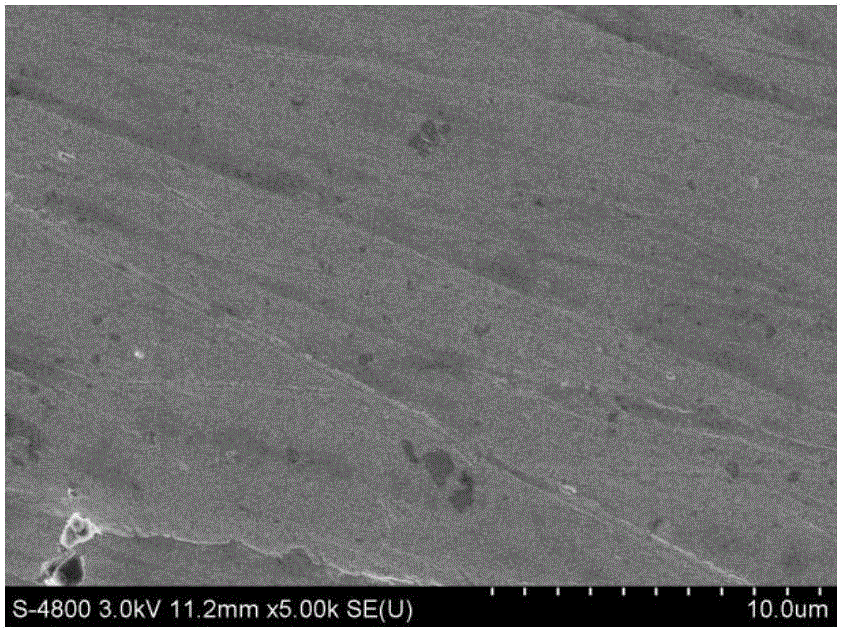

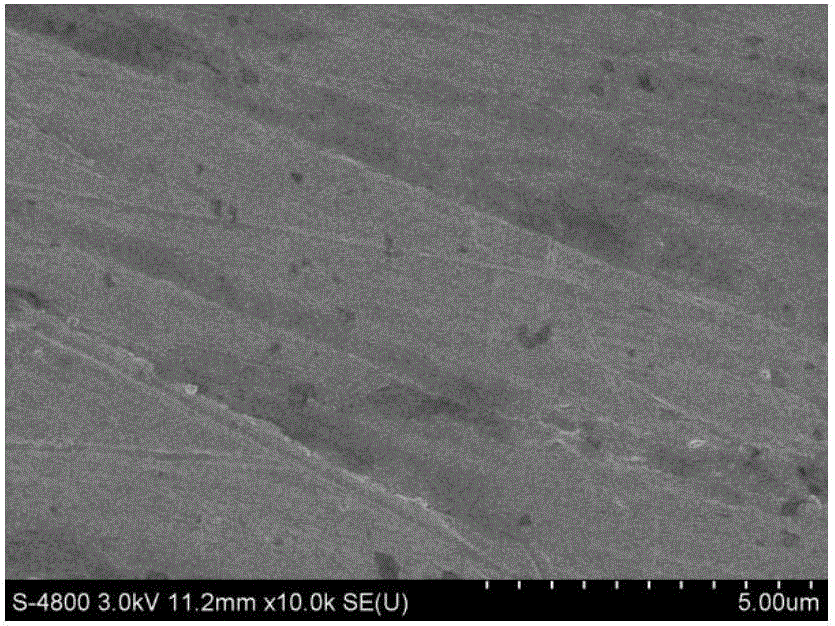

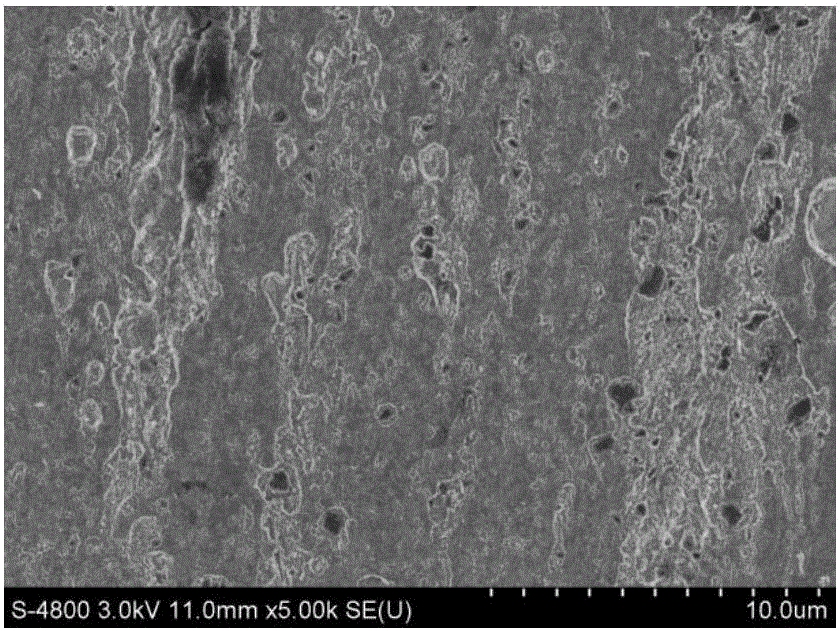

Preparation method of copper-based super-hydrophobic corrosion and scale preventing film for chloride ion corrosion and calcium carbonate scale

InactiveCN105880136AImprove uniformityImprove hydrophobicityPretreated surfacesSpecial surfacesEtchingHydrophobic surfaces

The invention discloses a preparation method of a copper-based super-hydrophobic corrosion and scale preventing film for chloride ion corrosion and calcium carbonate scale. The preparation method comprises the following steps: (1) polishing a copper sheet, carrying out ultrasonic cleaning pretreatment to remove oxides and other dirt on the surface of the copper sheet, and leveling the surface of the copper sheet; (2) putting the pretreated copper sheet into stronger ammonia water to carry out ultrasonic assisted etching, and then calcining to form uniform roughness on a surface layer of the copper sheet; (3) immersing the copper sheet formed with uniform roughness into an ethanol solution of octadecanoic acid to be soaked, then taking out and placing into an oven to carry out heat treatment, and thus forming a super-hydrophobic surface on the surface of the copper sheet. With the adoption of the preparation method disclosed by the invention, the etching time is shorter, the etching is more high-efficient, the uniformity of an emitting surface is enhanced, the price of a selected hydrophobic agent is cheap, and preparation equipment is simple.

Owner:TIANJIN UNIV

Formation method of semiconductor structure

ActiveCN105632923AAvoid injection damageLittle etching damageSemiconductor/solid-state device manufacturingSemiconductor structureAmorphous silicon

The present invention provides a formation method of a semiconductor structure. The formation method of the semiconductor structure comprises: providing a semiconductor substrate which has a protruded fin; forming sacrificial layers which are configured to cover the side wall and the top surface of the fin, wherein the sacrificial layers include first silicon oxide layers located at the side wall and the top surface of the fin, an amorphous silicon layers located at the surfaces of the first silicon oxide layers and second silicon oxide layers located at the surface of the amorphous silicon layers; performing ion implantation of the fin, and injecting foreign ions in the fin to form a well region; and removing the sacrificial layers. The formation method of a semiconductor structure is able to prevent a fin from etching and damaging when sacrificial layers are removed while preventing the fin from ion implantation damaging.

Owner:SEMICON MFG INT (SHANGHAI) CORP

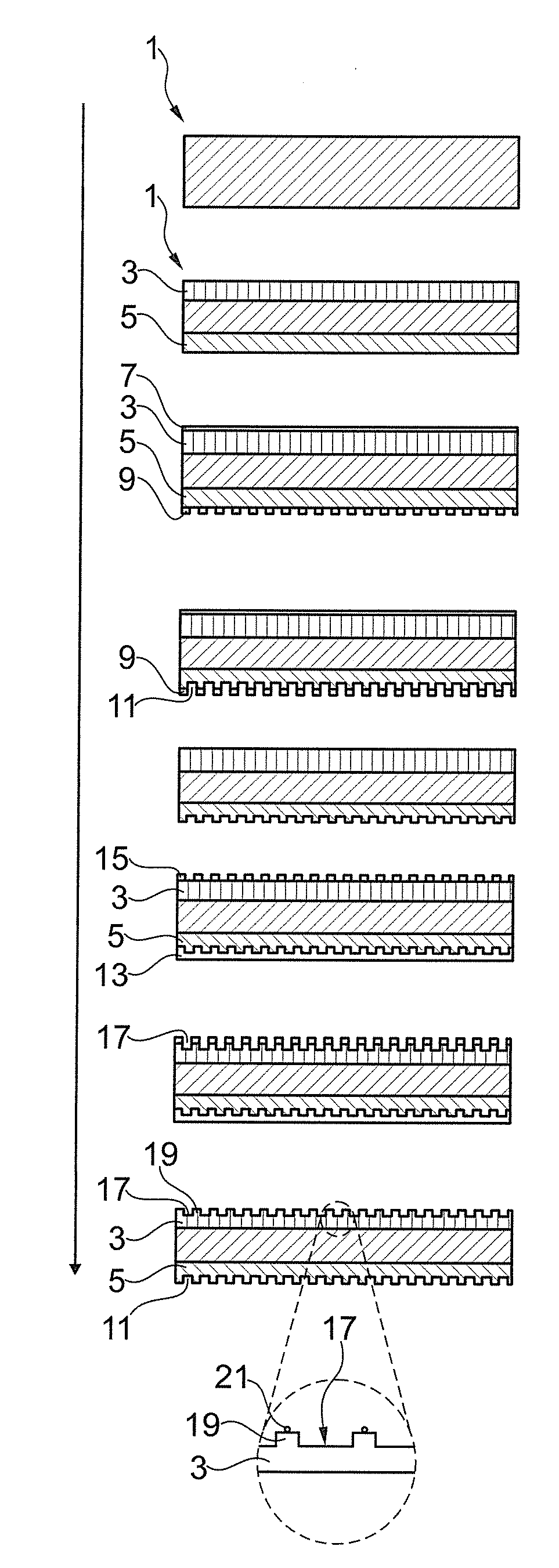

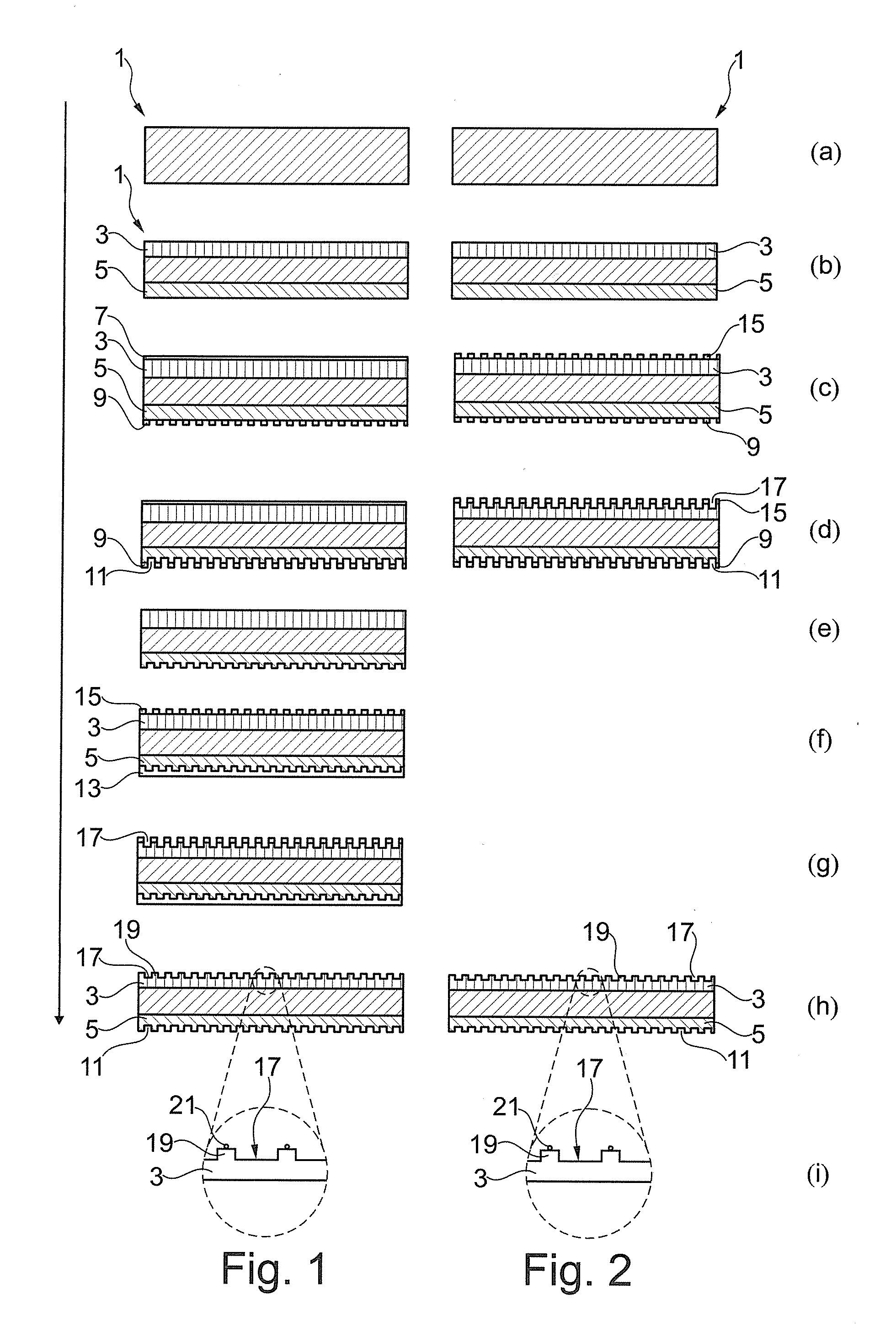

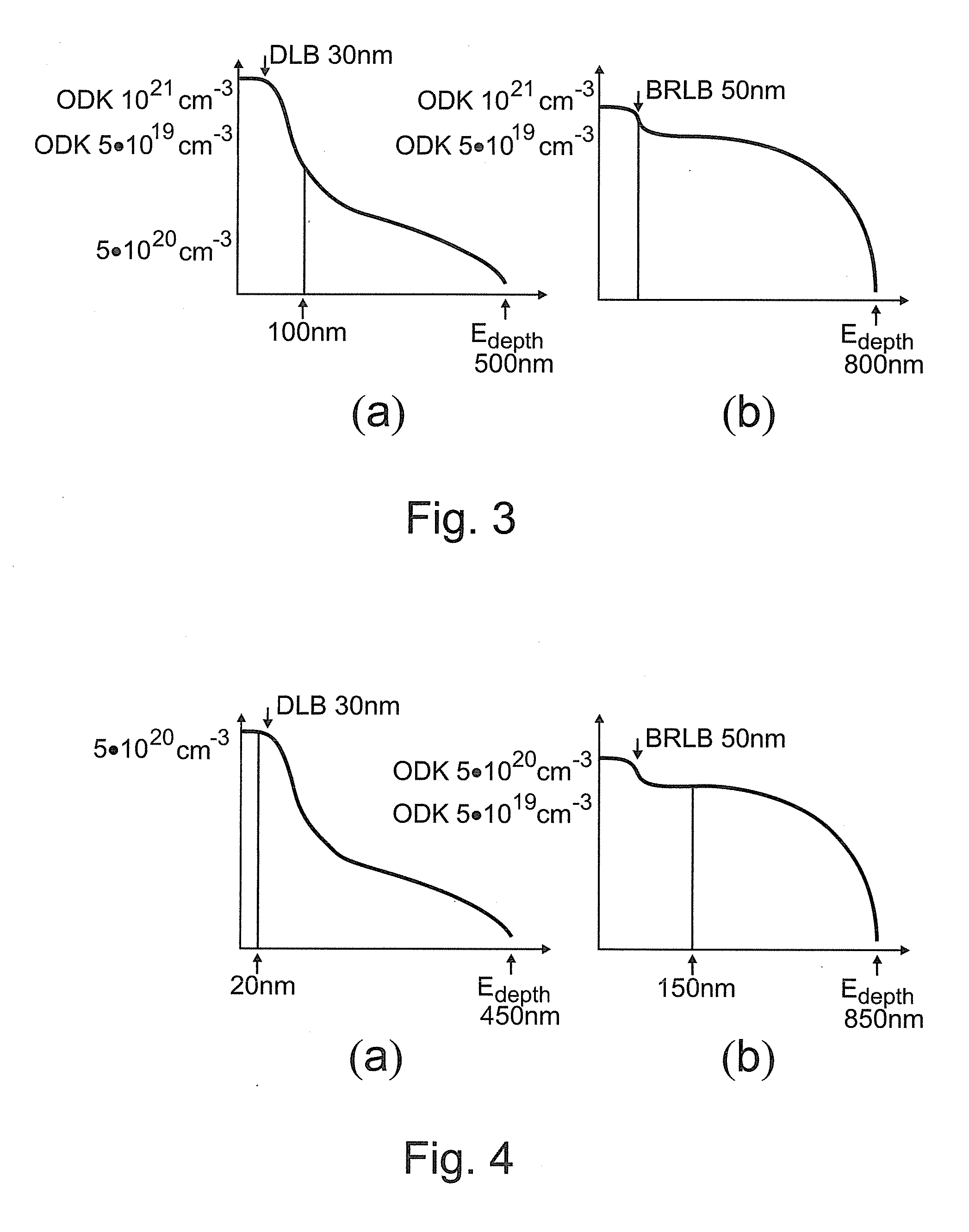

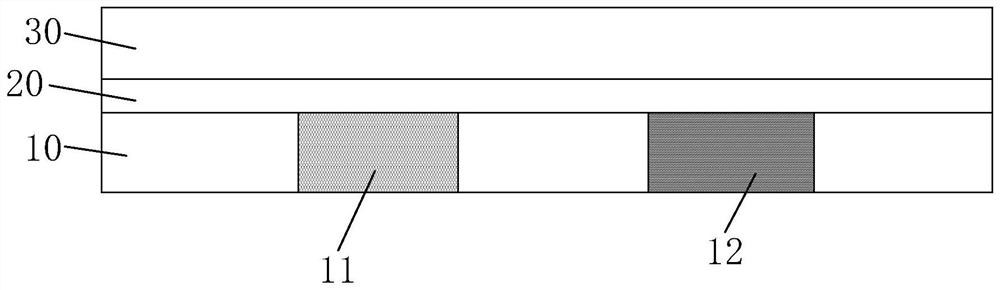

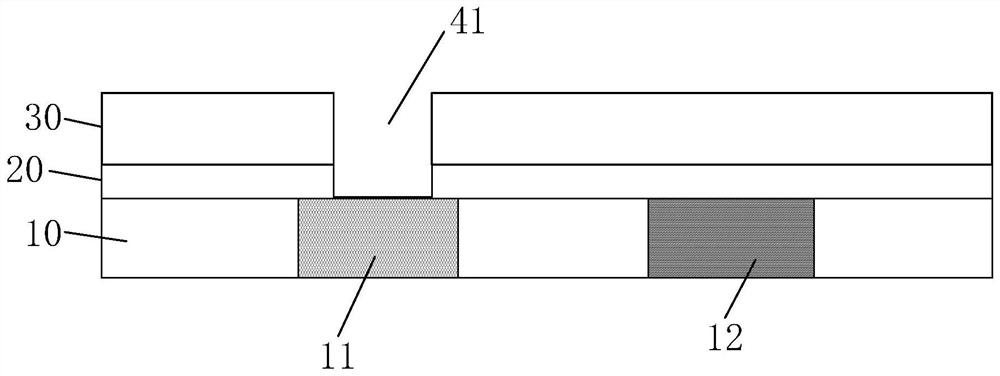

Method for producing solar cells having simultaneously etched-back doped regions

InactiveUS20170018676A1Reduce spendingReduce materialFinal product manufacturePhotovoltaic energy generationEtchingElectrical polarity

A method for producing a solar cell is described, in which a plurality of doped regions are to be etched-back selectively or over their entire surface. Once a semiconductor substrate (1) has been provided, various doped regions (3, 5) are formed in partial regions of a surface of the semiconductor substrate, the various doped regions (3, 5) differing as regards their doping concentration and / or their doping polarity. The various doped regions (3, 5) are then purposively etched-back in order to achieve desired doping profiles, and finally electrical contacts (21) are formed at least at some of the doped regions (3, 5). The etching-back of the various doped regions takes place in a common etching operation in an etching medium. In order that such common etching-back of various doped regions (3, 5) is possible, it is proposed purposively to adjust both properties of the initially unetched doped regions (3, 5) and parameters that influence the etching operation with regard to properties of the desired doping profiles within the etched doped regions.

Owner:UNIV KONSTANZ

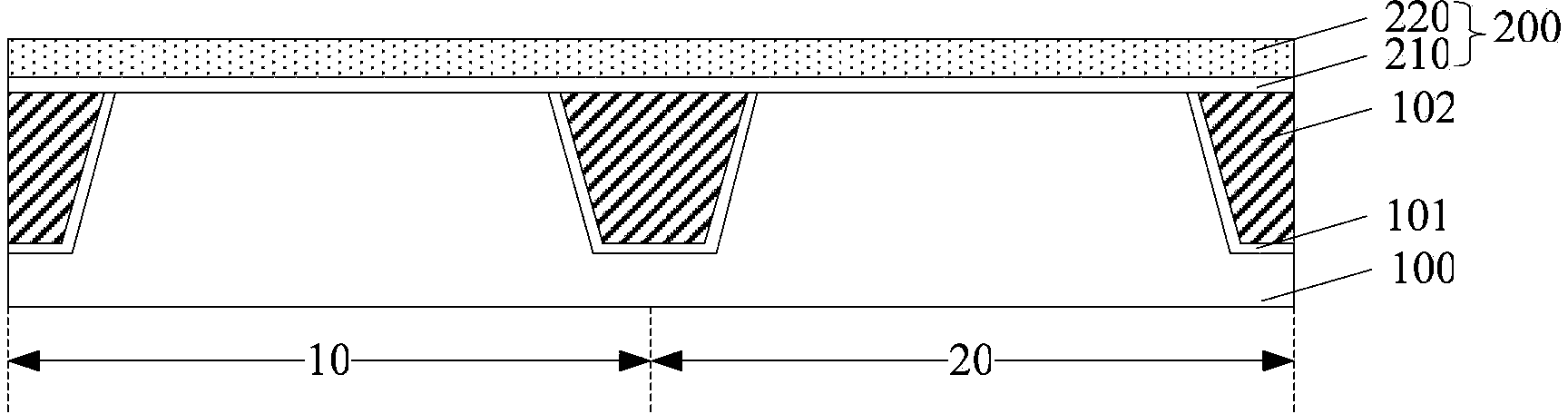

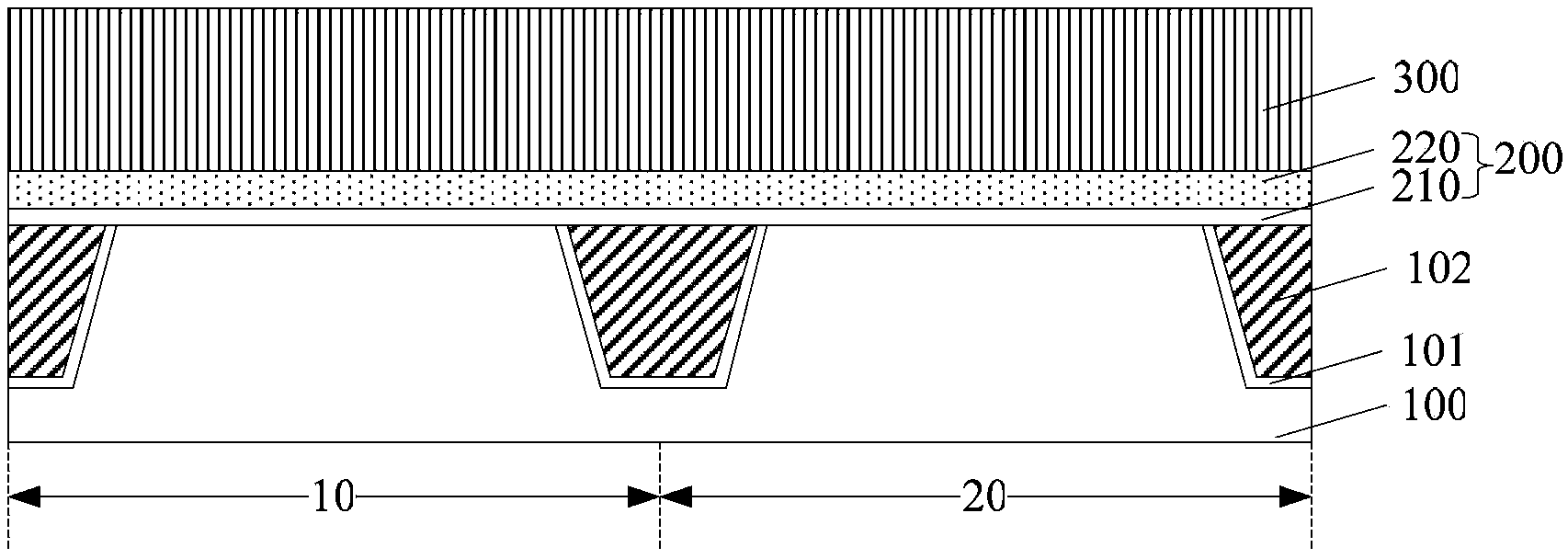

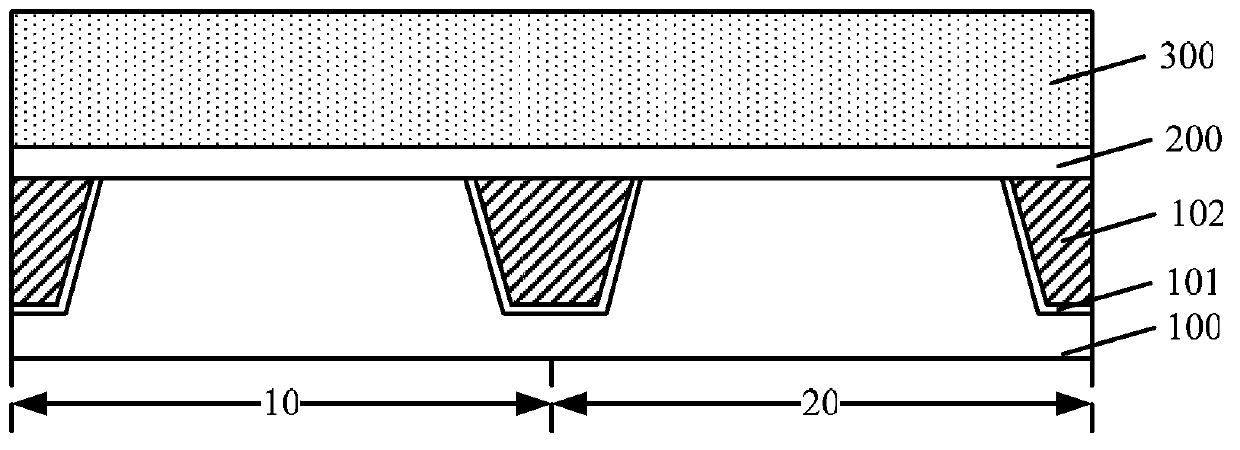

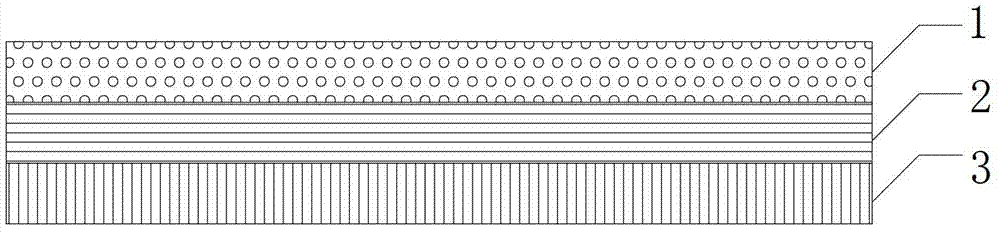

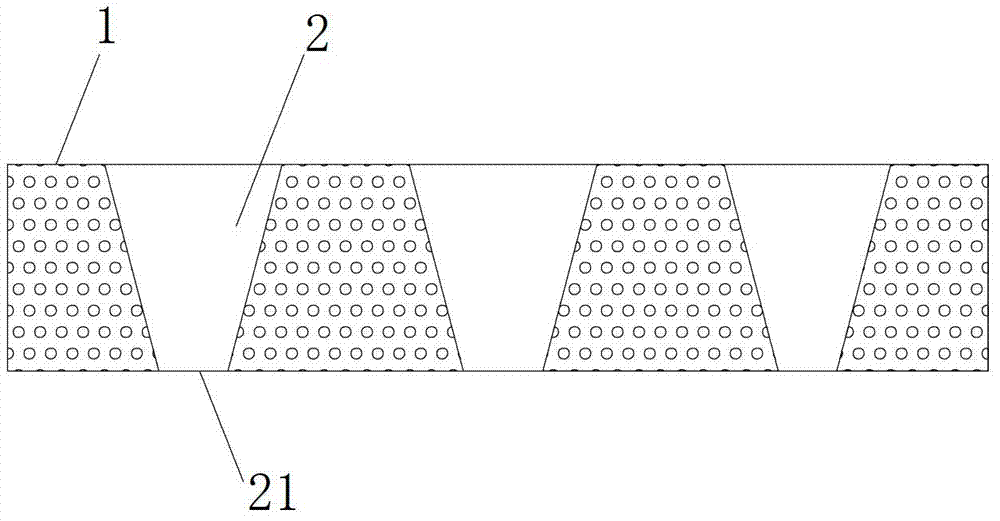

Funnel type lithium battery diaphragm and production method thereof

InactiveCN102760852AUniform thicknessHigh tensile strengthCell component detailsWater layerLithium battery

The invention relates to the field of a lithium battery processing production technology, and in particular relates to a funnel type lithium battery diaphragm and a production method of the diaphragm. The funnel type lithium battery diaphragm has the structure of comprising a base film layer; one side of the base film layer is stuck and connected with a protective film layer capable of resisting etching by a release agent and a glue water layer; and the base film layer is internally and evenly distributed with funnel type micropores. The lithium battery diaphragm produced by the method has the characteristics of being thin in thickness, even in density of the micropores, easy in control of aperture, rapid in production speed, high in production efficiency, high in tensile strength, etc.

Owner:허난구오안일렉트릭머터리얼컴퍼니리미티드

Corrugated and nanoporous microstructures and nanostructures, and methods for synthesizing the same

ActiveUS9176140B2Short etching timeImprove adsorption capacityLiquid surface applicatorsPhysical/chemical process catalystsEtchingPotassium cyanide

Owner:SYRACUSE UNIVERSITY

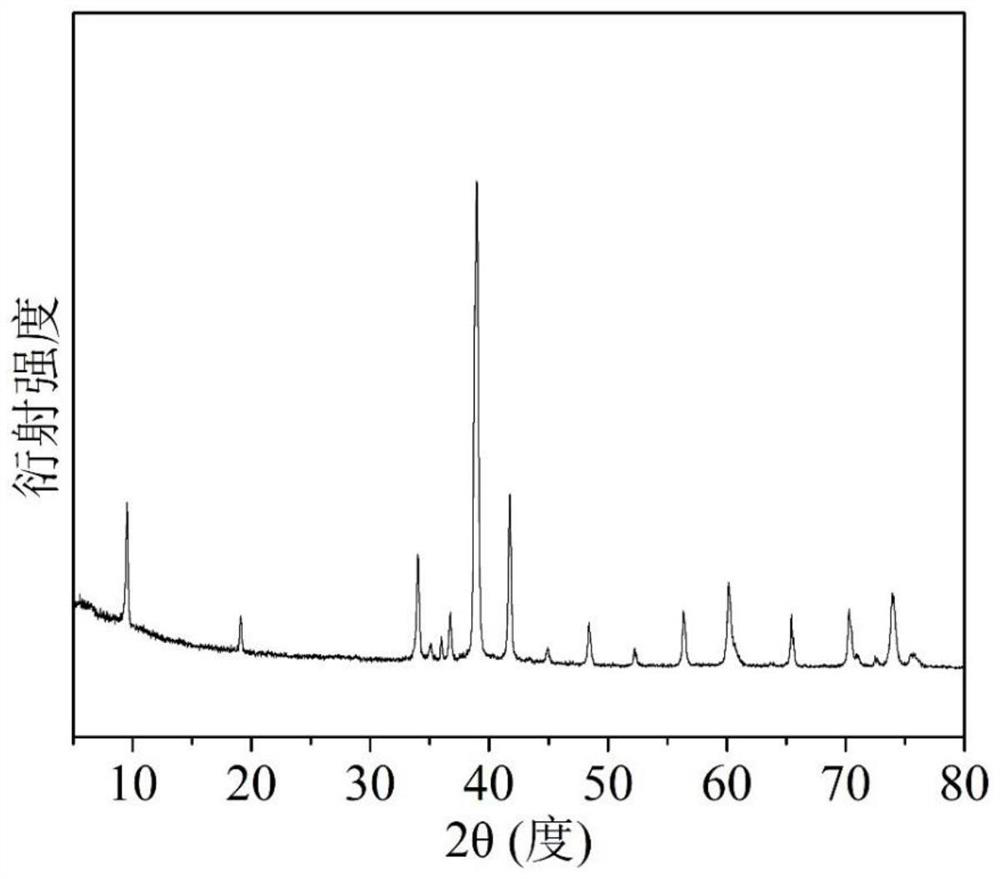

Preparation method and application of double non-noble metal catalyst with high specific surface area and high defects

ActiveCN110935451AHigh catalytic activityGood dispersionCatalyst activation/preparationHydrogen productionAcetic acidO-Phosphoric Acid

The invention relates to a preparation method and application of a double non-noble metal catalyst with high specific surface area and high defects. According to the method, the double non-noble metal(iron, cobalt, nickel, copper or zinc) catalyst is prepared by adopting a liquid phase reduction method, and then etching is performed by adopting a weak acid (acetic acid or phosphoric acid), so that the catalyst has a high specific surface area and high defect sites, more catalytic reaction active sites are generated, and the double non-noble metal catalyst with high activity is prepared. The catalyst is used for catalyzing the hydrolyzing reaction of ammonia borane to release hydrogen, and has excellent performance. The method has the advantages of cheap and accessible raw materials, simple technique and mild conditions, and can realize large-scale production.

Owner:HEBEI UNIV OF TECH

PCB and method for making PCB with thin copper layer

InactiveUS20010008680A1Good linear expansion propertyDecrease linear expansionDecorative surface effectsRecord information storageSurface levelOptoelectronics

The invention concerns a PC board with laminates for electrical circuits, the PC board comprising at least one carrier (1) and at least one copper surface layer (7), intended to, after the removal of selected parts, e.g. by etching, function as conductors on the PC board. The new thing is that the carrier at least at some parts has a surface roughness of up to mainly the same size as the thickness of the copper layer and that at least at the above named rough parts is arranged a surface levelling layer (5a,b) between the carrier (1) and the copper layer (7). Further, the invention concerns a method for producing PC board laminate for electrical circuits as above, the laminate comprising a copper layer and a carrier that has a surface roughness of mainly the same size as the thickness of the copper layer. The new thing here is that a layer (5a,b) of liquid epoxy is applied on the one or those surface parts of the carrier which in the end are to carry a copper layer, that the epoxy layer is dried and hardened, and that copper layers (7) are plated on the epoxy layers (5a,b).

Owner:TELEFON AB LM ERICSSON (PUBL)

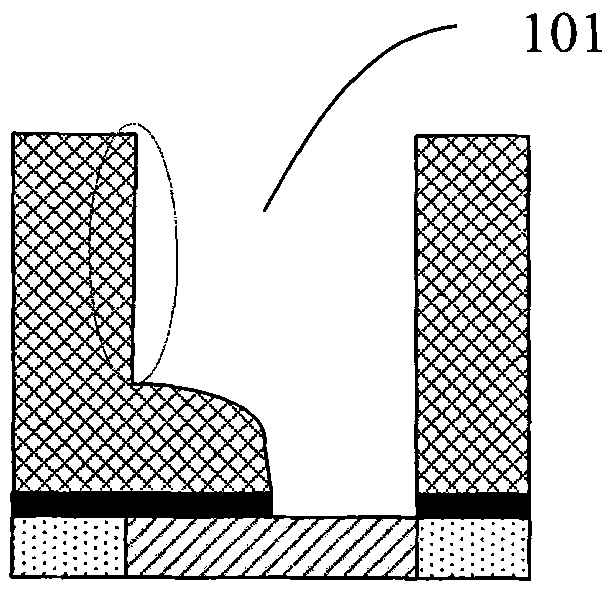

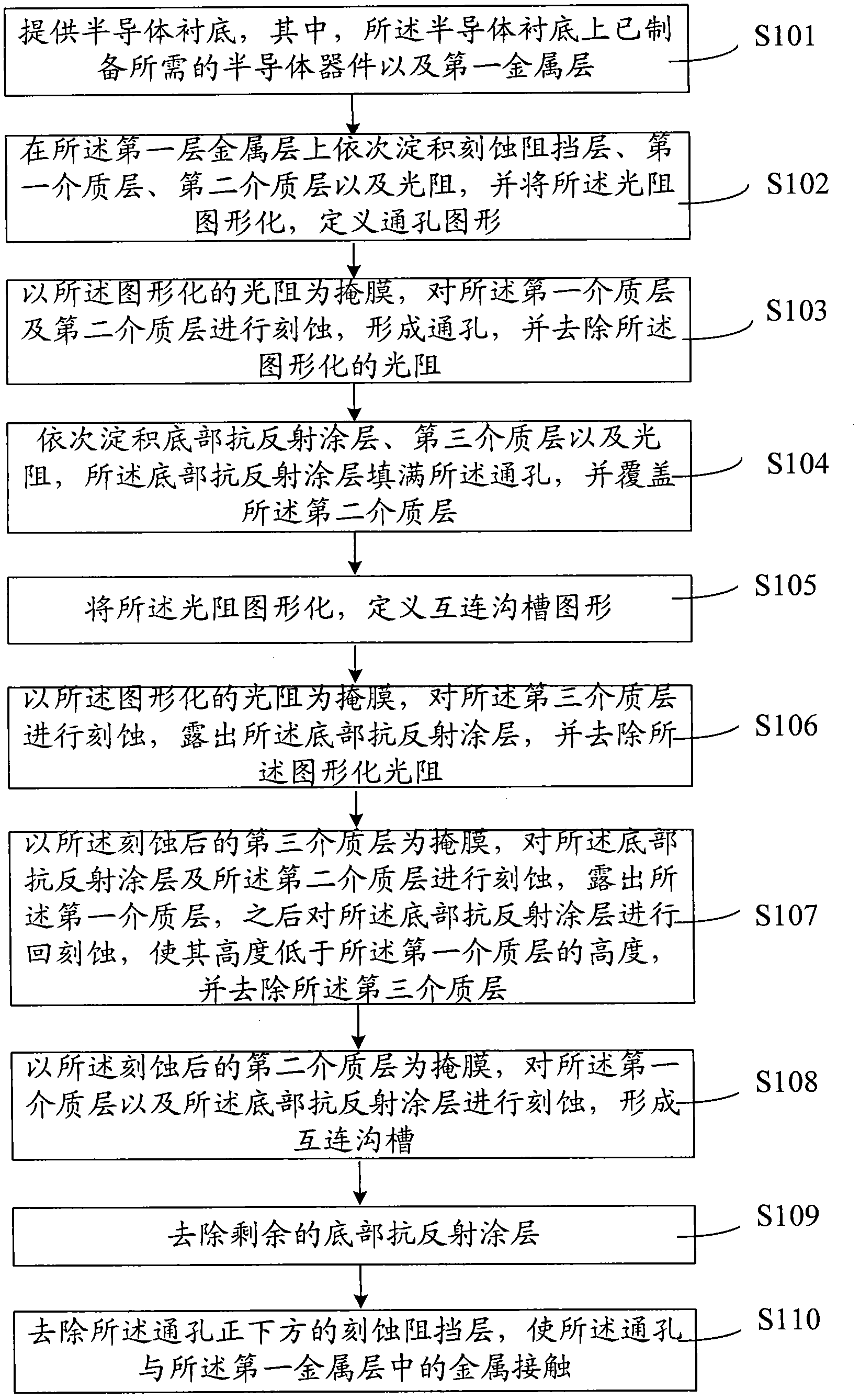

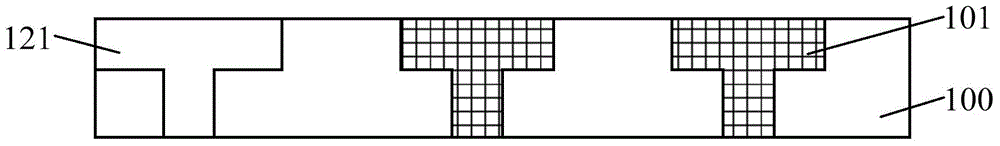

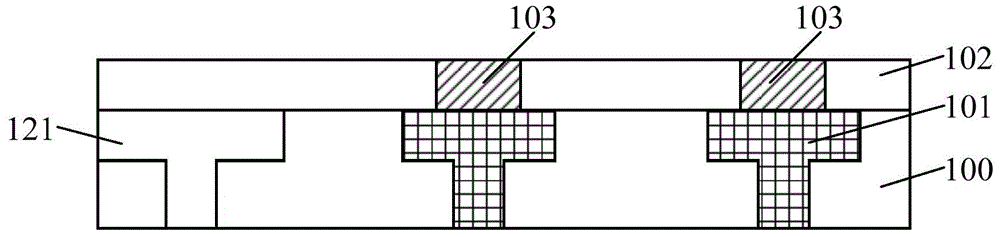

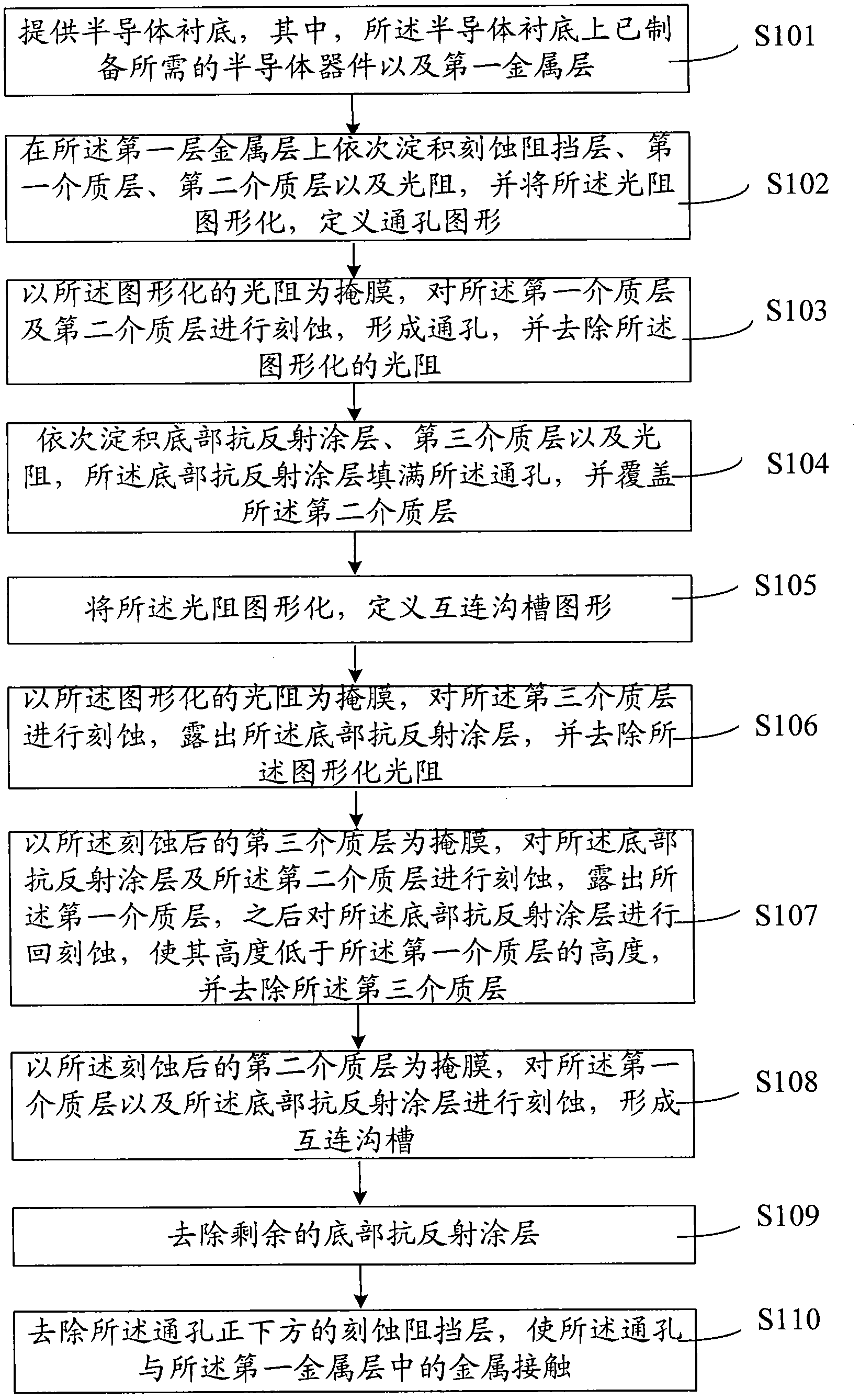

Method for producing dual damascene structure

ActiveCN102376631AEasy to achieve over-etchingShort etching timeSemiconductor/solid-state device manufacturingStructural engineeringDielectric permittivity

The invention discloses a method for producing a dual damascene structure. The method comprises the following steps of: depositing a part of silicon-containing coating in a through hole; then depositing a bottom antireflective coating; carrying out interconnected groove etching; and when the silicon-containing coating is exposed, introducing CF4, N2 and Ar and continuously etching, or introducingCF4, N2 and Ar for etching and then introducing CF4, N2, Ar and C4F8 and continuously etching. In the environment of the CF4, the N2 and the Ar, the ratio of the etching rate of the silicon-containing coating to the etching rate of a dielectric layer with a low dielectric constant can reach 1.1; in the environment of the CF4, the N2, the Ar and the C4F8, the ratio of the etching rate of the silicon-containing coating to the etching rate of the dielectric layer with the low dielectric constant can reach 3, thereby over etching of the silicon-containing coating is extremely realized when the interconnected groove etching is carried out. Therefore, the method is beneficial to enabling the top of a through hole and the bottom of the interconnected groove to form a circular corner, avoids the damage to the side of the interconnected groove and enables the interconnected groove to keep vertical.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Forming method of resistive random-access memory

ActiveCN105679932AHigh etch selectivityQuality improvementElectrical apparatusOptoelectronicsDry etching

The invention provides a forming method of a resistive random-access memory. The method comprises the steps as follows: a substrate is provided; a lower electrode layer is arranged in the substrate; the top part of the lower electrode layer is flush with the surface of the substrate; a dielectric material layer is formed on the surface of the substrate; an upper electrode layer is formed on the surface of the dielectric material layer; a hard mask layer is formed on the surface of the upper electrode layer; the hard mask layer is patterned; an opening for exposing the upper electrode layer is formed in the hard mark layer; with the hard mask layer with the opening as a mask, the upper electrode layer and the dielectric material layer are sequentially etched by a dry etching process until the surface of the substrate is exposed; an etching gas for the dry etching process is H2; the hard mask layer with the opening is removed. The etching pollution to the upper electrode layer and the dielectric material layer caused by the etching process is avoided; and the side wall of the etched upper electrode layer and the side wall of the dielectric material layer are clean, so that the electrical properties of the formed resistive random-access memory are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

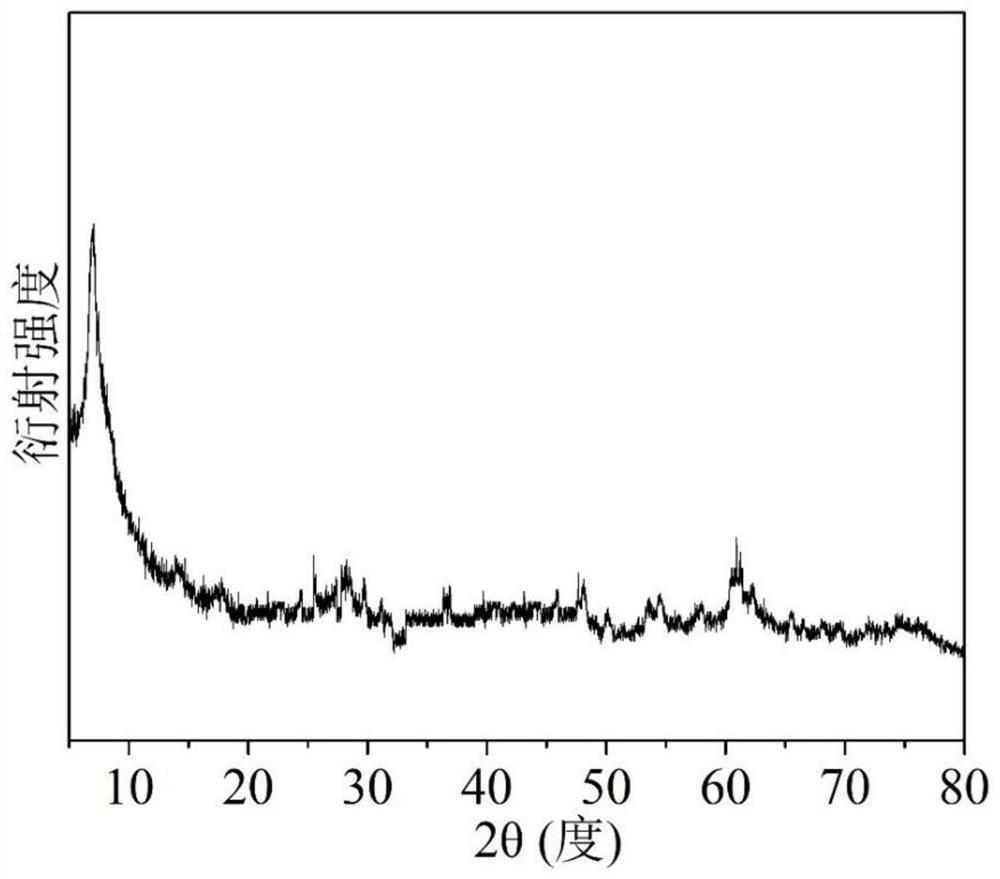

Method for preparing fluoride-free MXene by adopting electrochemical etching method

ActiveCN113461010AShort etching timeCarbon compoundsHybrid capacitor electrodesCapacitanceFreeze-drying

The invention discloses a method for preparing fluorine-free MXene by adopting an electrochemical etching method, the method comprises the following steps: immersing two MAX blocks serving as a working electrode and a counter electrode into a mixed aqueous solution of hydroxide and chloride respectively, applying voltage, and stirring; collecting black precipitates in the solution through centrifugal washing, and then carrying out ultrasonic treatment under ice-water bath and inert gas protection conditions; and centrifuging and washing for multiple times until the supernatant becomes black, and then freeze-drying the black supernatant to obtain few-layer or single-layer MXene. The obtained MXene, the nanocellulose and the carbon nanofiber are subjected to suction filtration to form a film, and the specific capacitance can reach 249.9 F / g, which is obviously superior to that of a contrast sample obtained by etching a fluorine-containing reagent.

Owner:NANJING FORESTRY UNIV

Method of fabricating pixel electrode in liquid crystal display

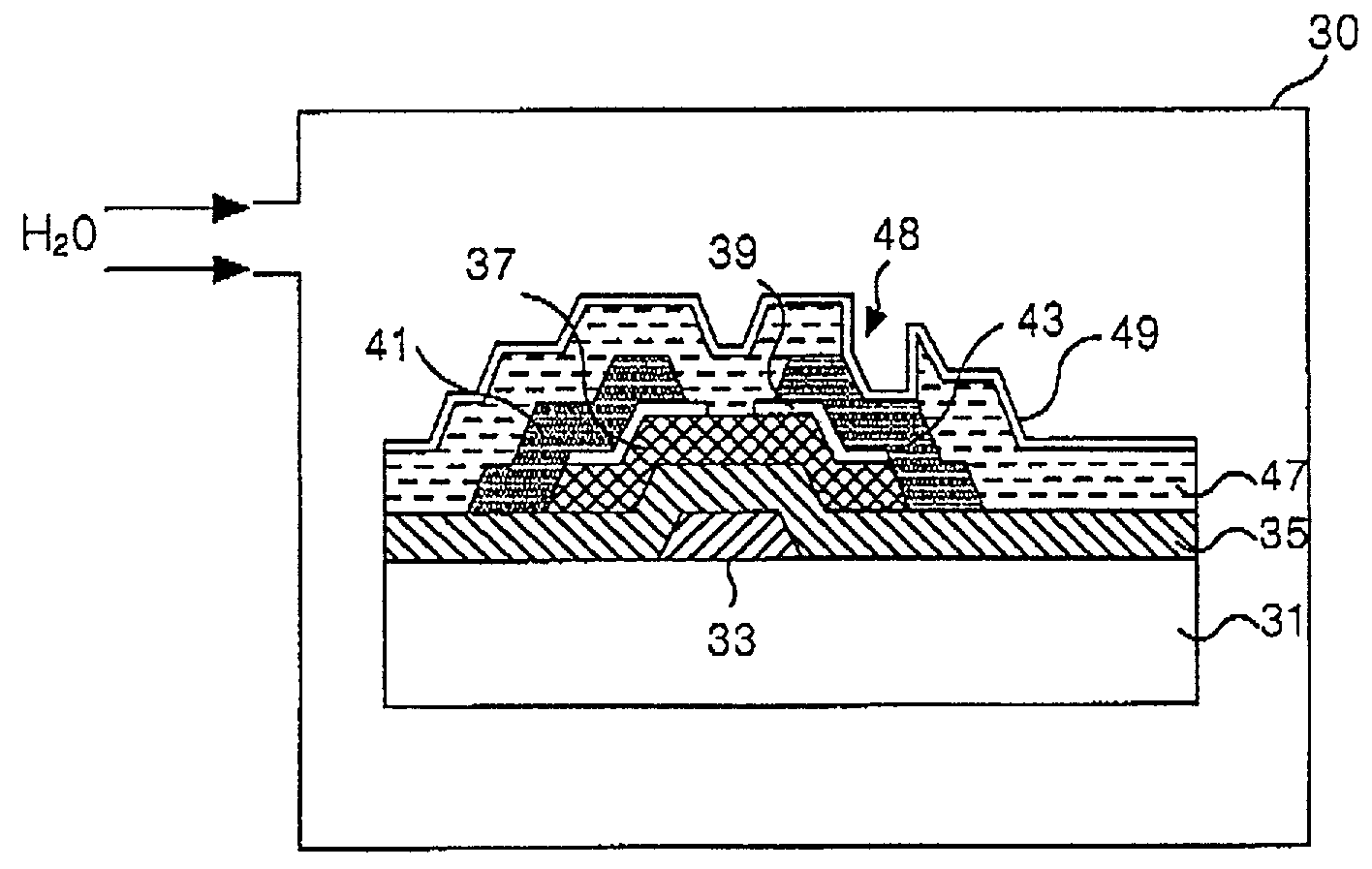

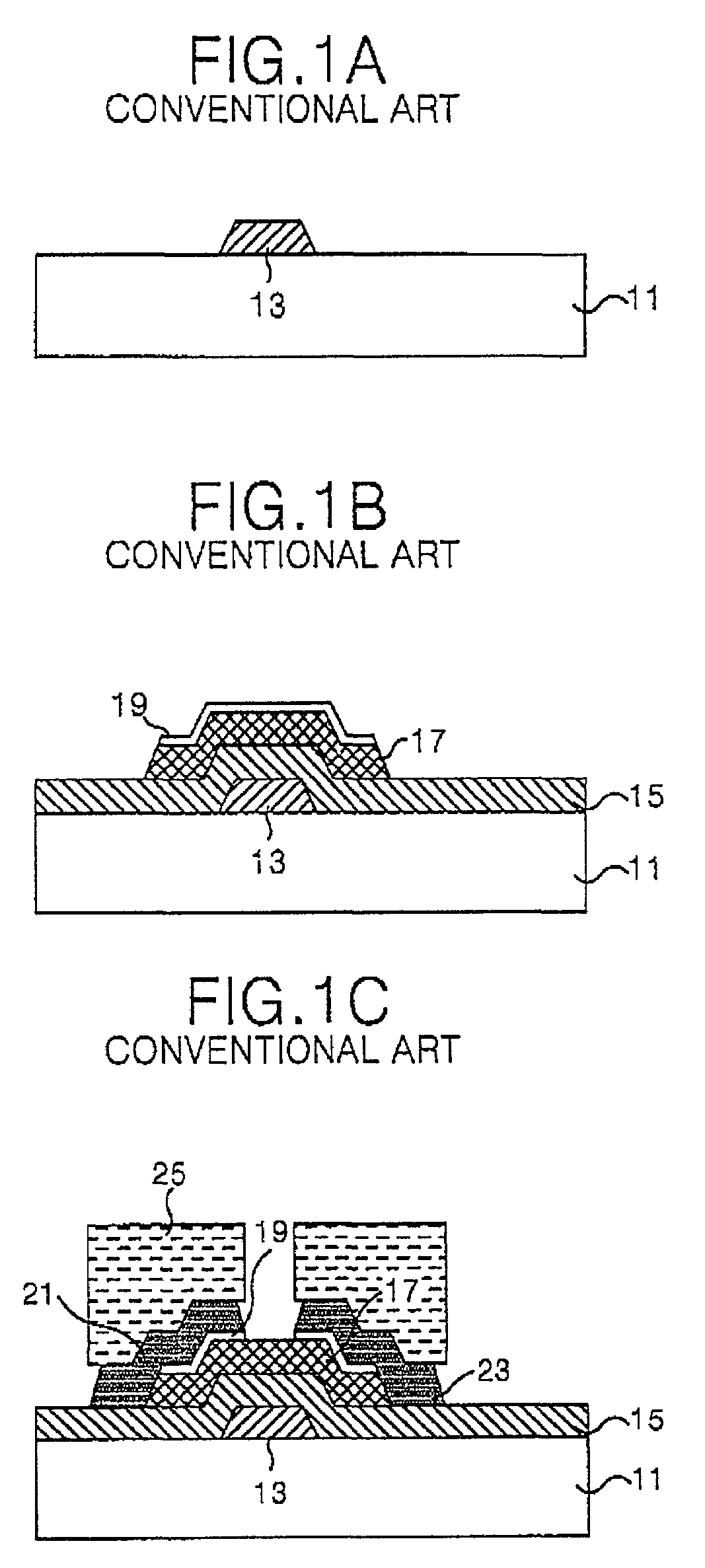

InactiveUS7158203B2Avoid damageShort etching timeNon-linear opticsTectorial membraneLiquid-crystal display

A method of fabricating a pixel electrode of a liquid crystal display uses an etchant that has low damage to metals to thereby enhance yields. In the method, a protective film covers a switching device, and a contact hole is defined at the protective film in such a manner to expose one electrode of the switching device. The pixel electrode, connected via the contact hole to the one electrode of the switching device, is formed on the protective film by using a low-temperature process in which a Hydrogen-containing gas is injected within a vacuum chamber. Accordingly, the etching process time can be shortened and damage to the metal can be virtually eliminated.

Owner:LG DISPLAY CO LTD

Method of forming a transistor

ActiveCN105097510BAvoid damageImprove performanceSemiconductor/solid-state device manufacturingOptoelectronicsDielectric layer

Owner:SEMICON MFG SOUTH CHINA CORP

Method for producing dual damascene structure

ActiveCN102376631BEasy to achieve over-etchingShort etching timeSemiconductor/solid-state device manufacturingStructural engineeringDielectric permittivity

The invention discloses a method for producing a dual damascene structure. The method comprises the following steps of: depositing a part of silicon-containing coating in a through hole; then depositing a bottom antireflective coating; carrying out interconnected groove etching; and when the silicon-containing coating is exposed, introducing CF4, N2 and Ar and continuously etching, or introducingCF4, N2 and Ar for etching and then introducing CF4, N2, Ar and C4F8 and continuously etching. In the environment of the CF4, the N2 and the Ar, the ratio of the etching rate of the silicon-containing coating to the etching rate of a dielectric layer with a low dielectric constant can reach 1.1; in the environment of the CF4, the N2, the Ar and the C4F8, the ratio of the etching rate of the silicon-containing coating to the etching rate of the dielectric layer with the low dielectric constant can reach 3, thereby over etching of the silicon-containing coating is extremely realized when the interconnected groove etching is carried out. Therefore, the method is beneficial to enabling the top of a through hole and the bottom of the interconnected groove to form a circular corner, avoids the damage to the side of the interconnected groove and enables the interconnected groove to keep vertical.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

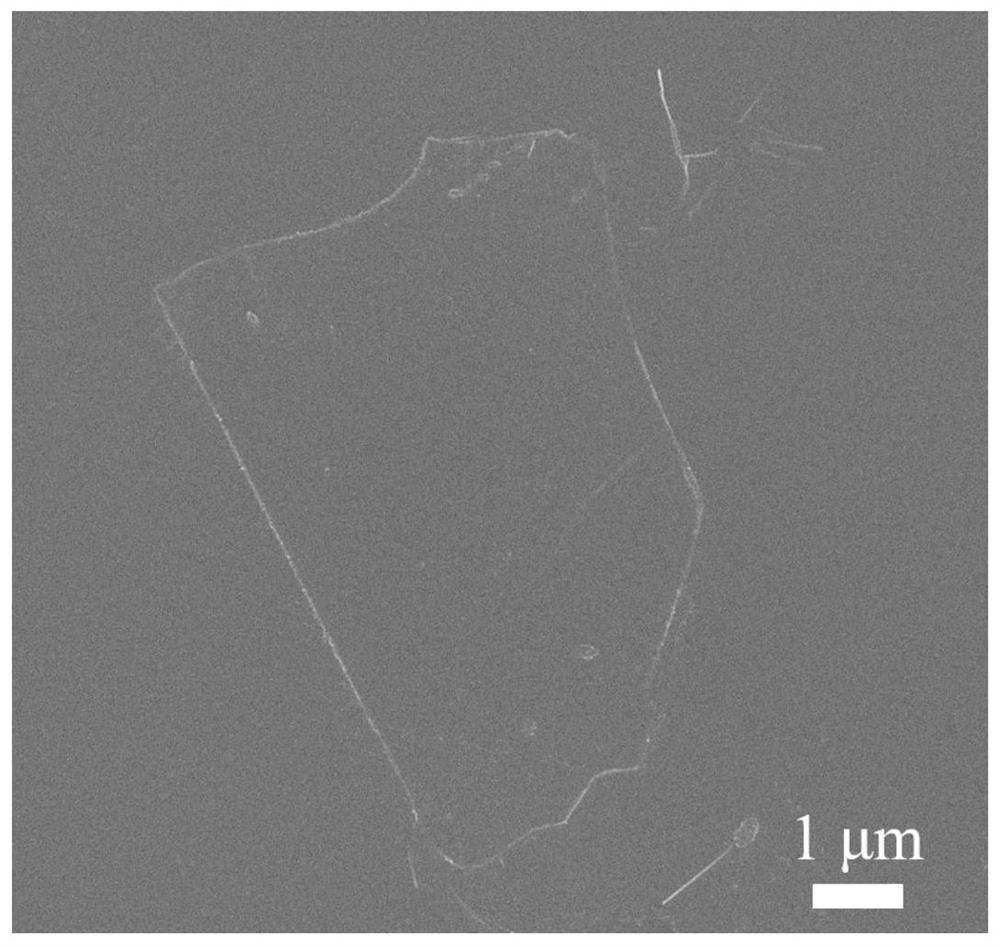

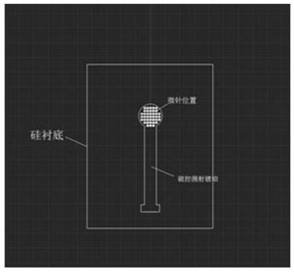

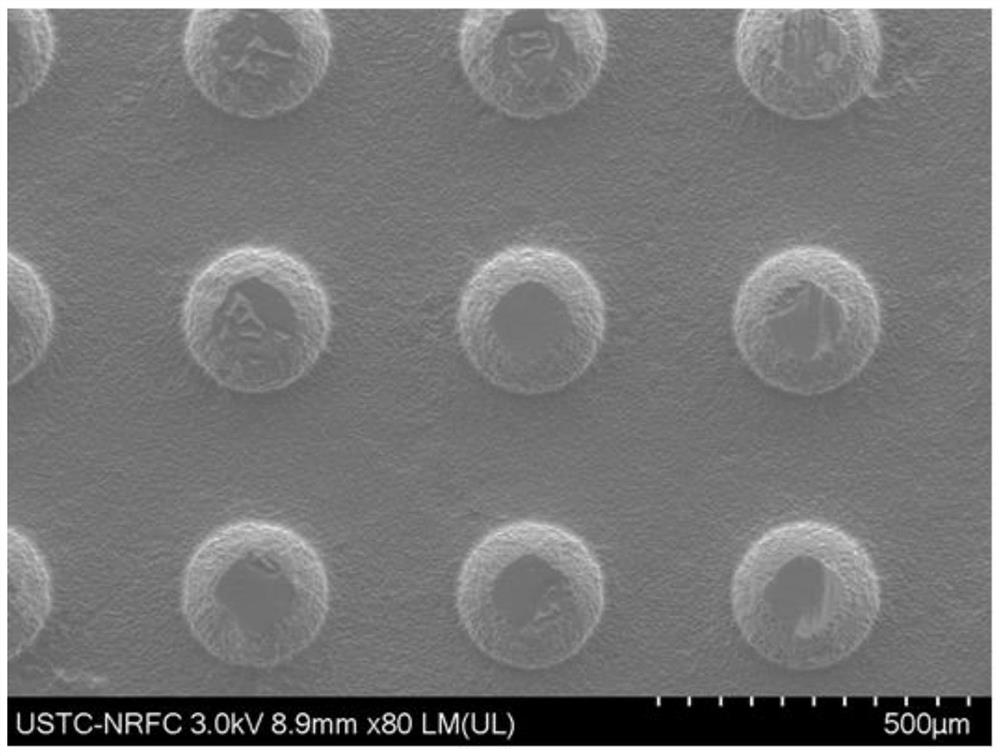

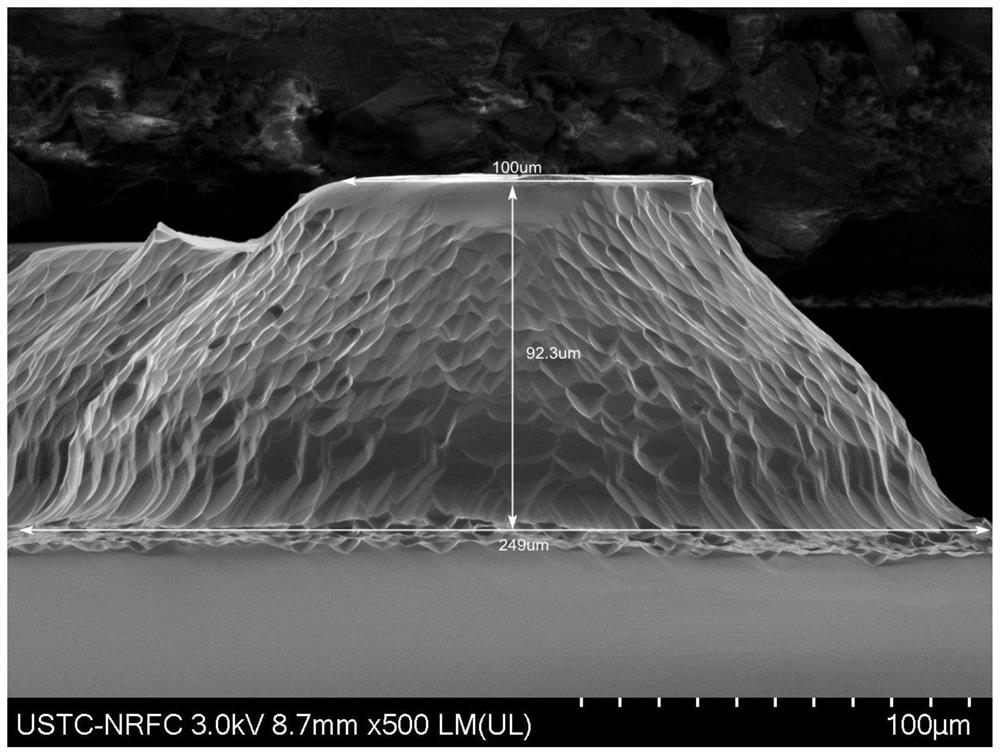

A preparation method and application of silicon-based microneedles by metal-assisted wet etching

ActiveCN112221010BHighly easy to controlGood linear responseMicroneedlesMedical devicesEtchingHybrid solution

The present invention provides a preparation method to prepare silicon -based microneedles with metal auxiliary wet etching, including: the pre -processing silicon wafer surface is applied to the graphic processing to obtain the sample;Fluoric acid 纯 ultra -pure water hybrid solution is deposited to obtain sedimentary silicon wafers; the sedimentary silicon wafers are carved in the hydrogen hydrogen peroxide hydrogen peroxide mixed solution, soaked in the ingredients solution after washing, and then removed the silicon nano wire., Get the silicon -based microneedle.The method provided by the present invention only needs to be treated with a simple map with photoresist, and then the metal auxiliary wetting method is used to etched out large -sized microcliclement under acidic conditions.The etching time is short, the process is simple, and the effect is significant.The height of the silicon -based microneedle is 90 to 137 microns; the prepared sensors have a good linear response to hydrogen peroxide, and the response current is large. It can detect changes in the concentration of hydrogen peroxide at no less than 4 hours.

Owner:UNIV OF SCI & TECH OF CHINA

How the transistor is formed

ActiveCN104253047BThe process steps are simpleShort etching timeSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention relates to a forming method of a transistor. The forming method of the transistor includes the following steps that: a semiconductor substrate is provided, wherein the semiconductor substrate includes a first region and a second region; a dummy gate dielectric material layer is formed on the surface of the semiconductor substrate, wherein the dummy gate dielectric material layer includes a first insulating material layer and a second insulating material layer; a dummy gate and a second gate are formed; the dummy gate dielectric material layer is etched with the dummy gate and the second gate adopted as a mask, so that a dummy gate dielectric layer and a second gate dielectric layer are formed; first source / drain areas are formed in the first region, and second source / drain areas are formed in the second region; a dielectric layer is formed on the surface of the semiconductor substrate, and the surface of the dielectric layer is flush with the surface of the dummy gate; and the second insulating material layer in the dummy gate dielectric material layer is removed through adopting a dry etching process, and the first insulating material layer in the dummy gate dielectric material layer is removed through adopting a wet etching process, and therefore, a groove can be formed; and a first gate structure is formed in the groove. With the forming method of the transistor adopted, steps can be decreased, and the performance of the transistor can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

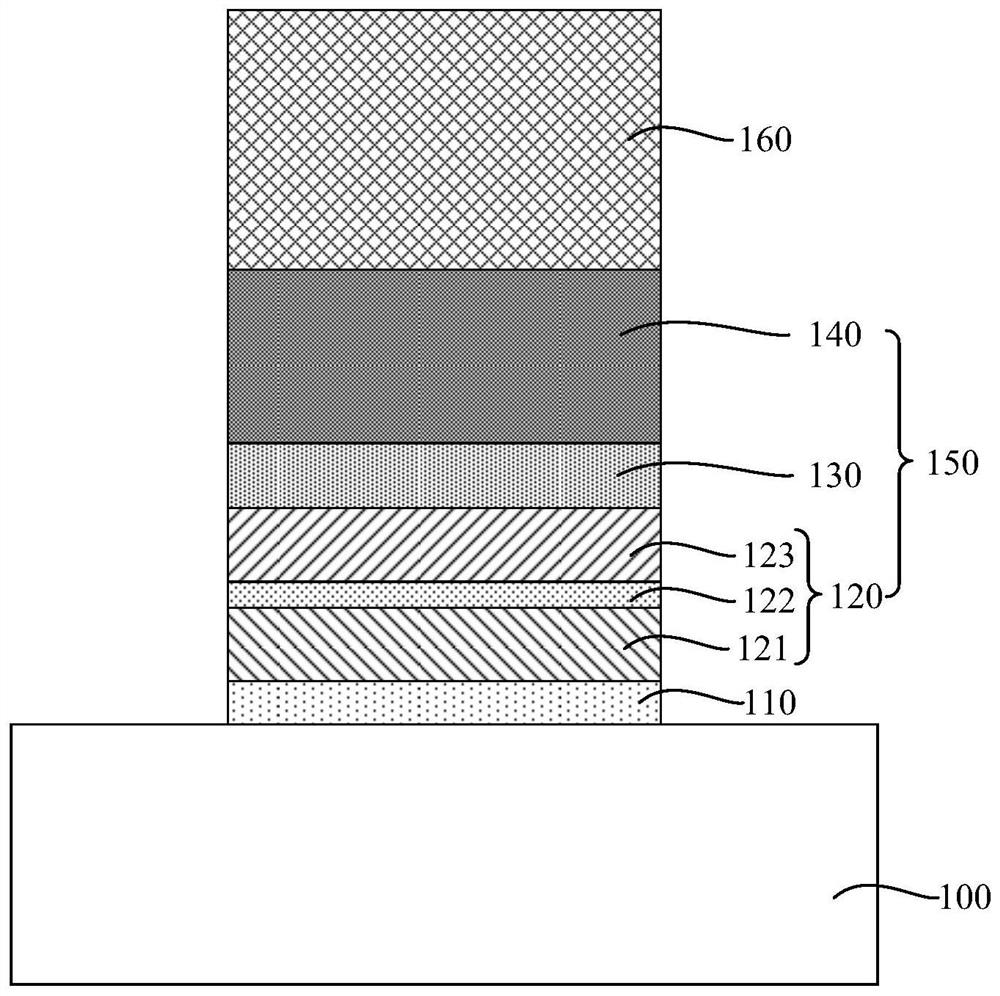

Semiconductor structure and manufacturing method of semiconductor structure

PendingCN114530493AExcellent electrical performanceGuaranteed yieldSemiconductor/solid-state device manufacturingSemiconductor devicesElectrically conductivePolycrystalline silicon

The embodiment of the invention provides a semiconductor structure and a manufacturing method of the semiconductor structure. The semiconductor structure comprises a substrate; the gate structure is located on the substrate and comprises a first conductive layer, a barrier layer and a second conductive layer which are stacked in sequence; wherein the first conductive layer comprises a first polycrystalline silicon layer, a first metal layer and a second polycrystalline silicon layer, the first polycrystalline silicon layer is close to the substrate, and the second polycrystalline silicon layer is tightly attached to the barrier layer; the first metal layer is located between the first polycrystalline silicon layer and the second polycrystalline silicon layer. The gate structure provided by the embodiment of the invention has a vertical morphology and relatively strong electrical performance.

Owner:CHANGXIN MEMORY TECH INC