Method for producing dual damascene structure

A dielectric layer and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that double damascus cannot meet the requirements of forming round corners of through holes and vertical sides of interconnection trenches at the same time. The effect of short eclipse time and avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

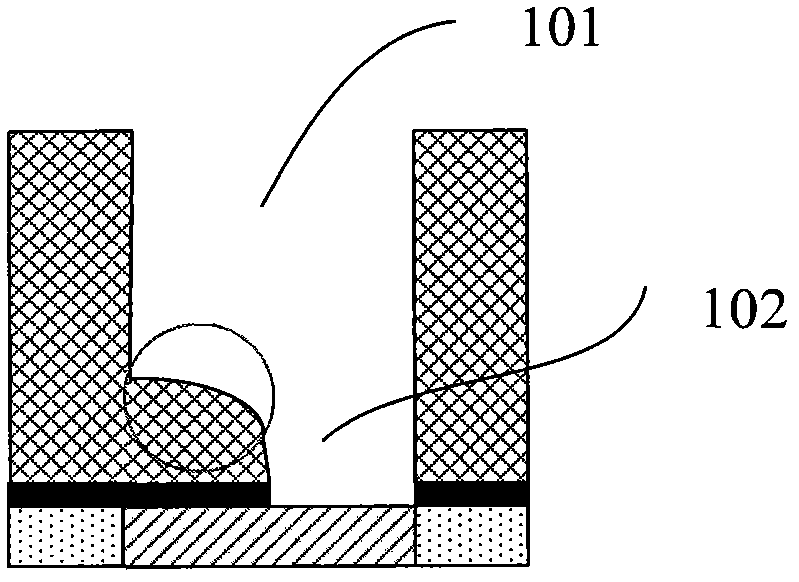

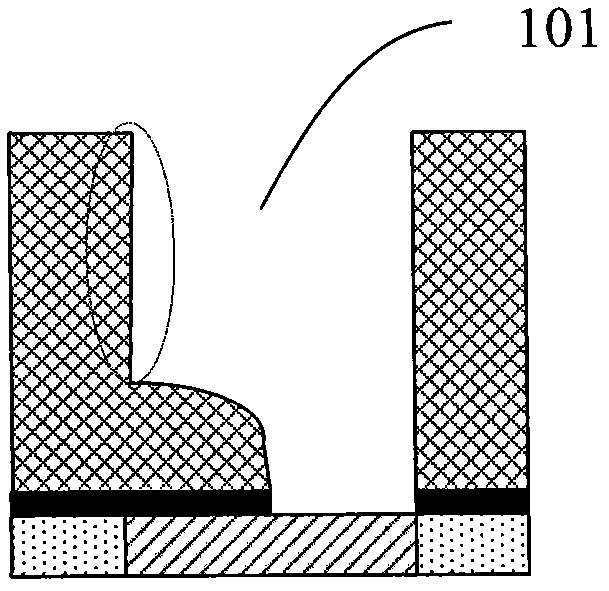

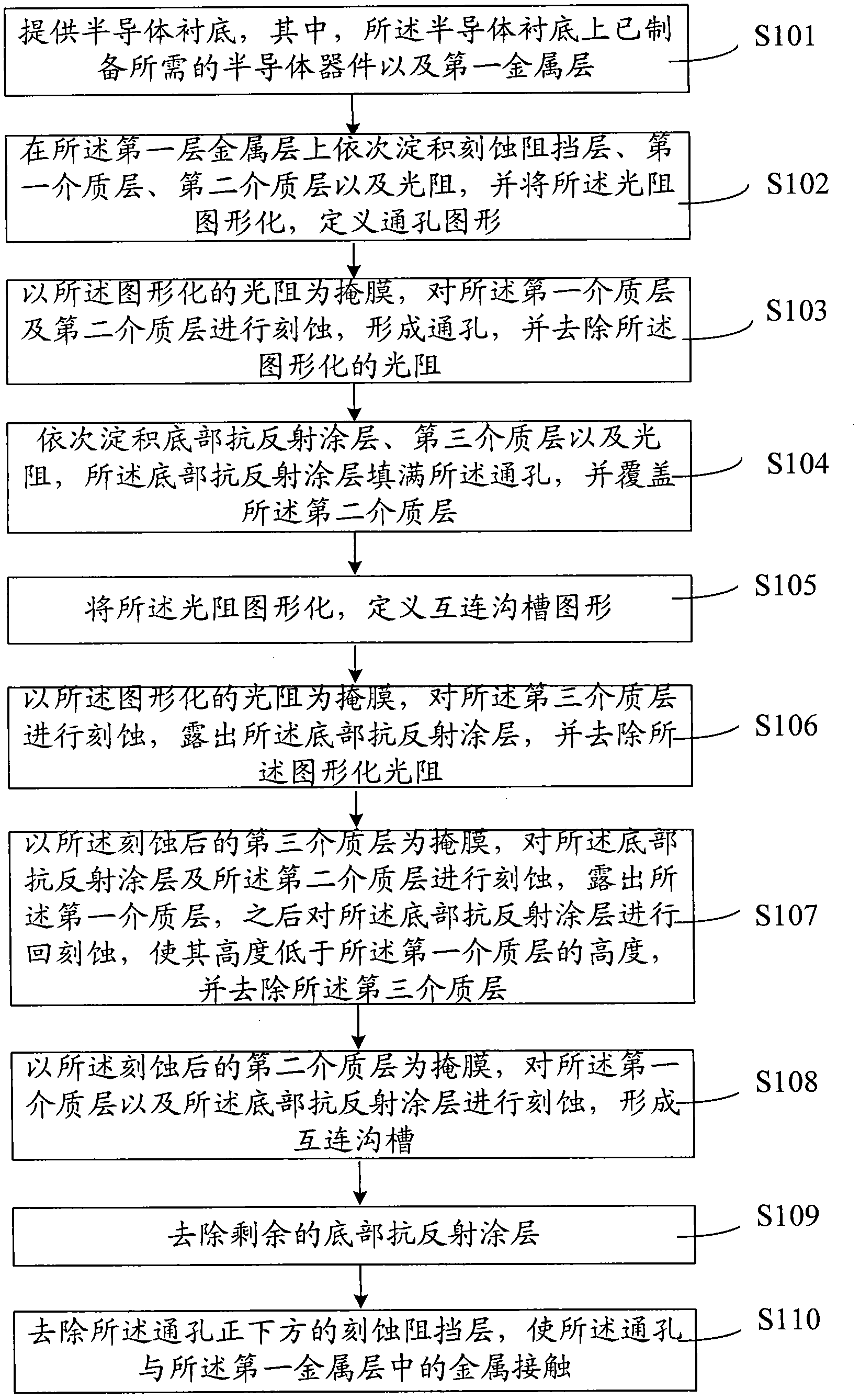

[0076] Please refer to Figure 6 ,as well as Figure 7A to Figure 7J ,in, Figure 6 The flow chart of the method steps for preparing the double damascene structure provided by the embodiment of the present invention, Figure 7A to Figure 7J The schematic diagram of the cross-sectional structure of the device corresponding to each step in the method for preparing the double damascene structure provided by the embodiment of the present invention, as shown in Figure 6 as well as Figure 7A to Figure 7J As shown, the method for preparing a double damascene structure provided by the embodiments of the present invention includes the following steps:

[0077]S301. Provide a semiconductor substrate 301, wherein the required semiconductor device and the first metal layer have been prepared on the semiconductor substrate 301; specifically, the first metal layer includes an inter-metal dielectric layer (IMD, Inter-Metal Dielectric) 302 and the metal 303 in the intermetal dielectric ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More